Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1112results about "Instrumental components" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

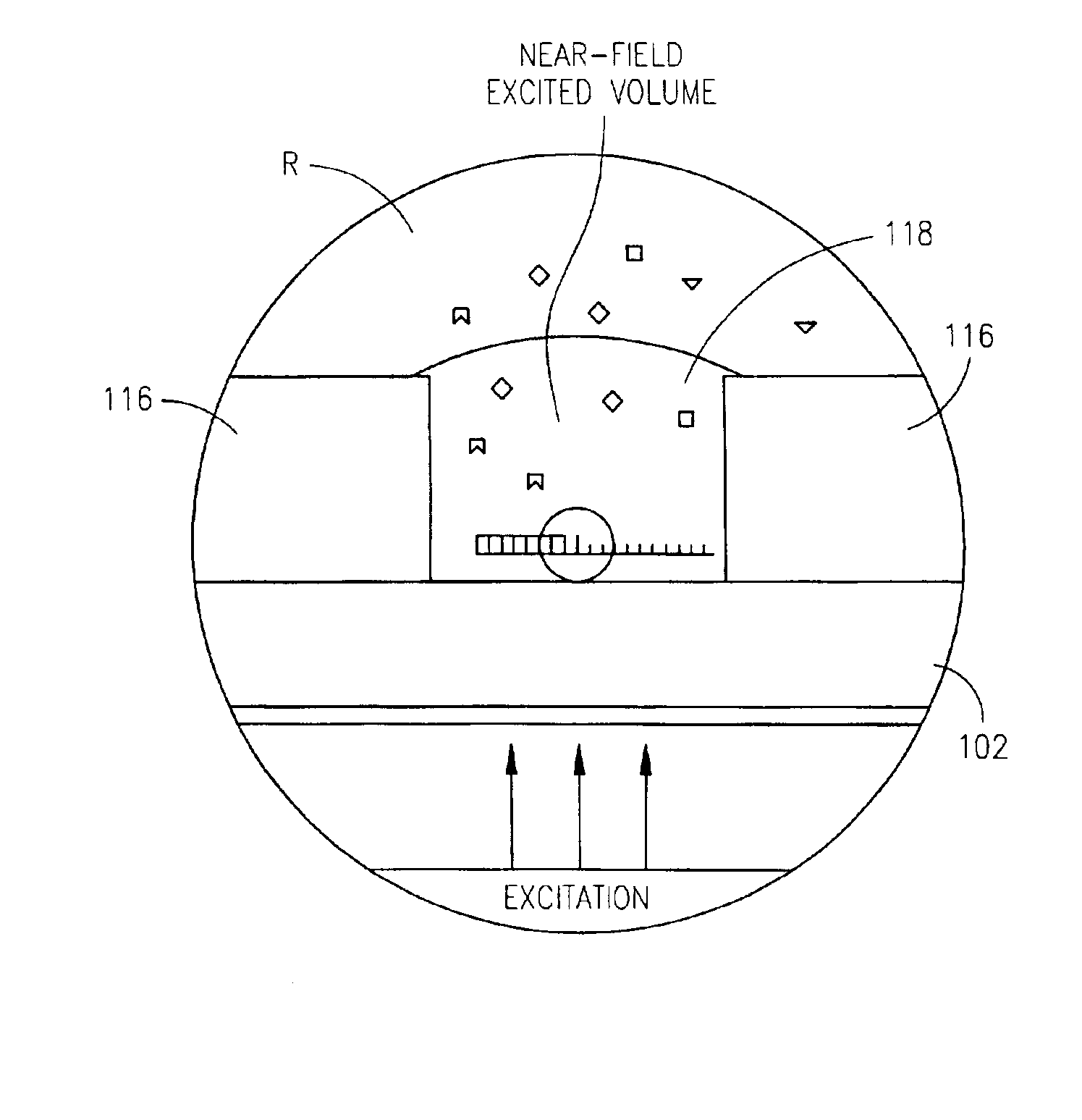

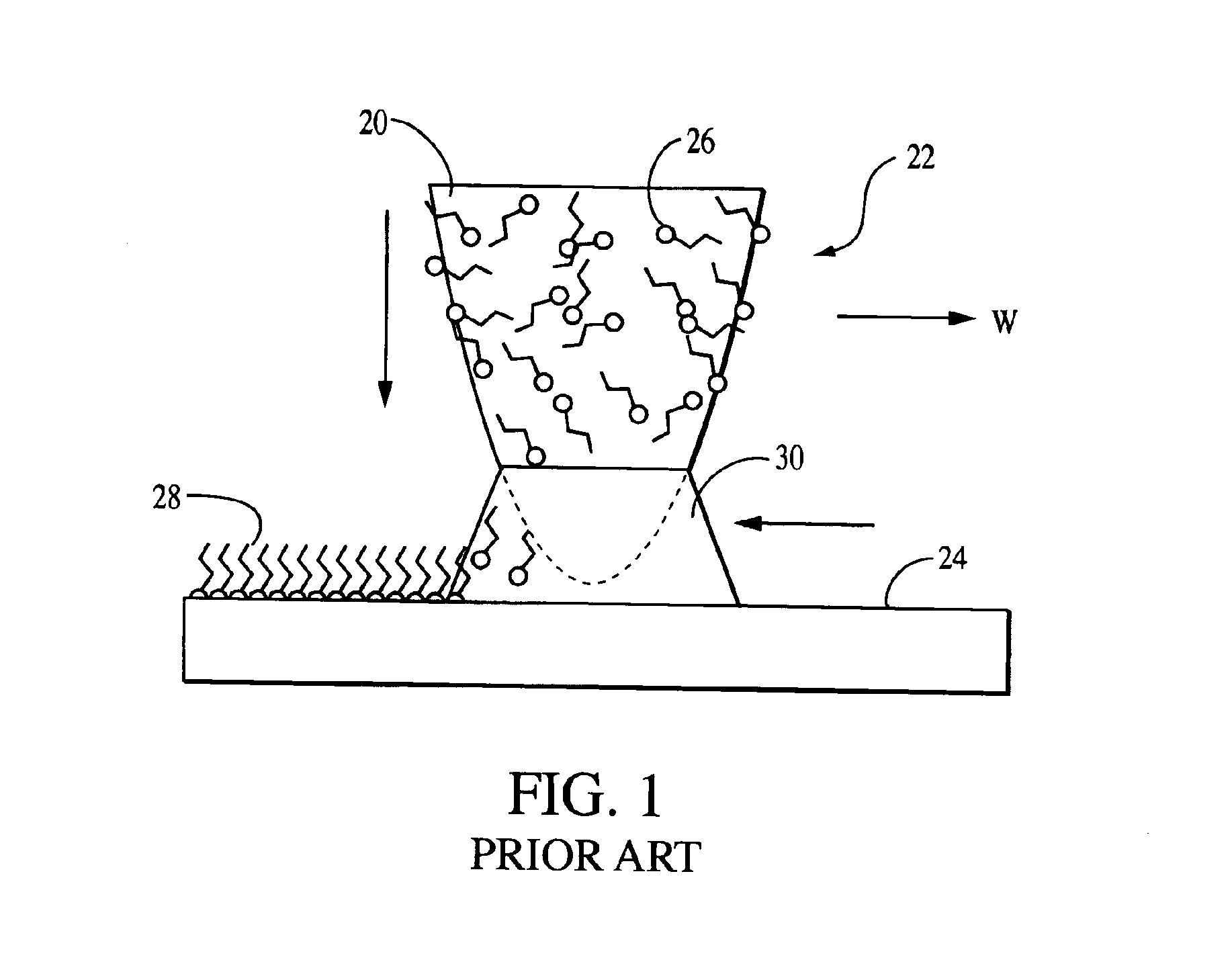

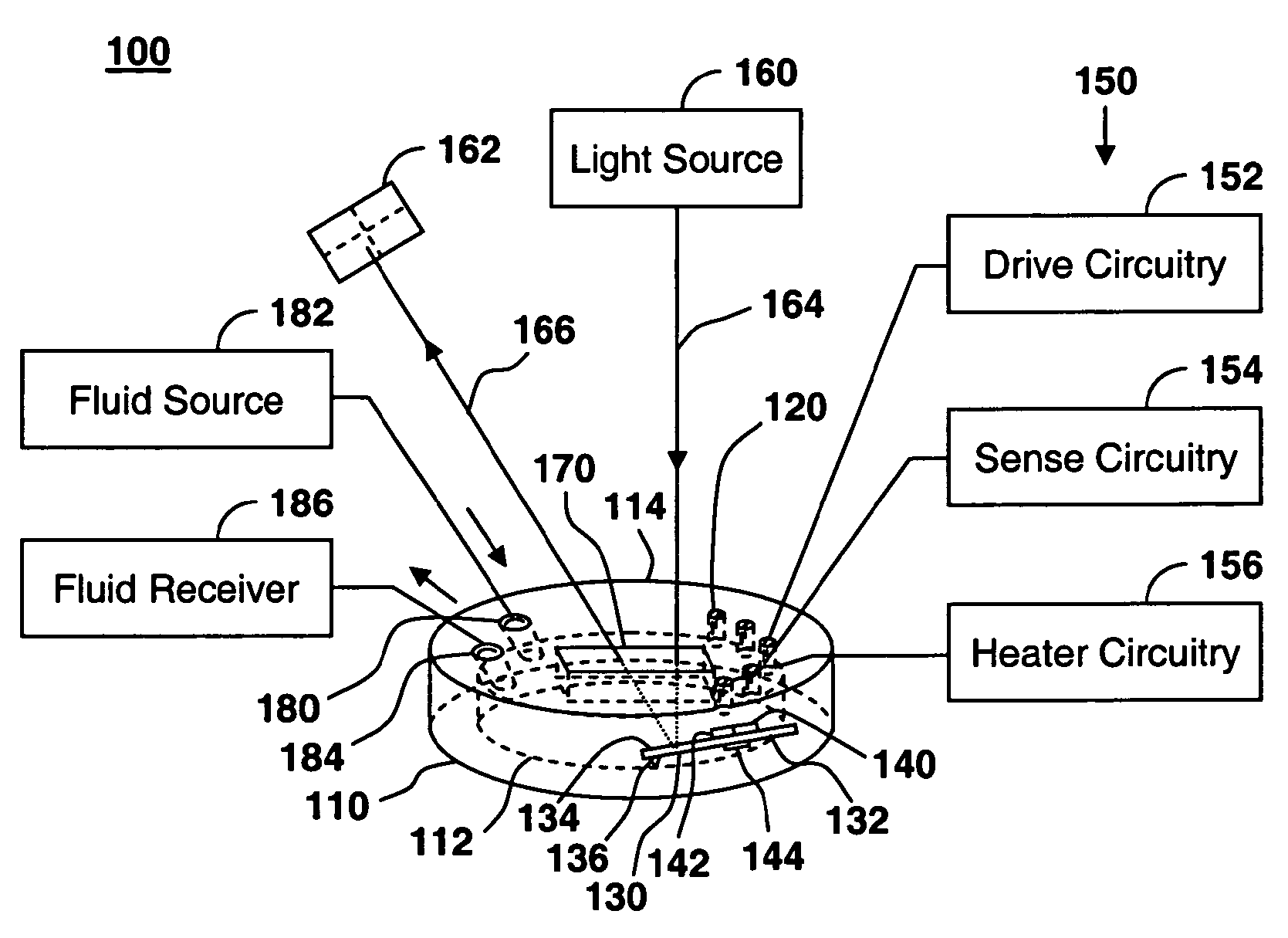

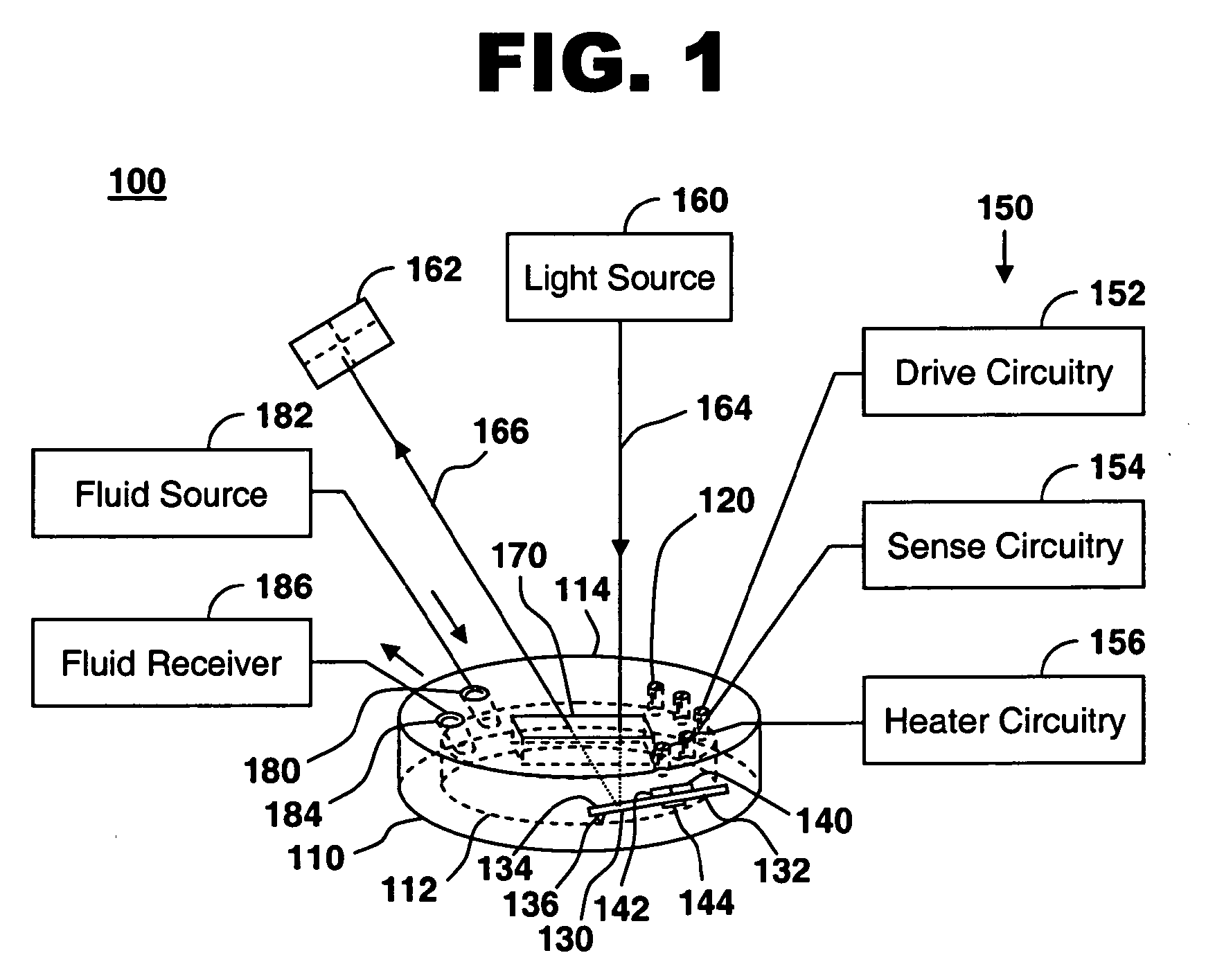

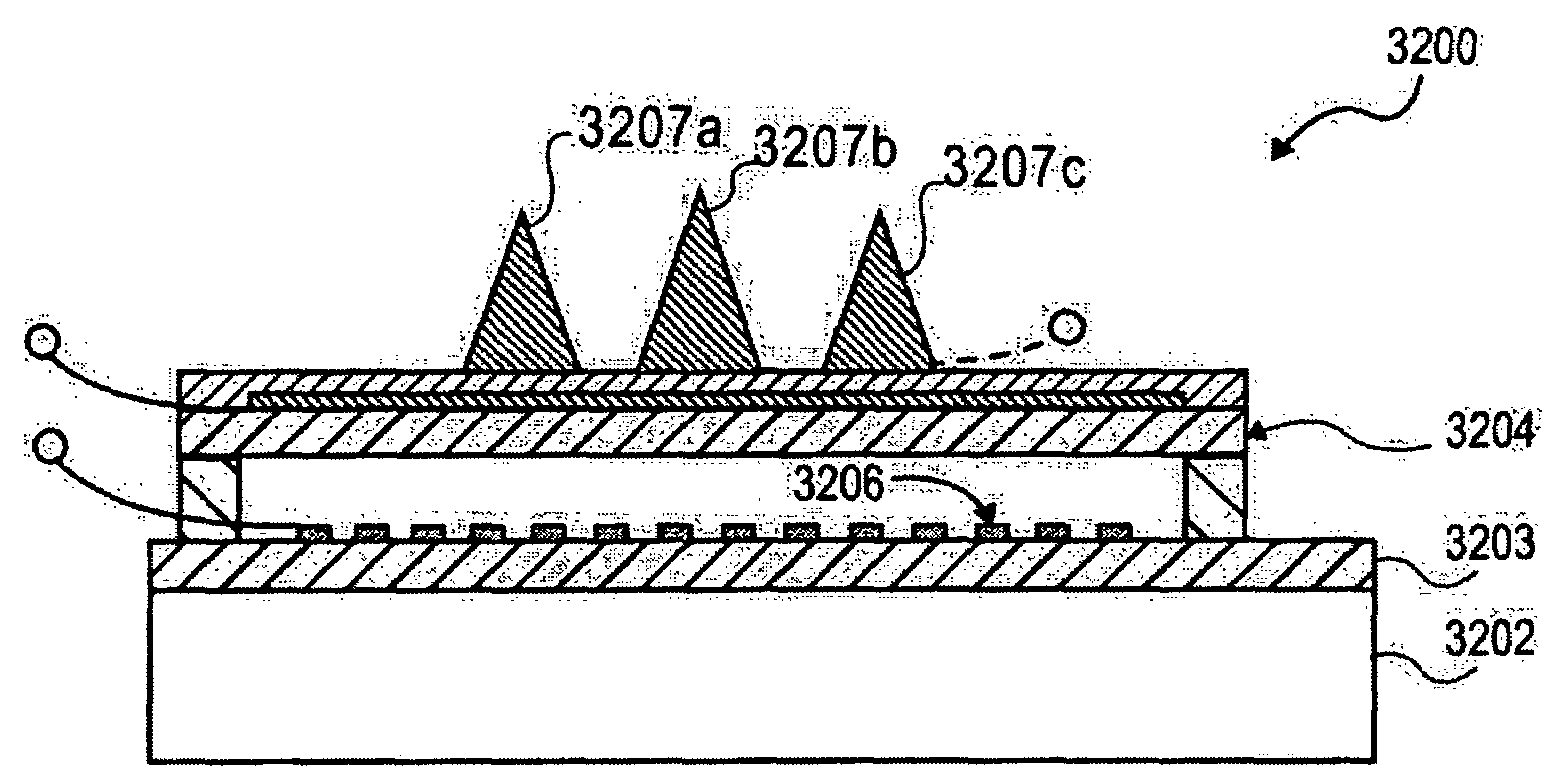

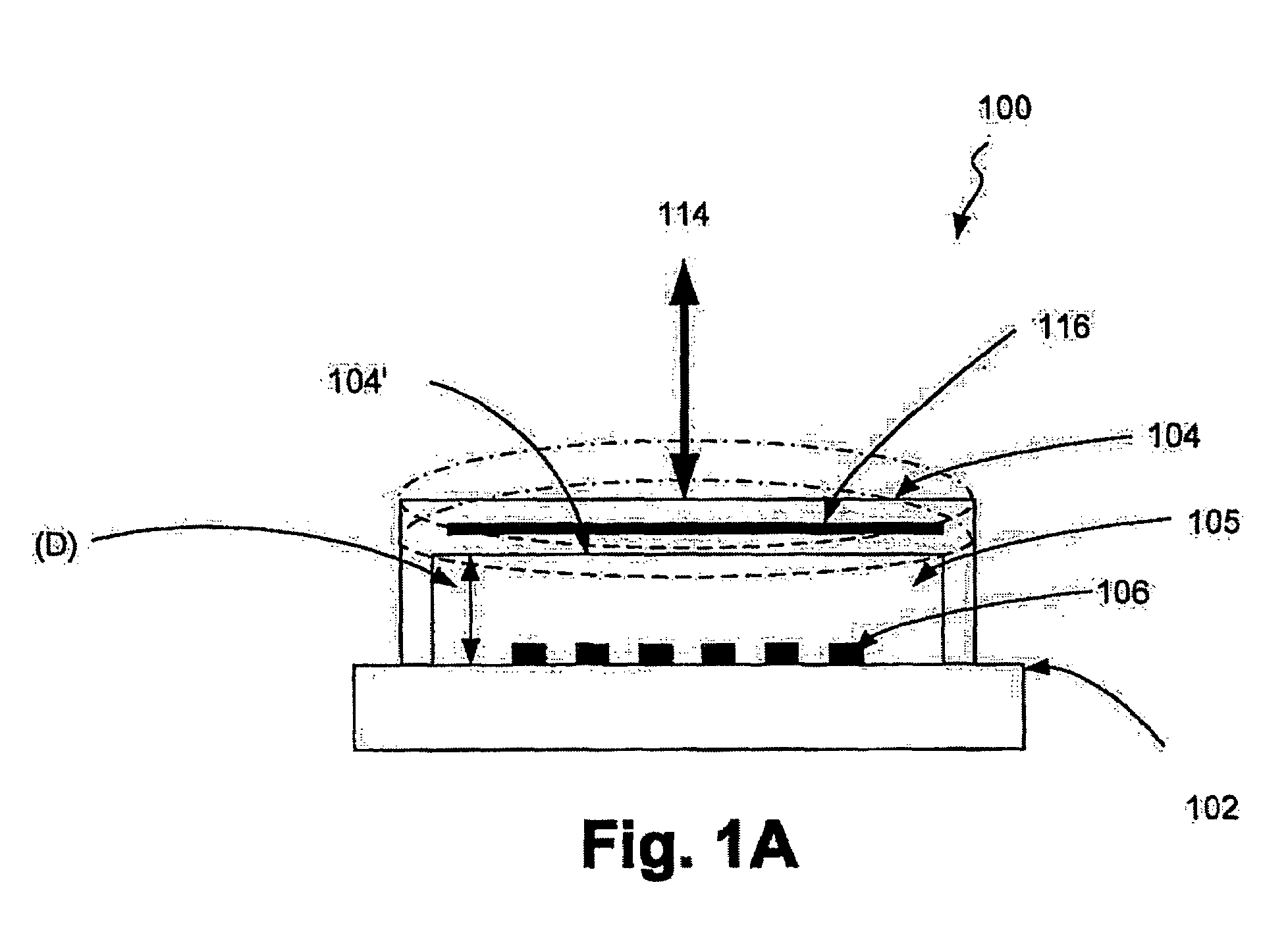

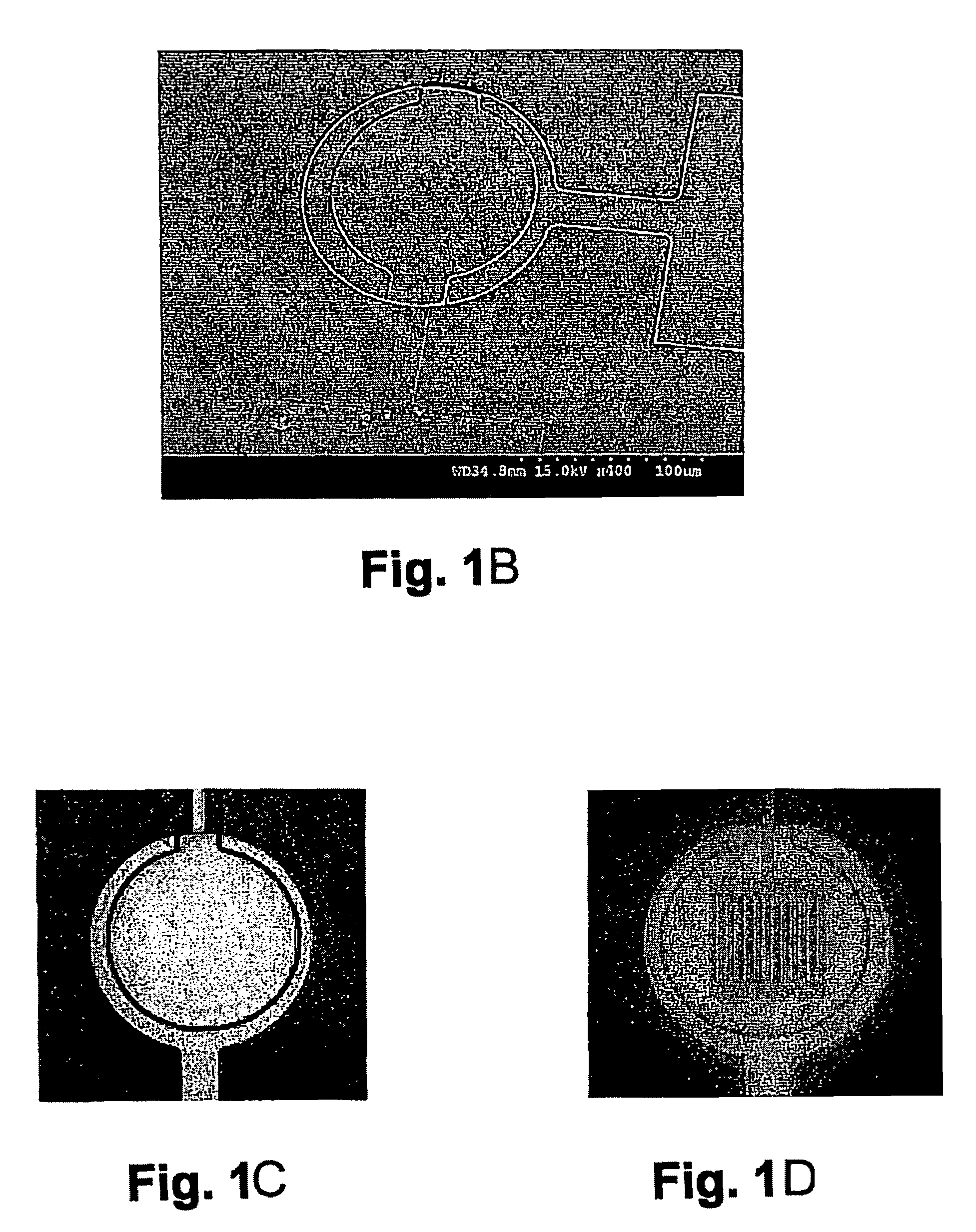

Zero-mode clad waveguides for performing spectroscopy with confined effective observation volumes

InactiveUS6917726B2Effective volumeEasy to useMicrobiological testing/measurementBiological material analysisAnalyteSpectroscopy

The present invention is directed to a method and an apparatus for analysis of an analyte. The method involves providing a zero-mode waveguide which includes a cladding surrounding a core where the cladding is configured to preclude propagation of electromagnetic energy of a frequency less than a cutoff frequency longitudinally through the core of the zero-mode waveguide. The analyte is positioned in the core of the zero-mode waveguide and is then subjected, in the core of the zero-mode waveguide, to activating electromagnetic radiation of a frequency less than the cut-off frequency under conditions effective to permit analysis of the analyte in an effective observation volume which is more compact than if the analysis were carried out in the absence of the zero-mode waveguide.

Owner:CORNELL RES FOUNDATION INC

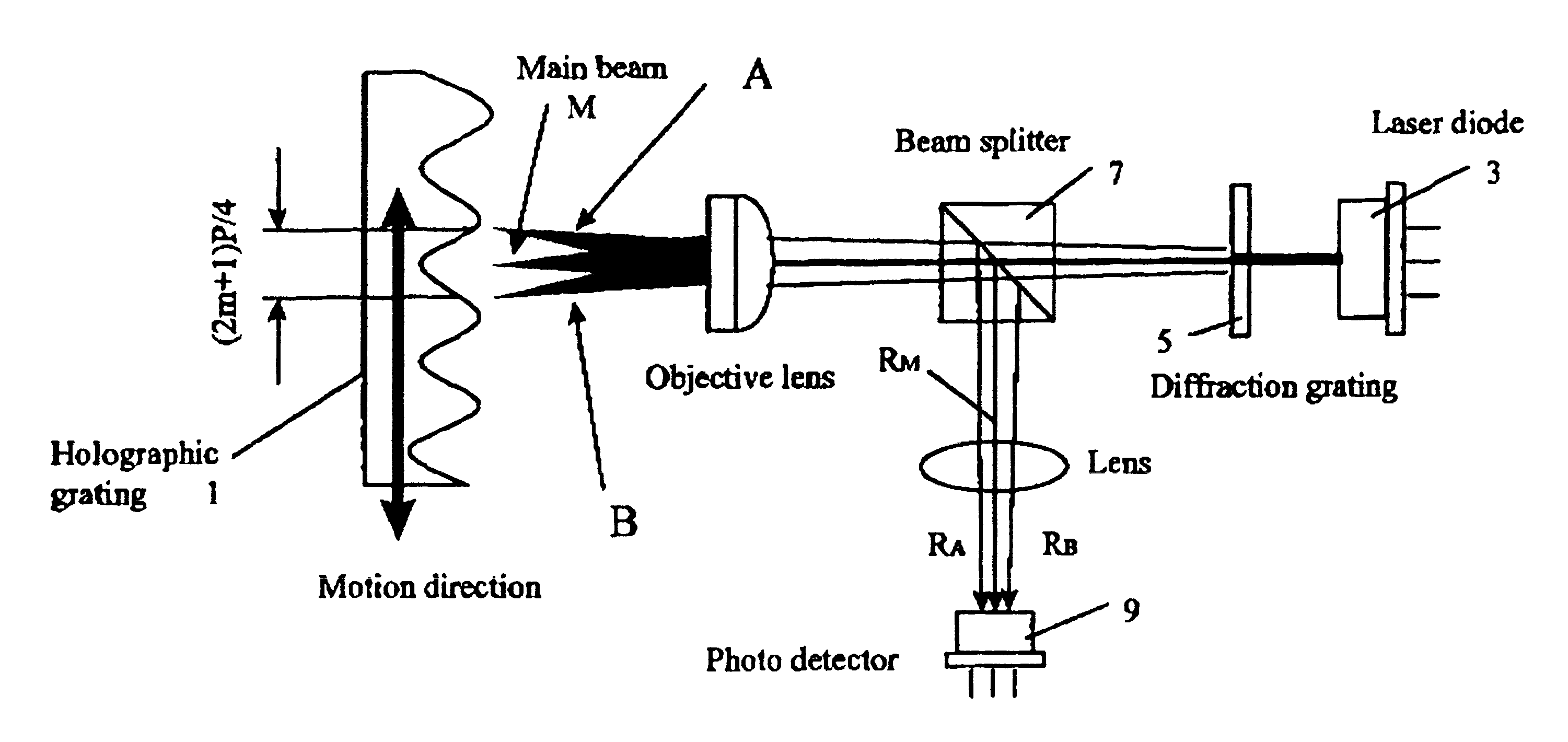

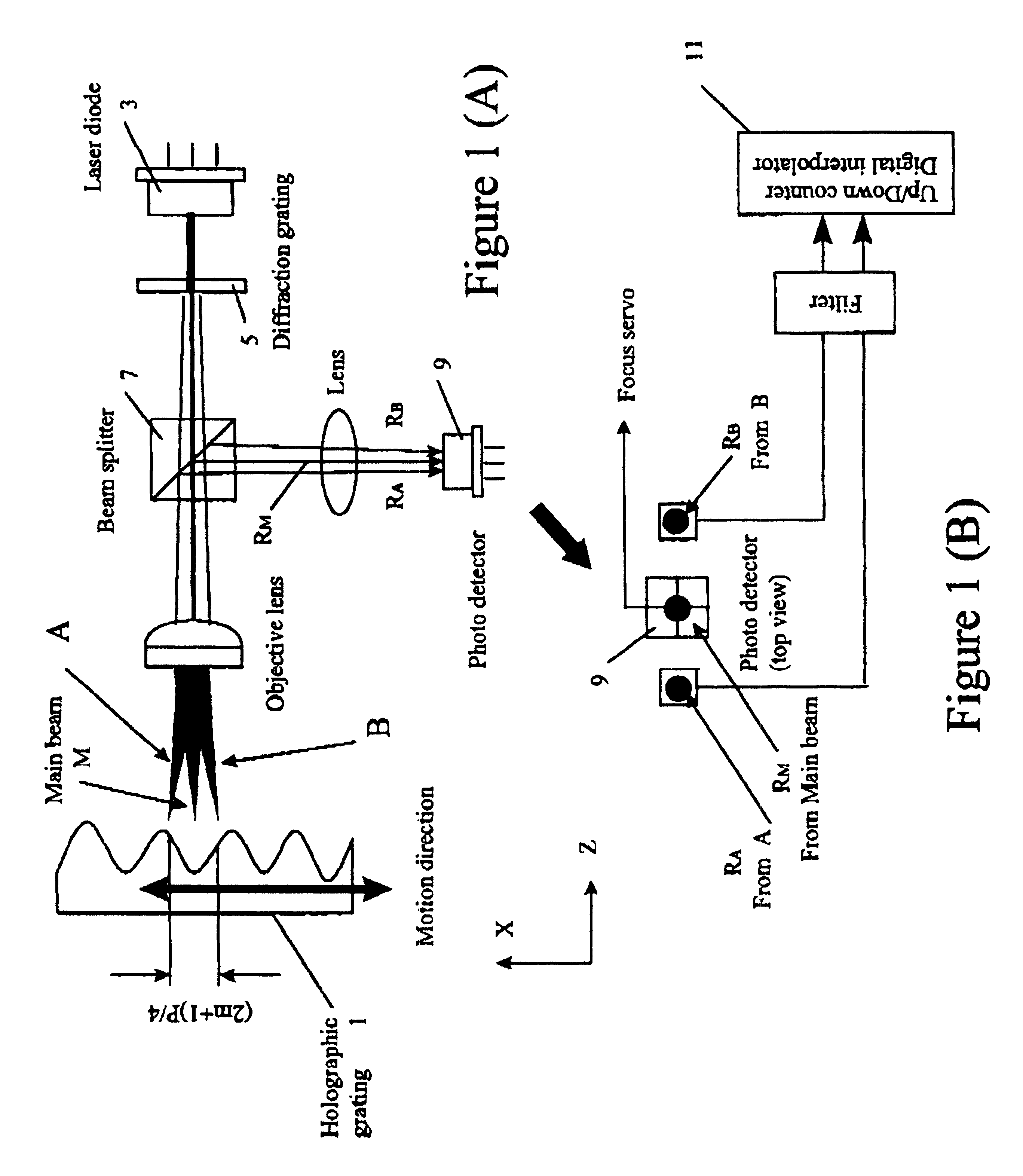

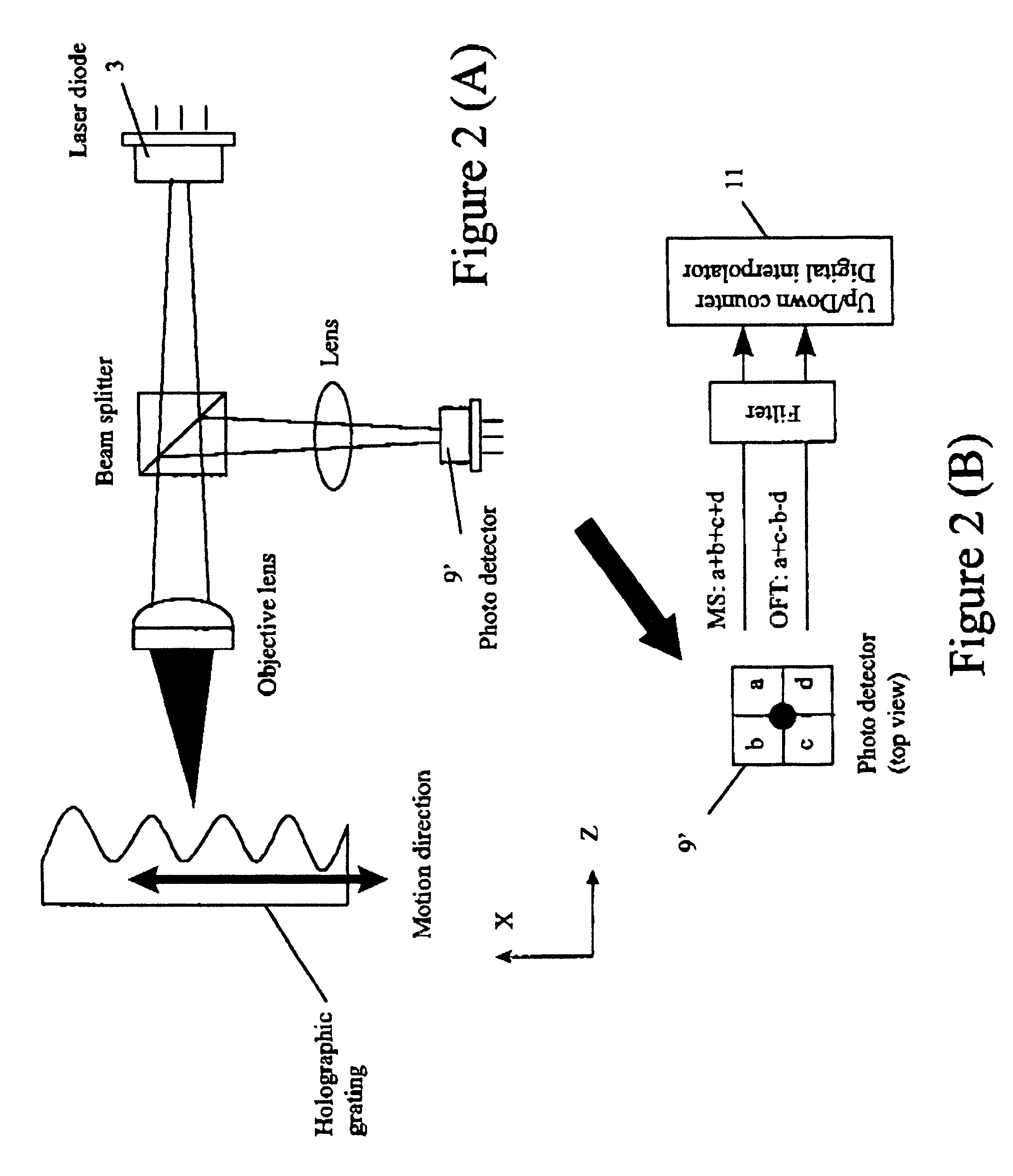

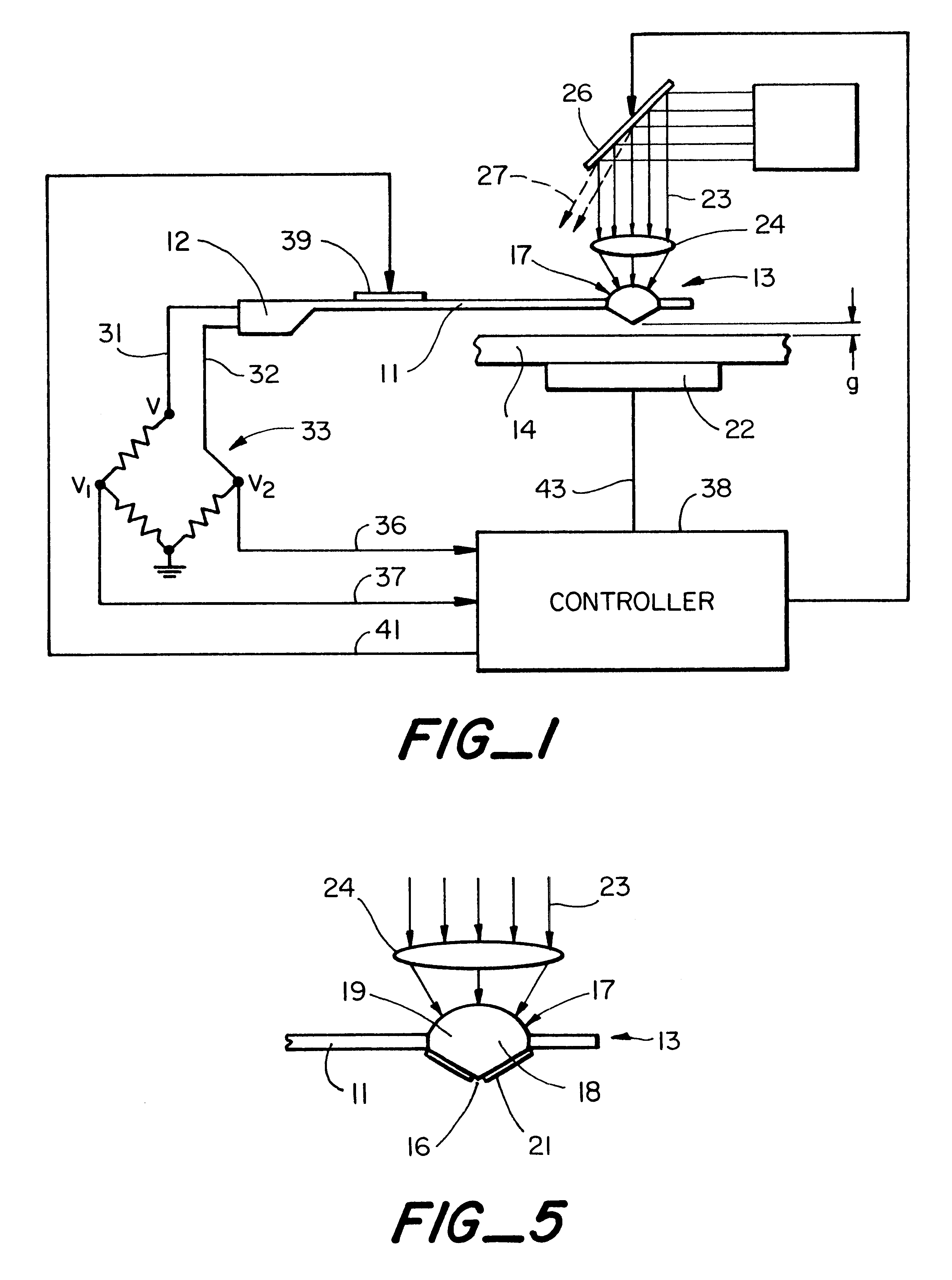

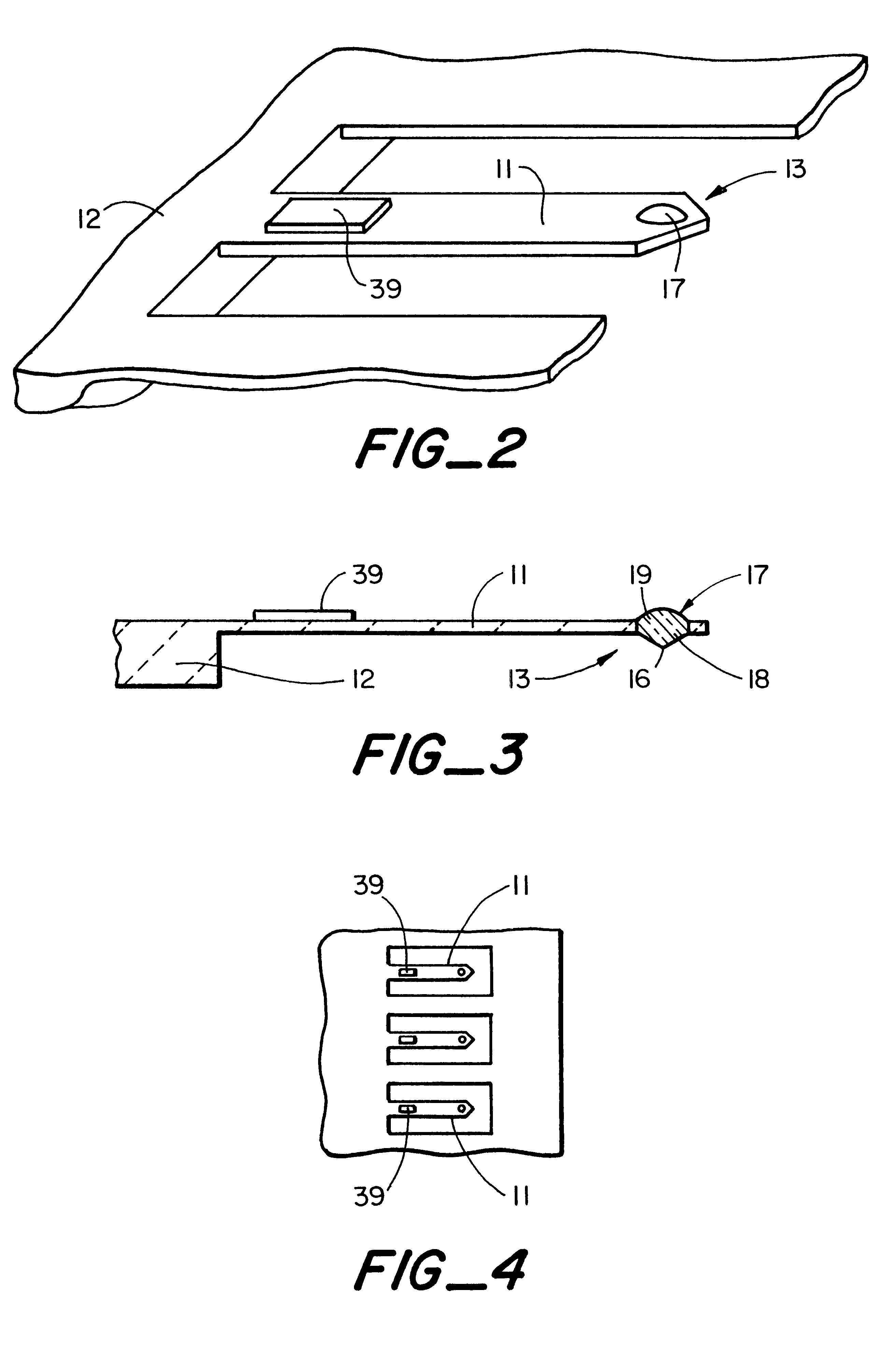

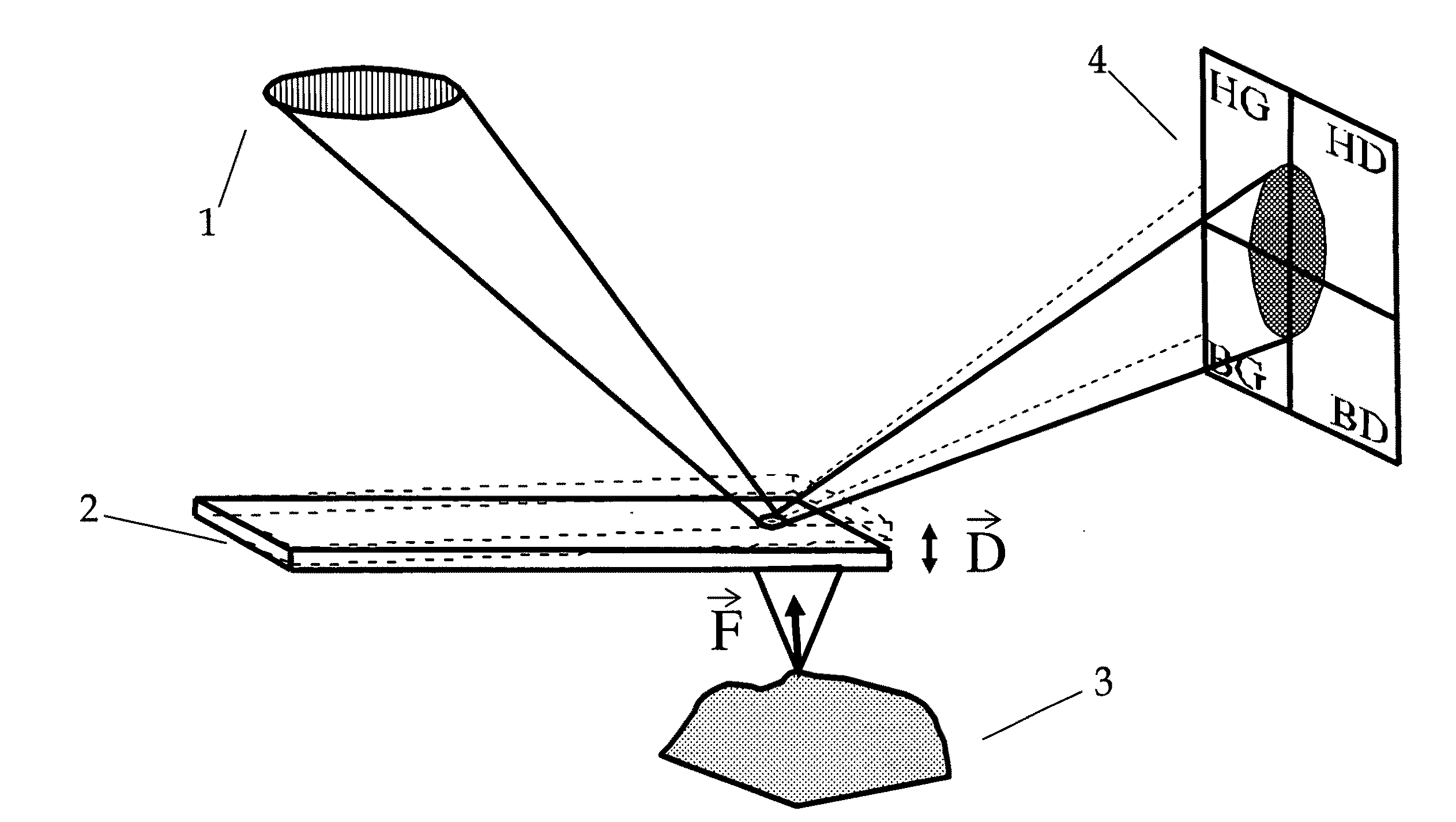

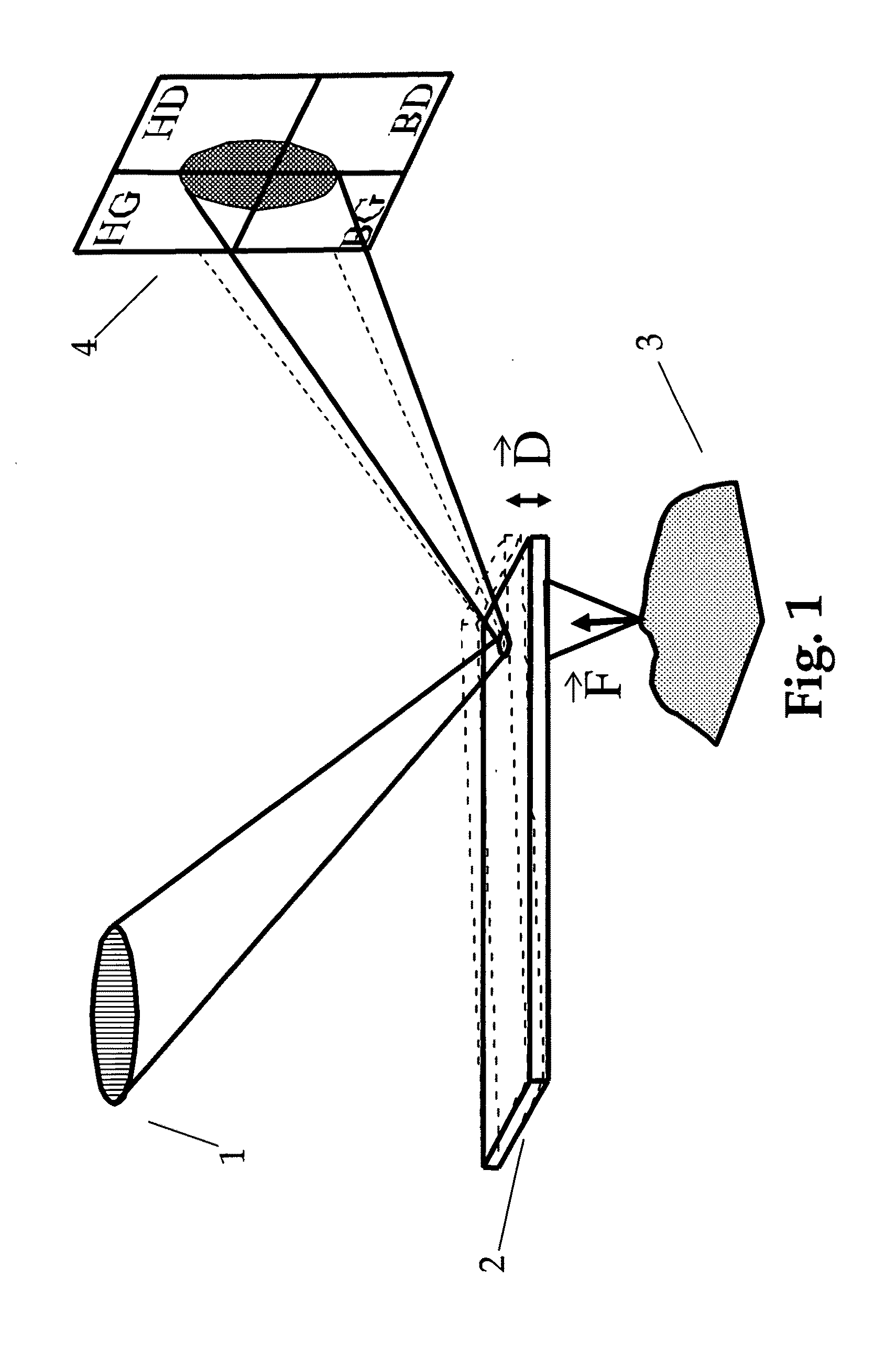

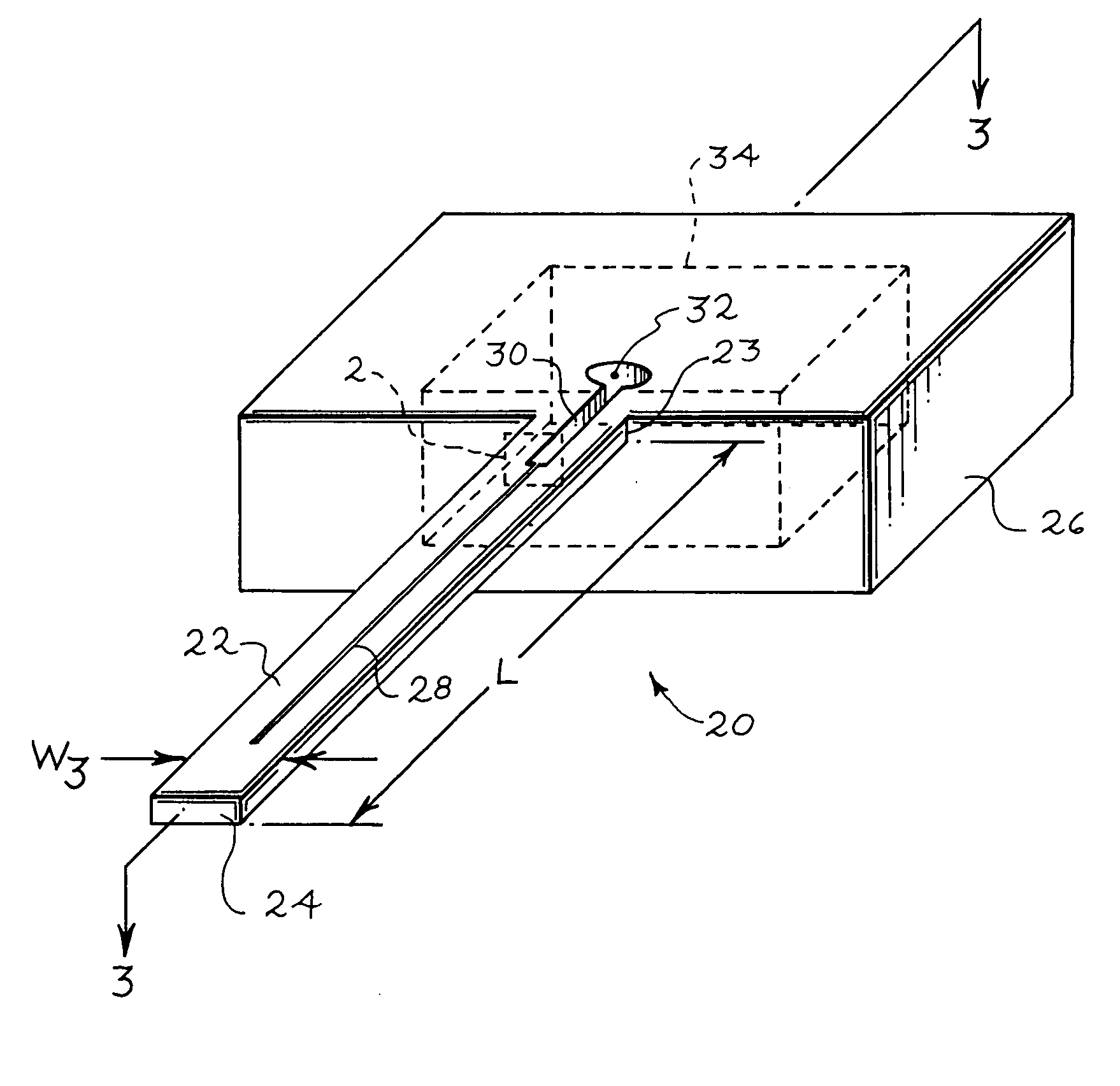

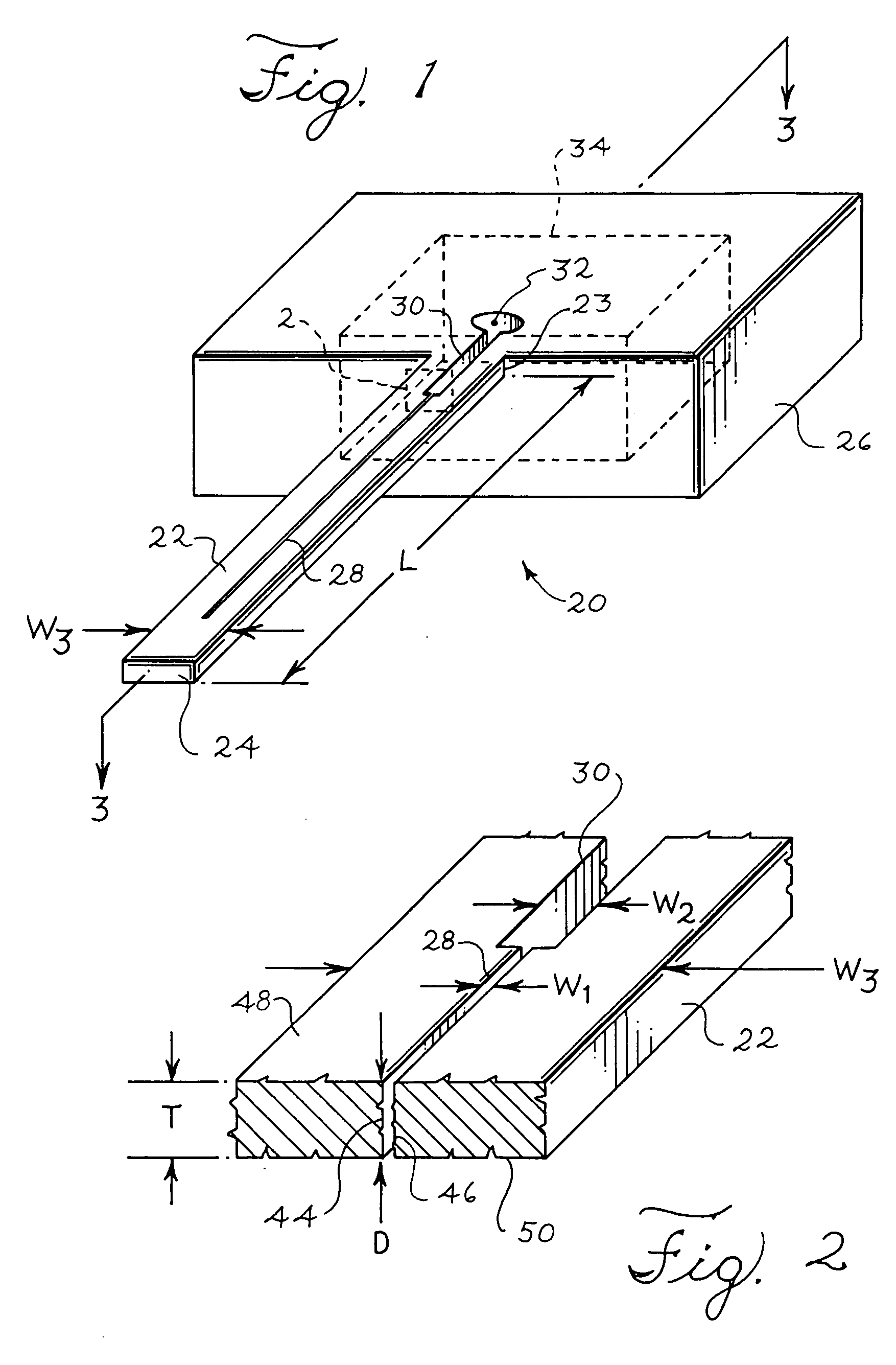

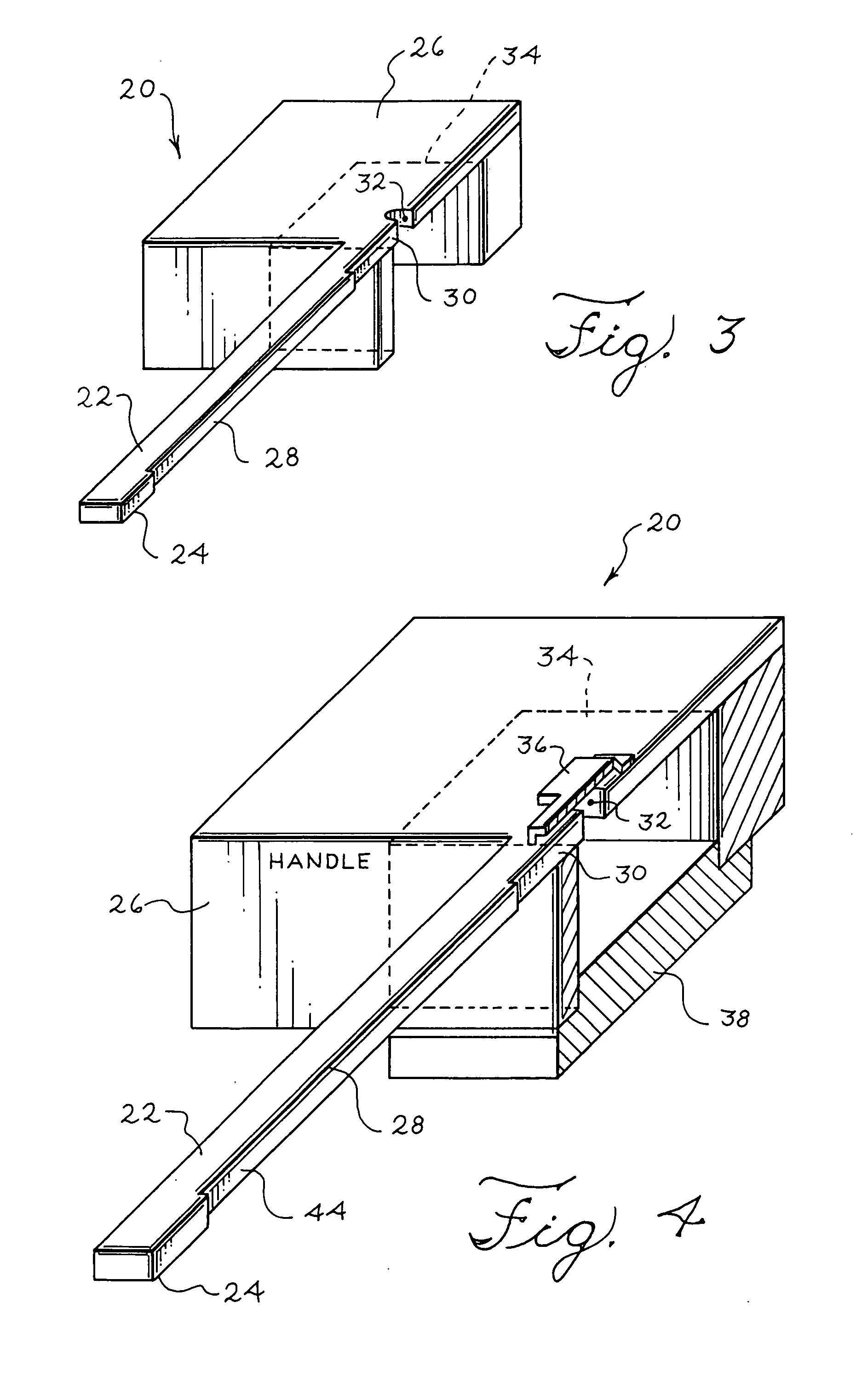

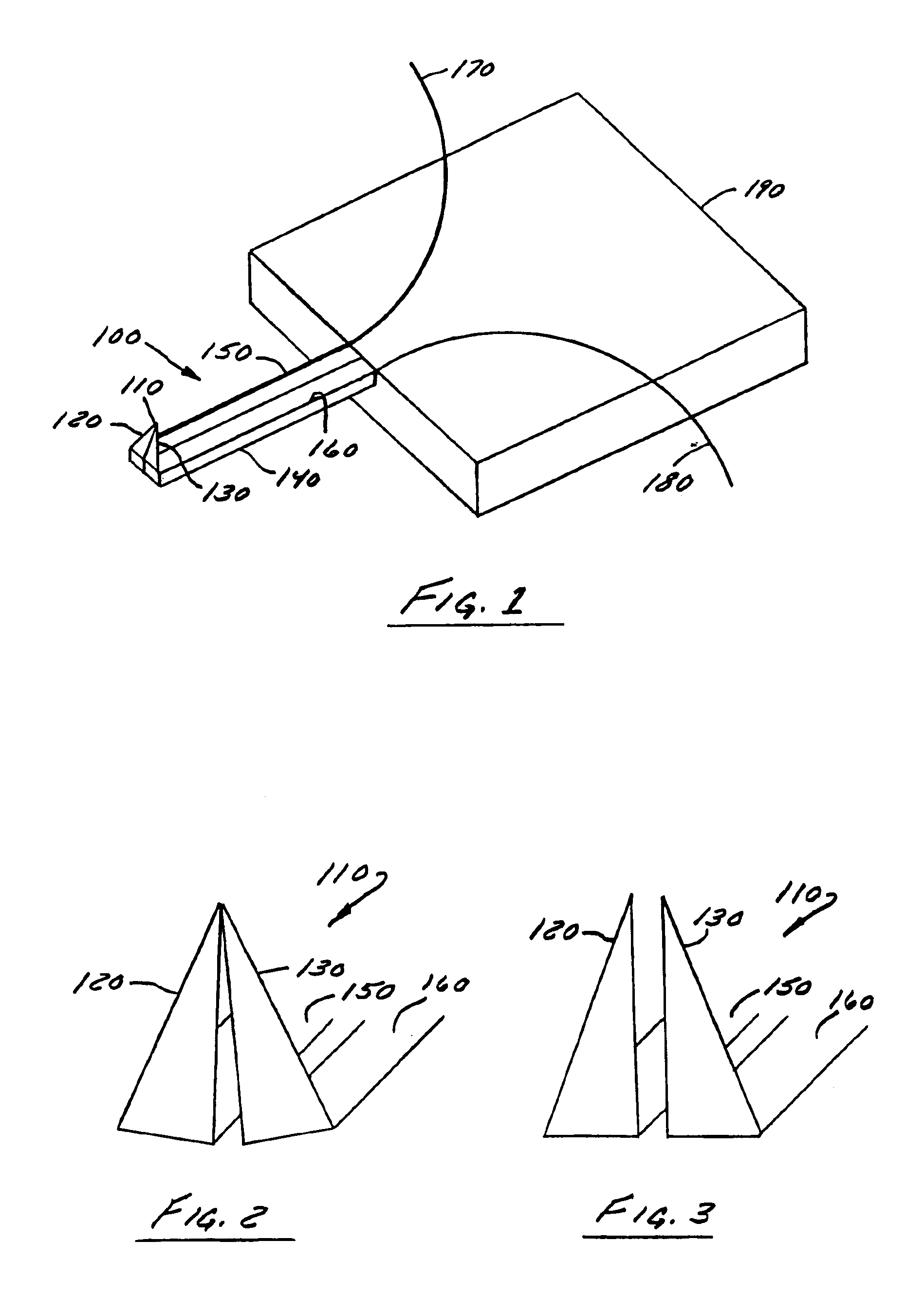

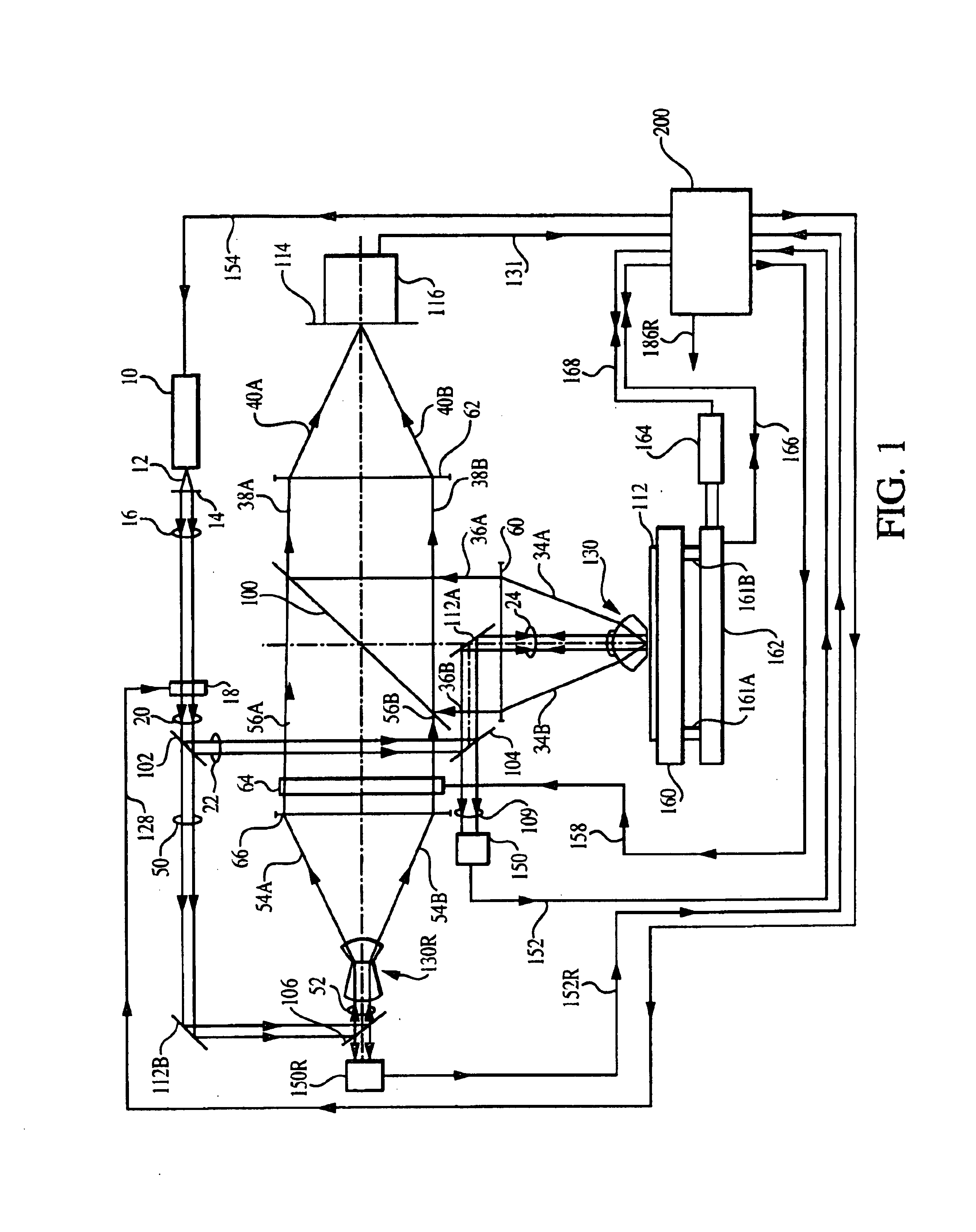

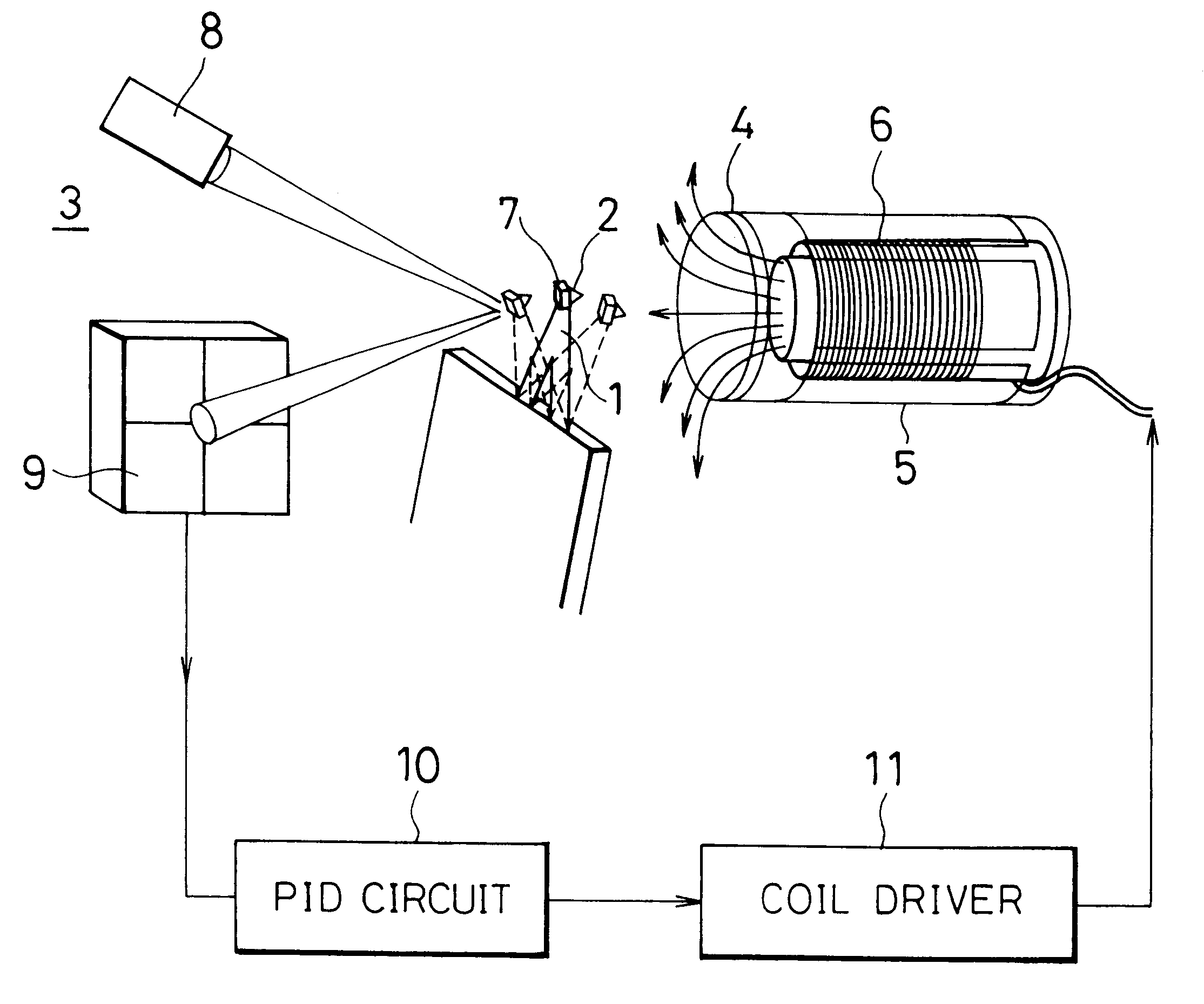

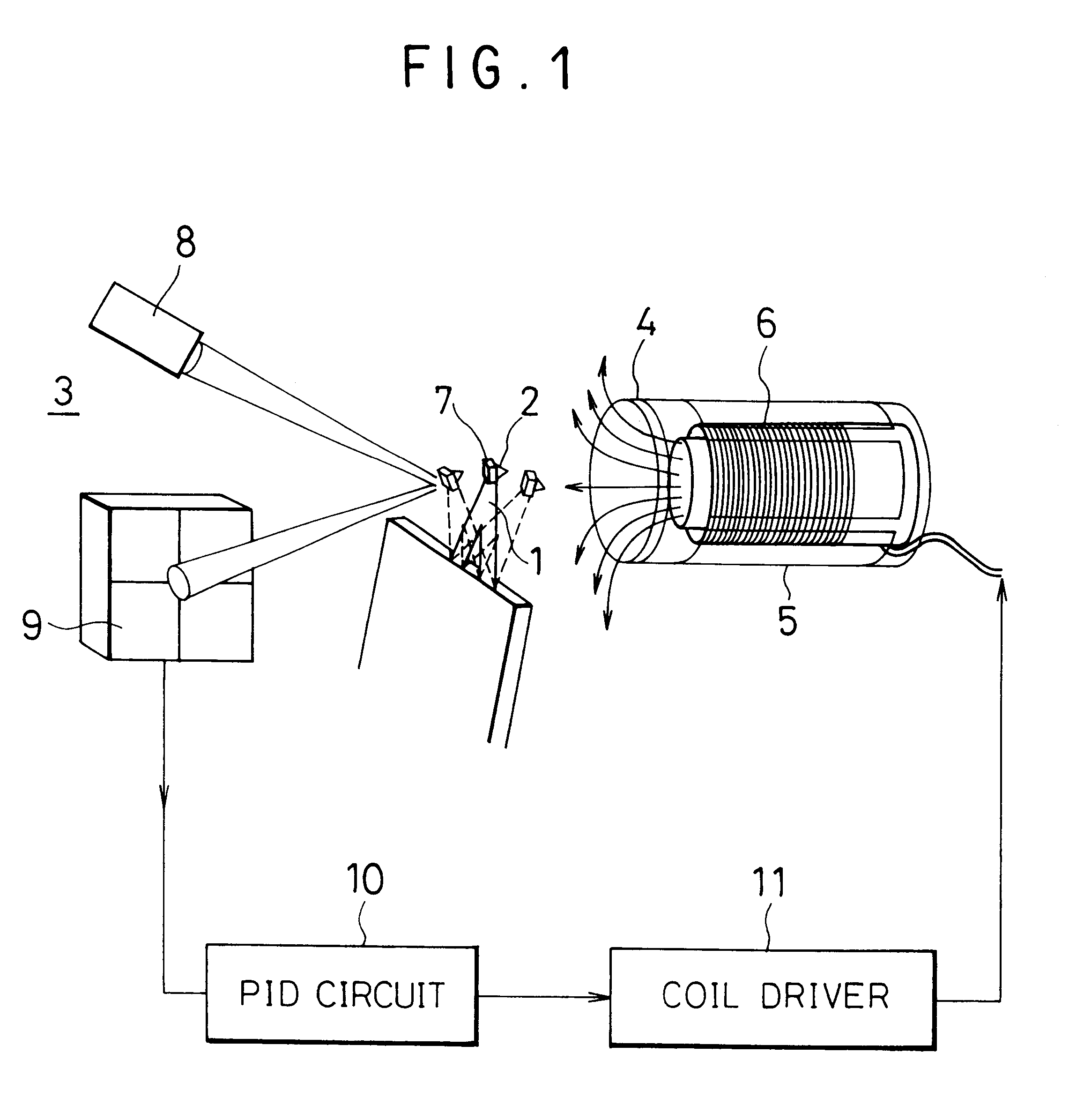

Method of and apparatus for real-time continual nanometer scale position measurement by beam probing as by laser beams and the like of atomic and other undulating surfaces such as gratings or the like relatively moving with respect to the probing beams

InactiveUS6639686B1Improved position sensing responseImprove operationNanoopticsInstrumental componentsGratingLight beam

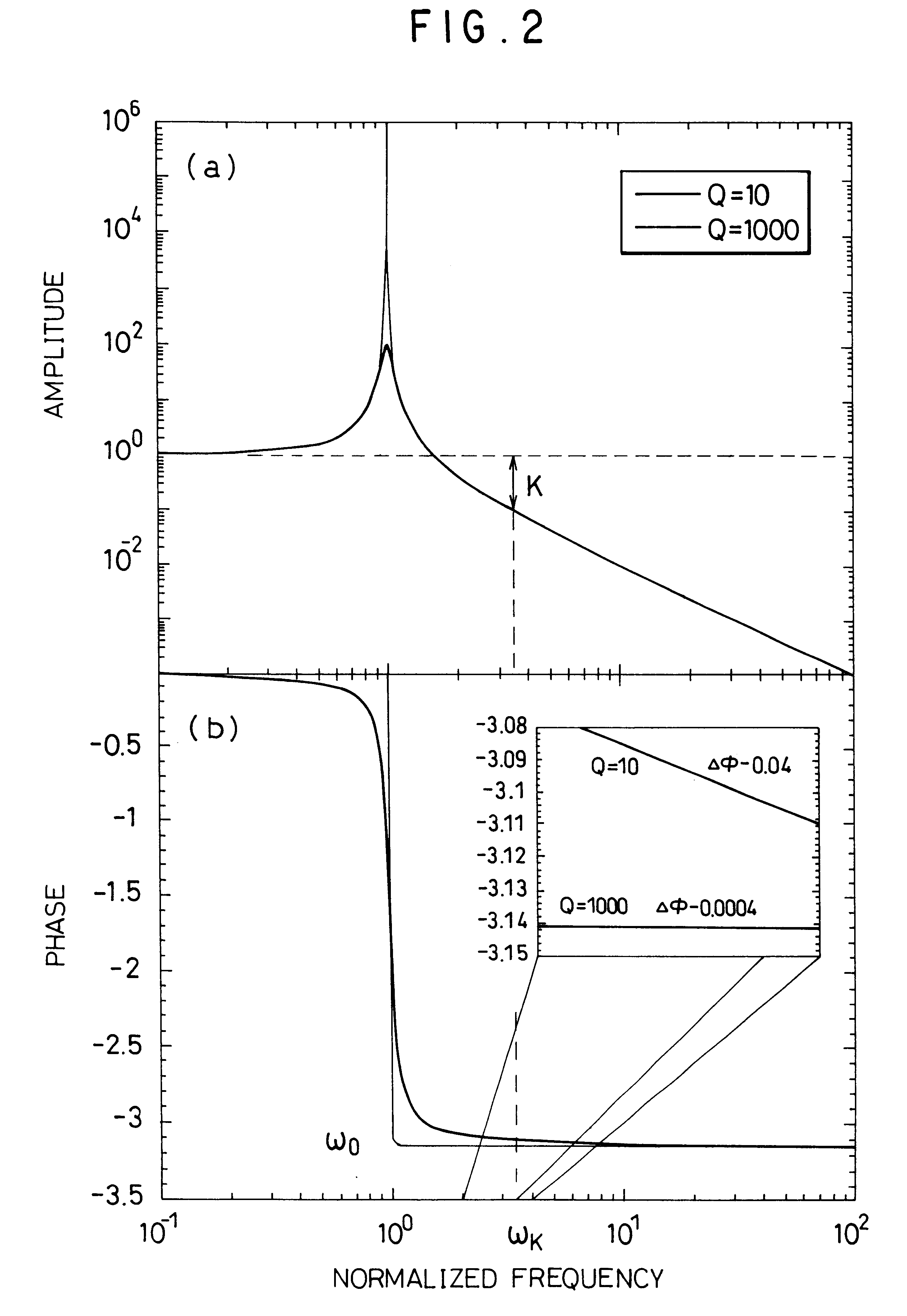

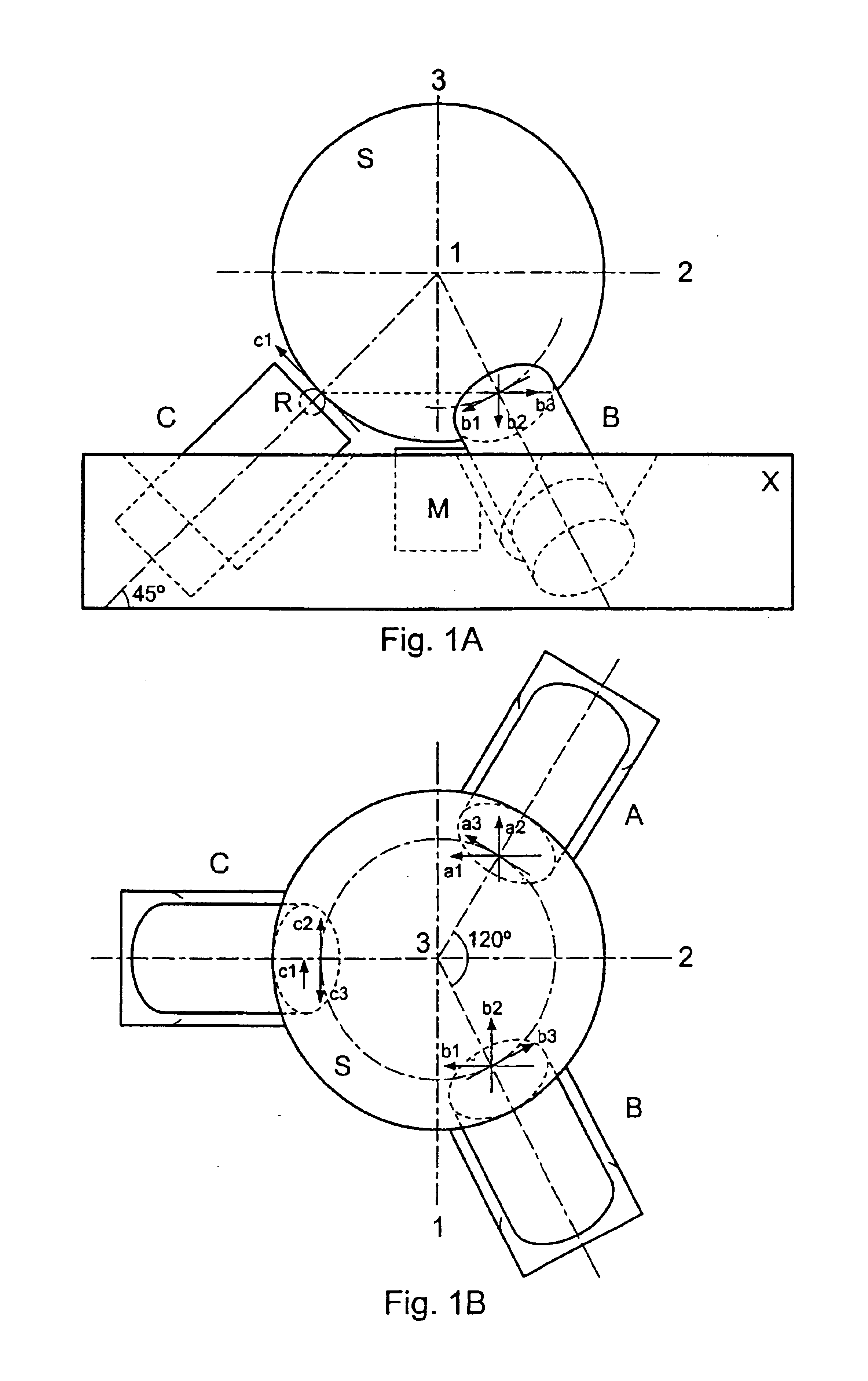

An improved method of and apparatus for real-time continual nanometer scale position measurement by beam probing as by laser beams and the like, both fixed and oscillating or scanning, over an atomic and other undulating surface such as gratings or the like, relatively moving with respect to the probing beams; and providing, where desired, increased detection speeds, improved positioning sensing response, freedom from or relaxed requirements of strict control on probing oscillation amplitude, and multi-dimensional position measurement with focused beam probes and the like.

Owner:NANOWAVE

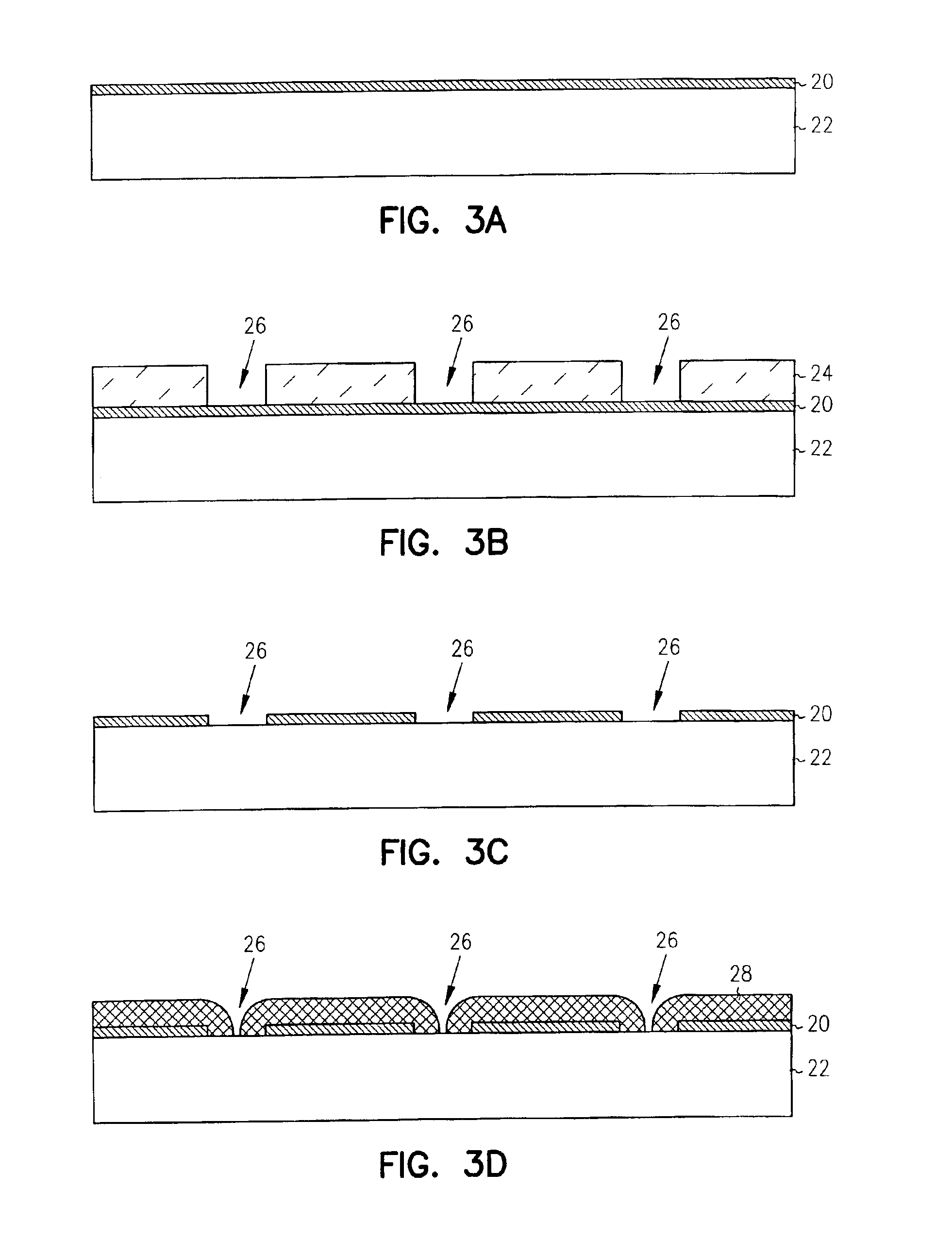

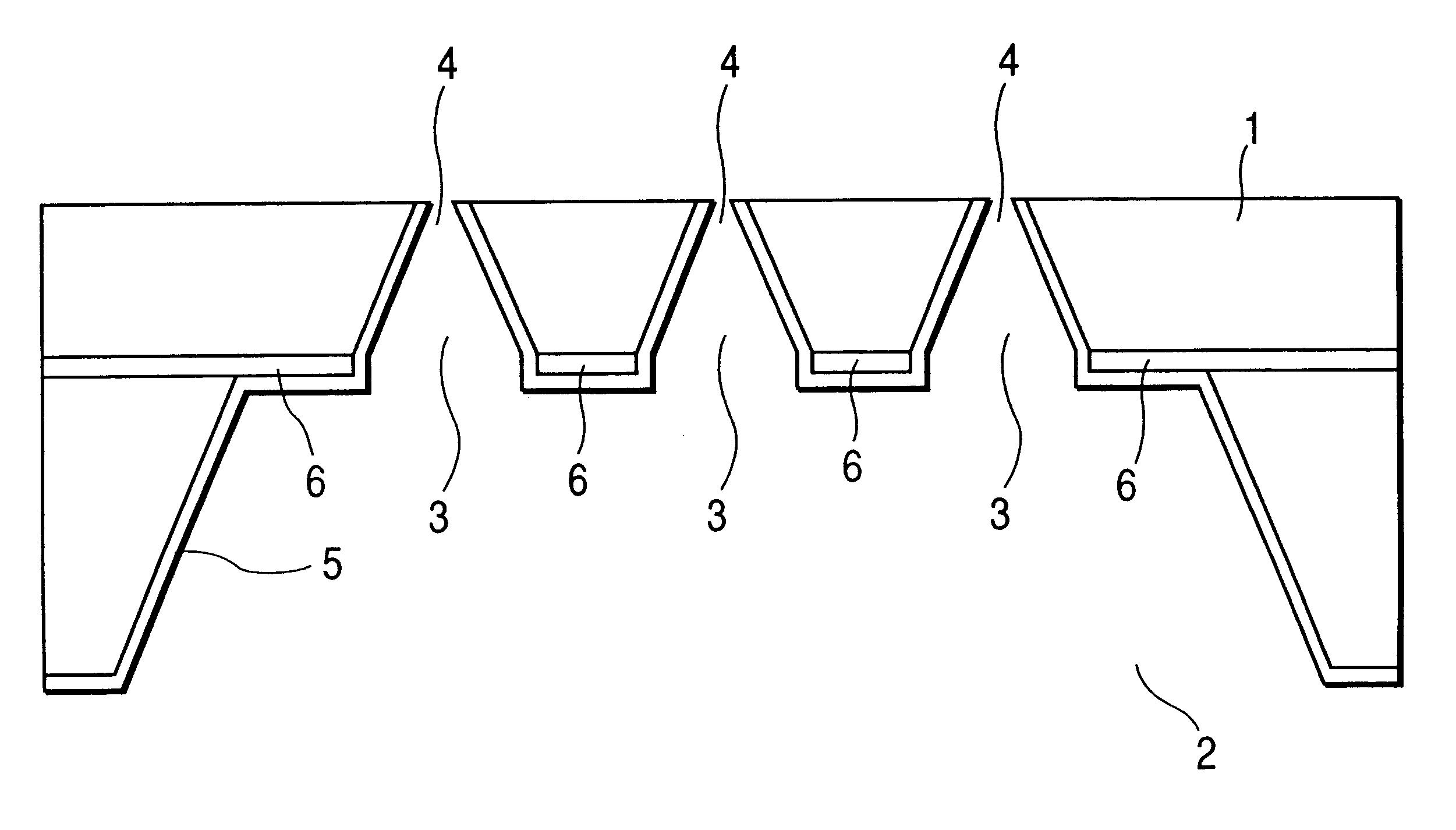

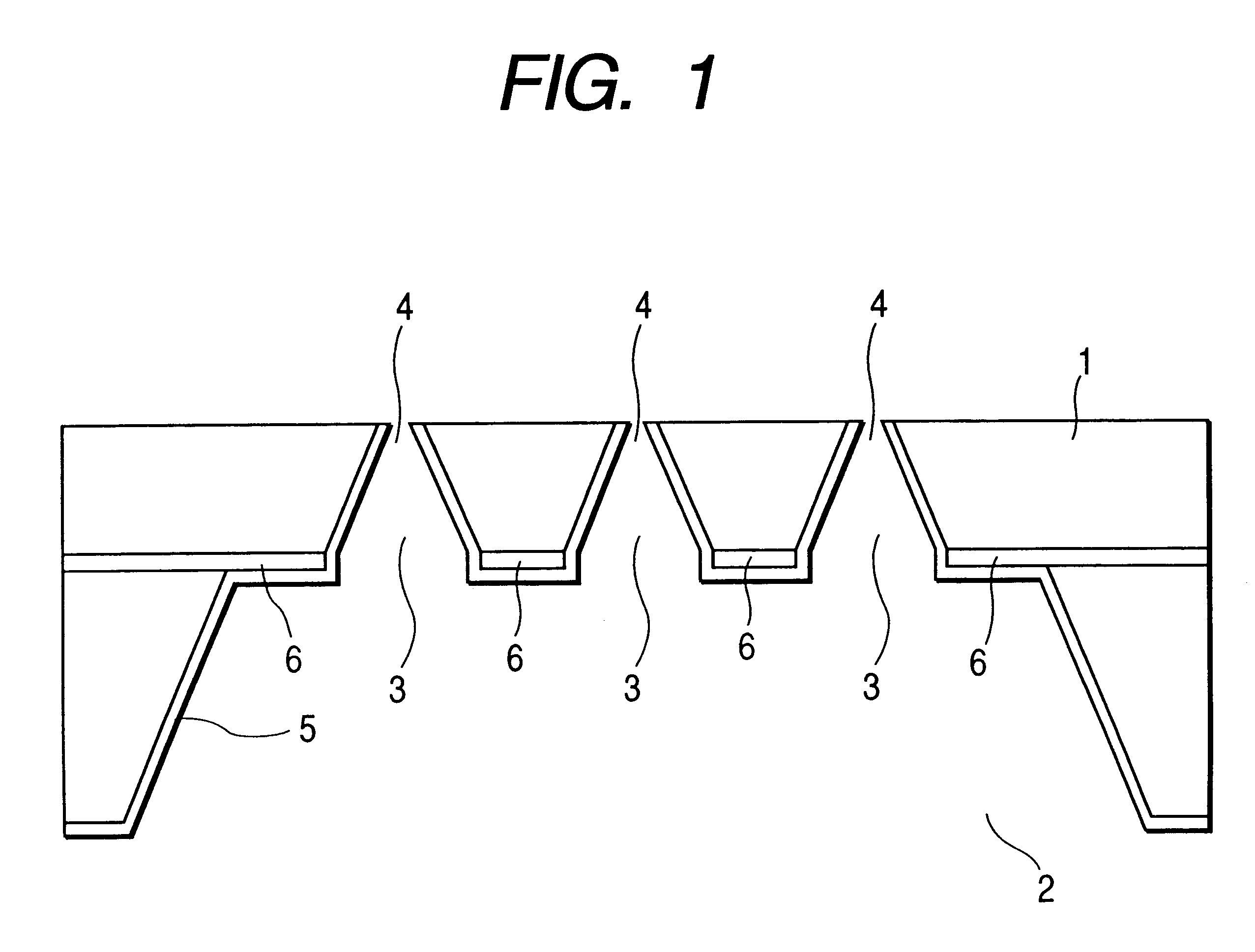

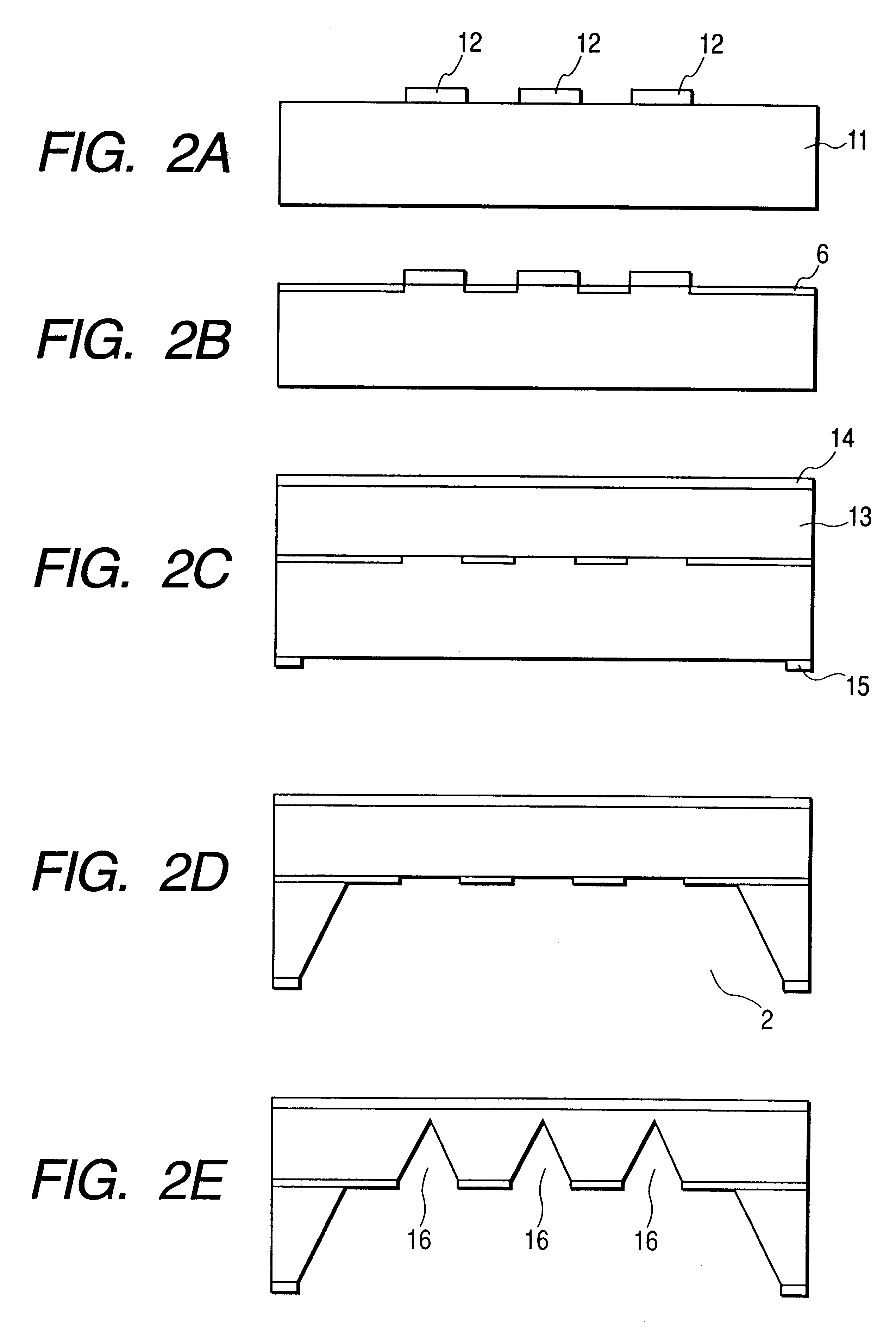

Optical probe for detecting or irradiating light and near-field optical microscope having such probe and manufacturing method of such probe

InactiveUS6215114B1Beam/ray focussing/reflecting arrangementsMaterial analysis by optical meansLight irradiationNear field optical microscope

An optical prove for detecting or irradiating evanescent light is manufactured by forming a film having a regulated film thickness on a substrate, then forming a recess from the rear surface of the substrate, and forming a through hole in the film from the side of the recess by etching. The obtained optical probe has a micro-aperture at the tip of the through hole and usually, a plurality of optical probes each having a micro-aperture of uniform profile are formed on a single substrate. In the recess, light-receiving or light-irradiating means may be provided.

Owner:CANON KK

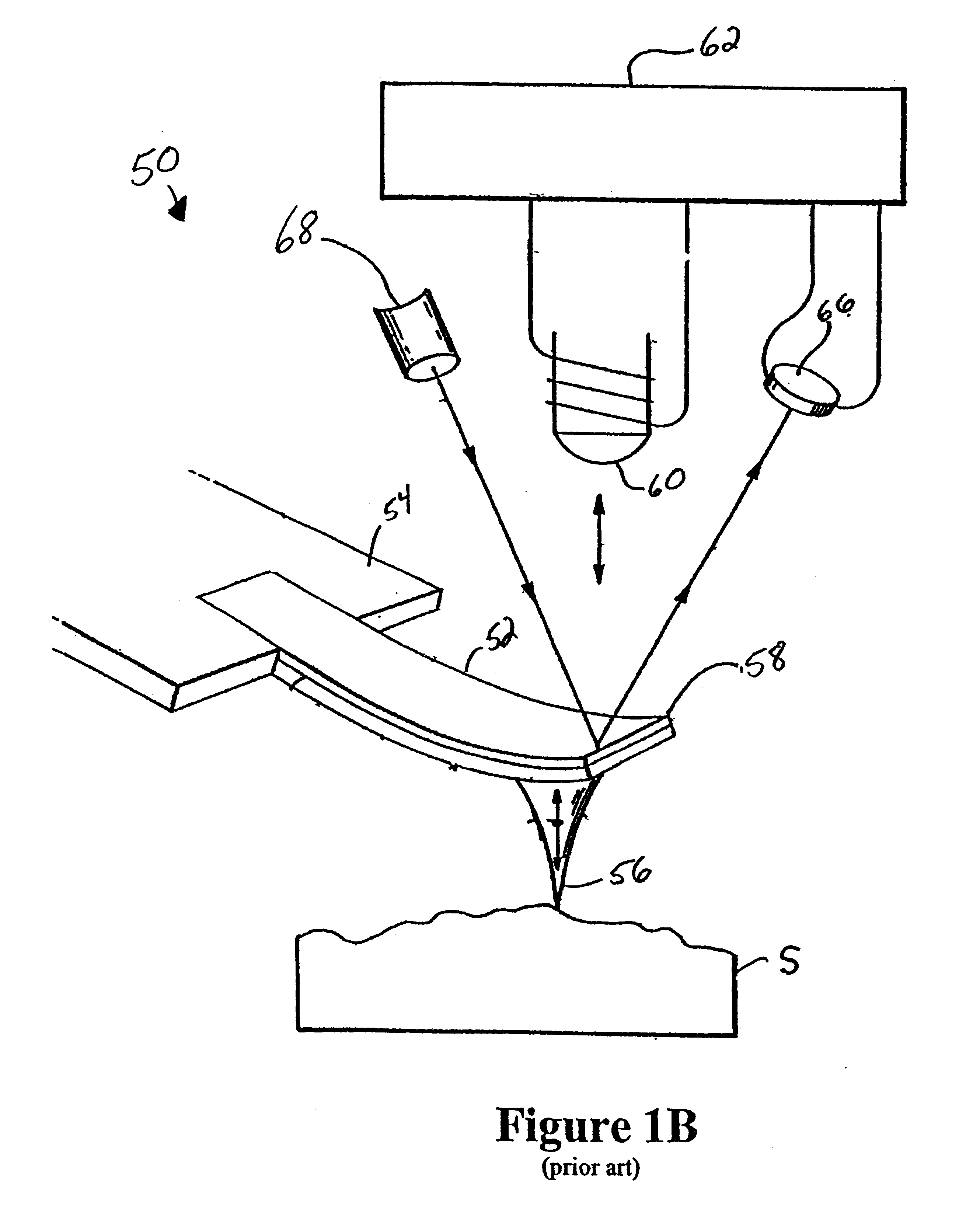

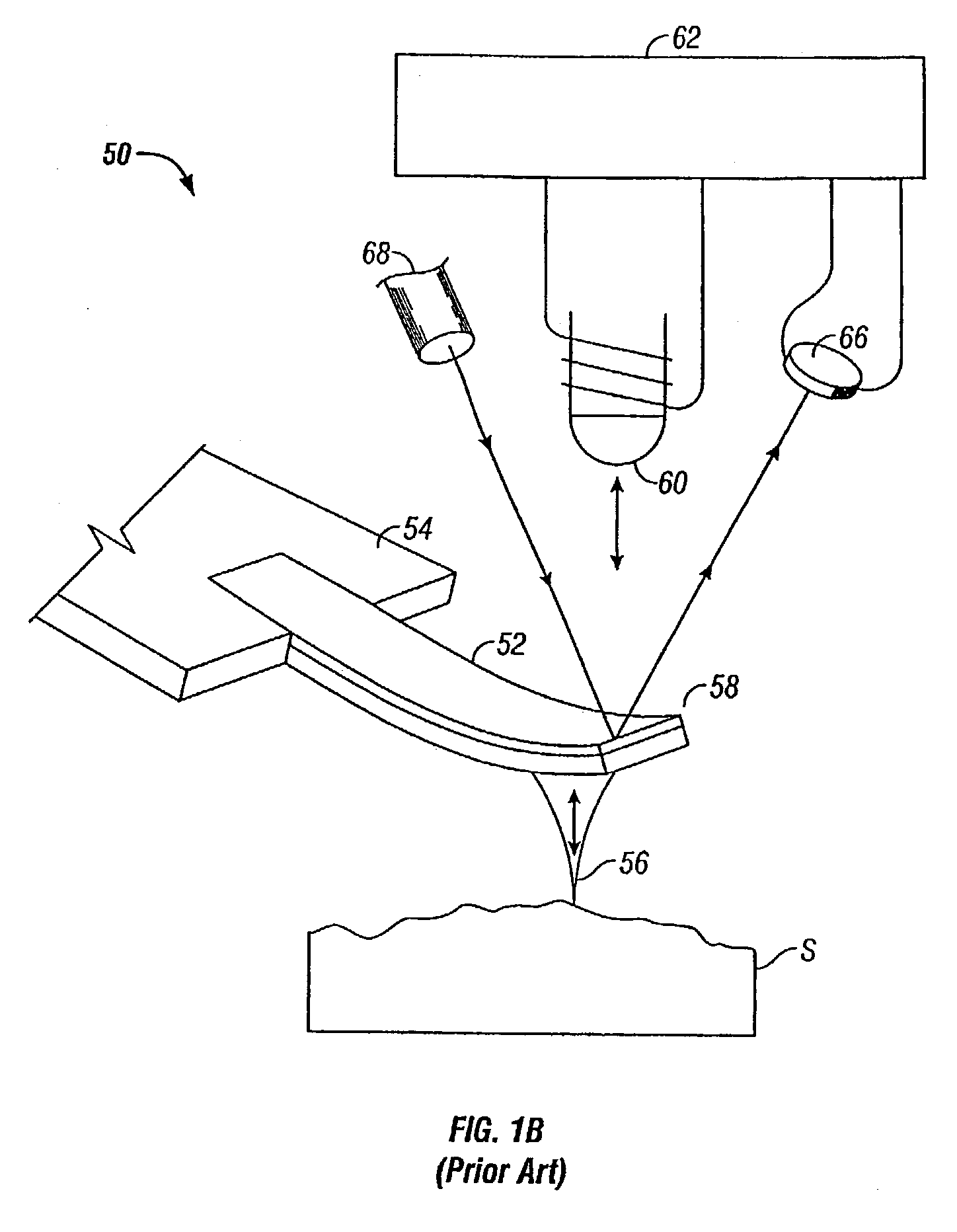

Near field optical scanning system employing microfabricated solid immersion lens

A solid immersion lens integrated on a flexible support such as a cantilever or membrane is described, together with a method of forming the integrated structure.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

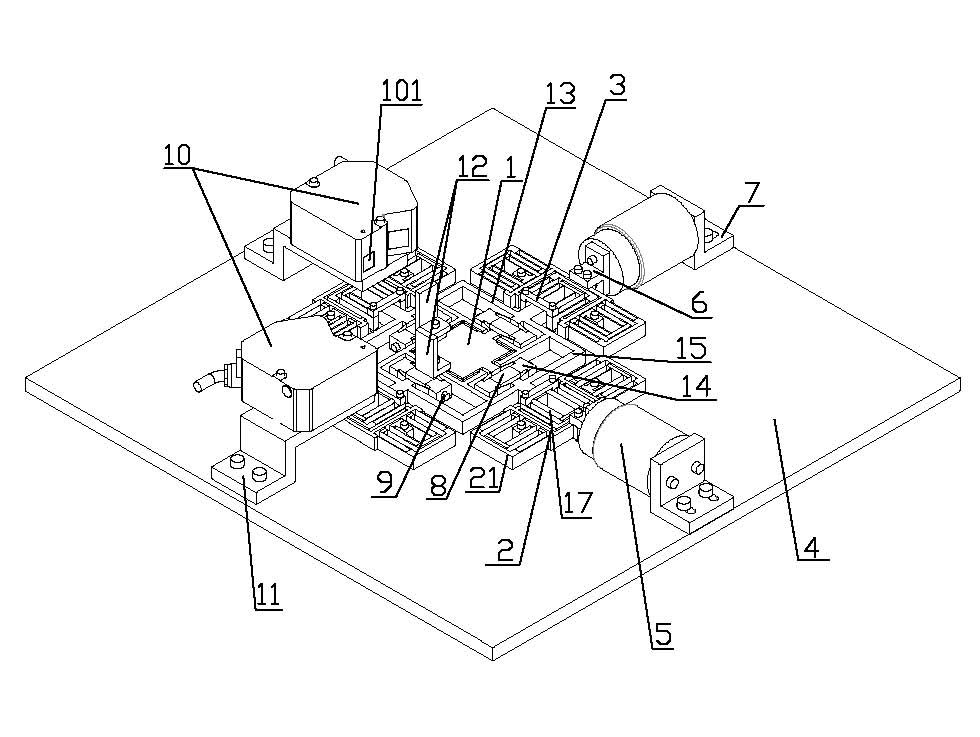

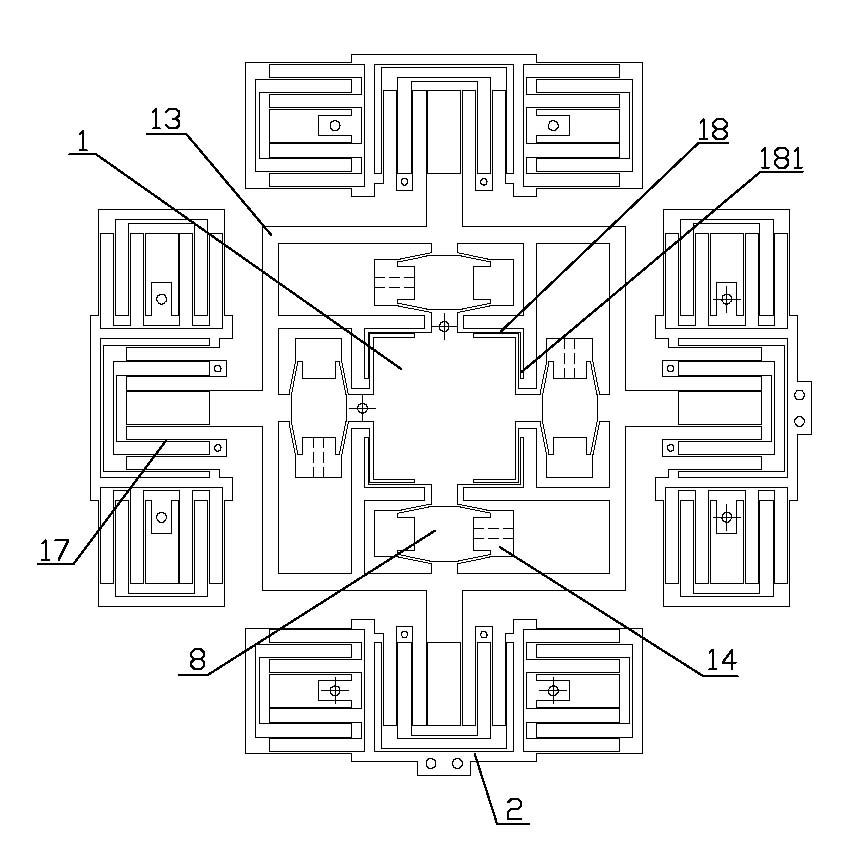

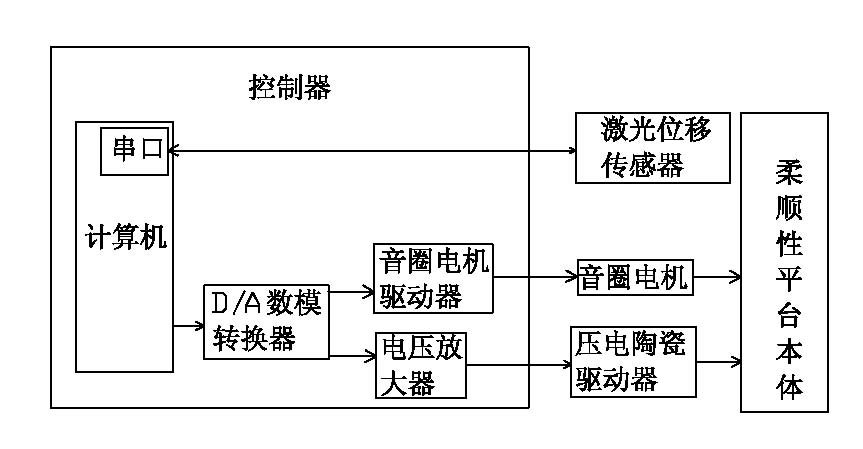

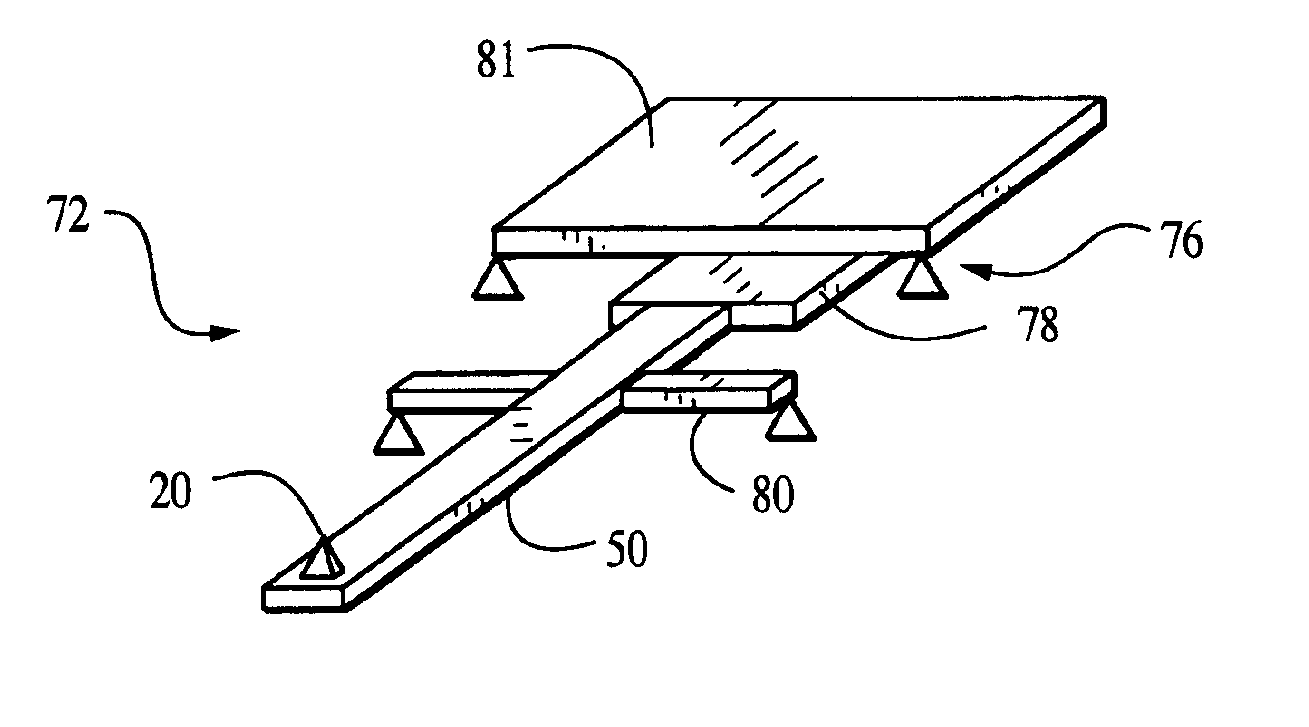

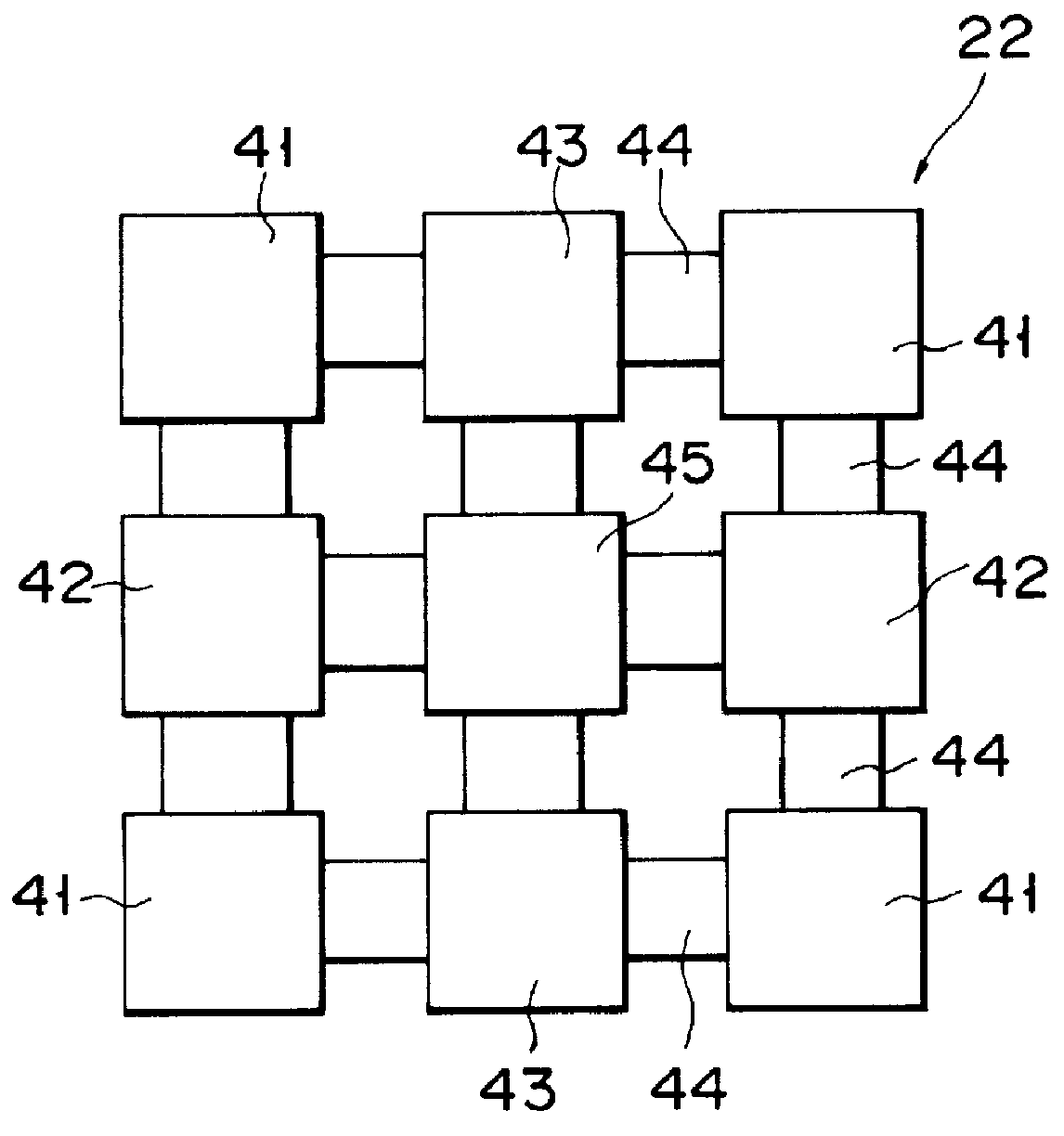

Macro-micro driven bidimensional integrated micro positioning platform

ActiveCN102543217ASmall moment of inertiaIncrease stiffnessInstrumental componentsElectricityFlexible Mechanisms

The invention provides a macro-micro driven bidimensional integrated micro positioning platform, which is characterized by including a base, a flexible platform body, two voice coil motors, four piezoelectric ceramic actuators, two displacement sensors and a controller, wherein the flexible platform body is fixed on the base; the two voice coil motors are connected with the flexible platform body; and the controller is in signal connection with the two voice coil motors, the four piezoelectric ceramic actuators and the two displacement sensors. The macro-micro driven bidimensional integrated micro positioning platform adopts a parallel decoupling totally flexible mechanism, and has the advantages of a parallel mechanism, a flexible mechanism and a decoupling mechanism; a macro-motion platform and a micro-motion platform are integrally designed; the same piece of material can be adopted to manufacture the macro-micro driven bidimensional integrated micro positioning platform integrally, and the manufacture is simple and convenient; and the motion decoupling design is applied to the macro-motion platform and the micro-motion platform, so that the motion control is facilitated and the positioning accuracy is improved.

Owner:UNIVERSITY OF MACAU

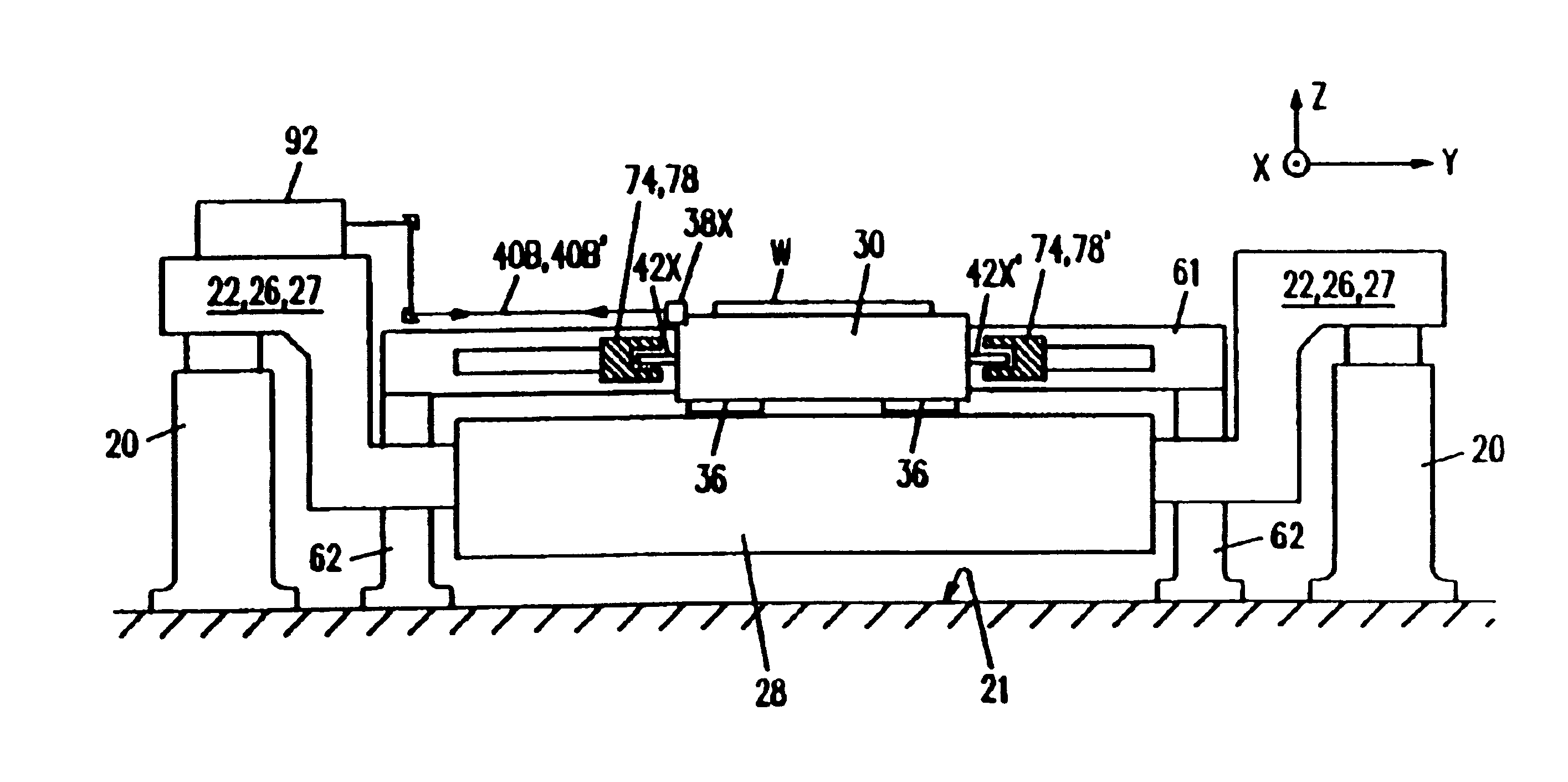

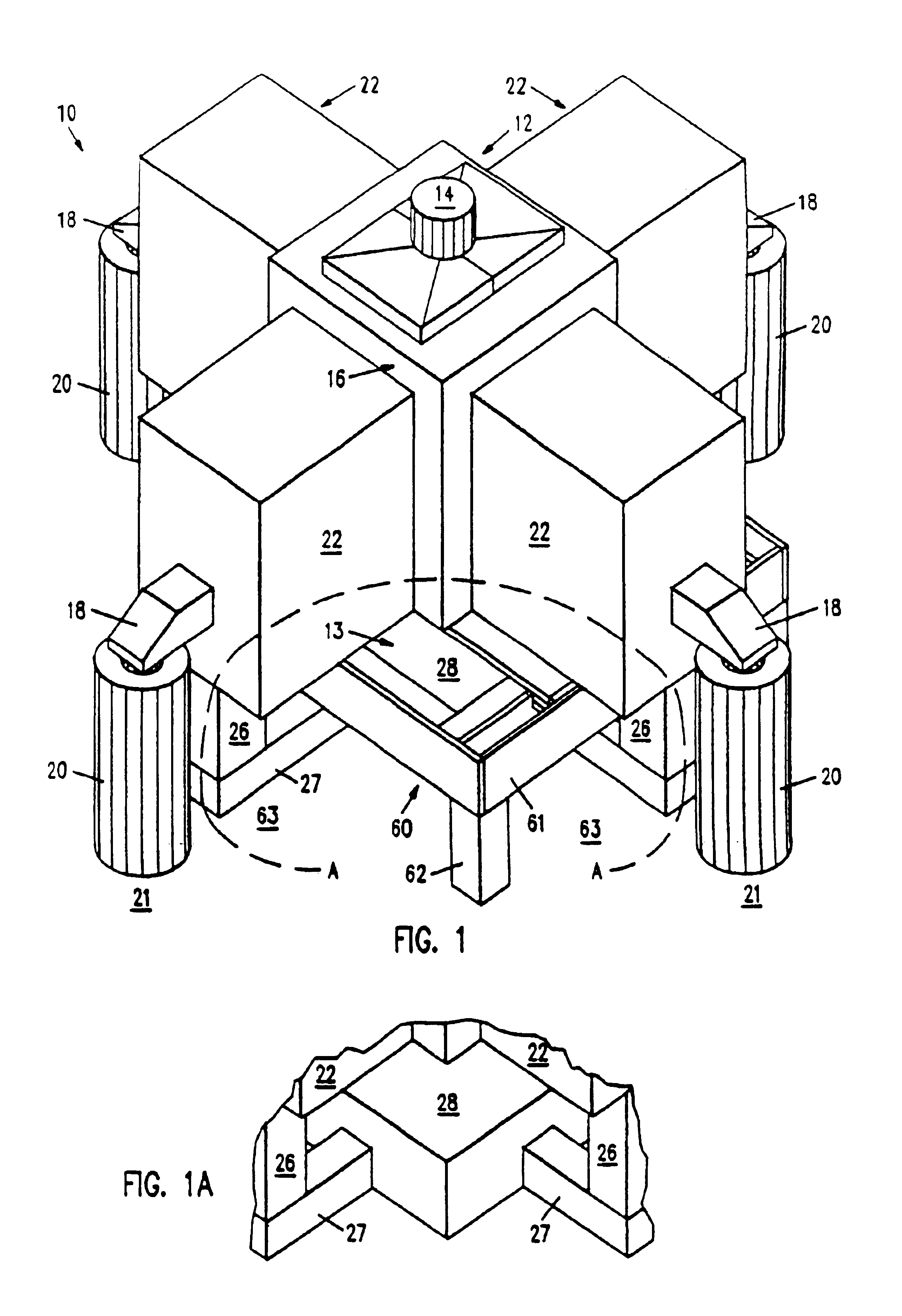

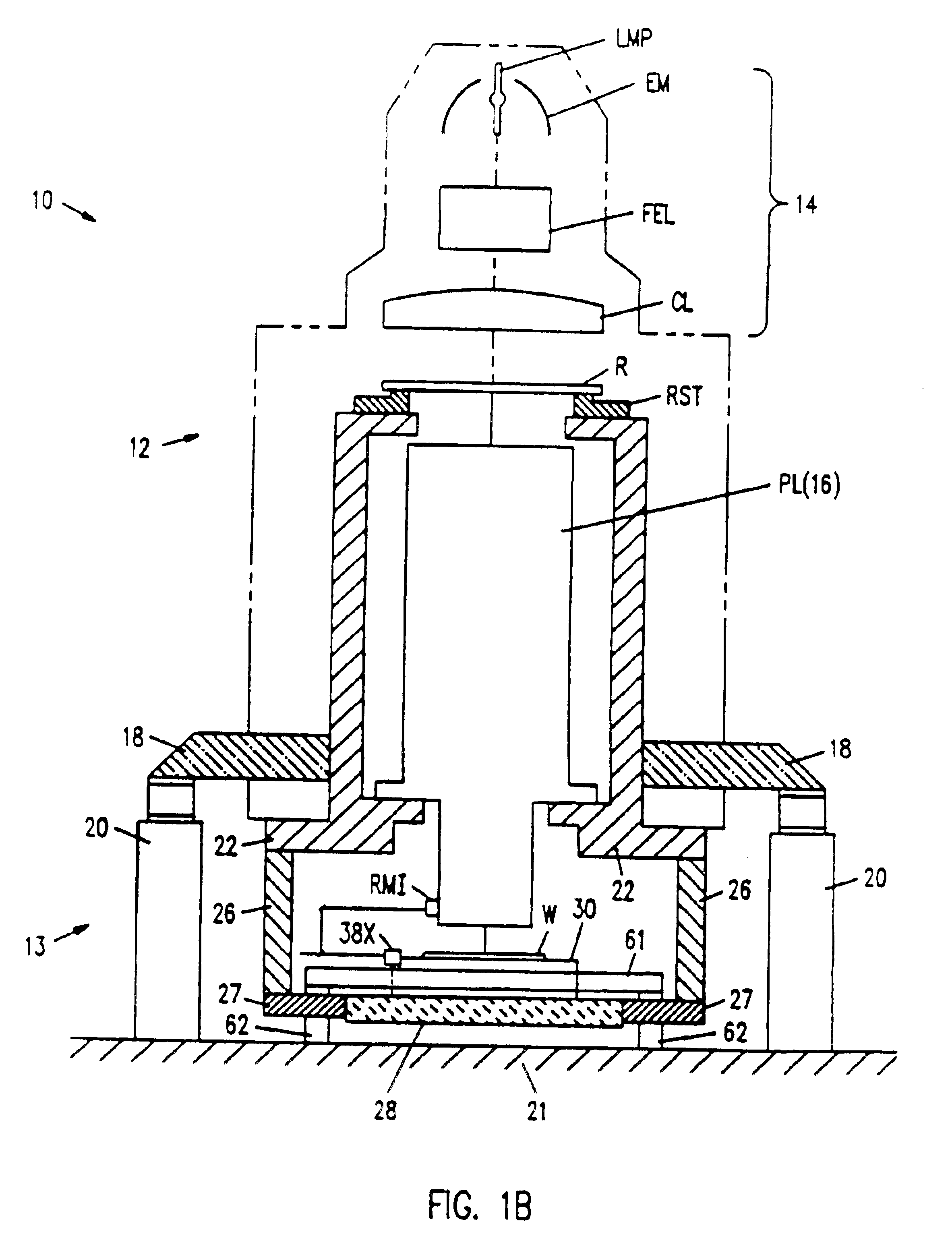

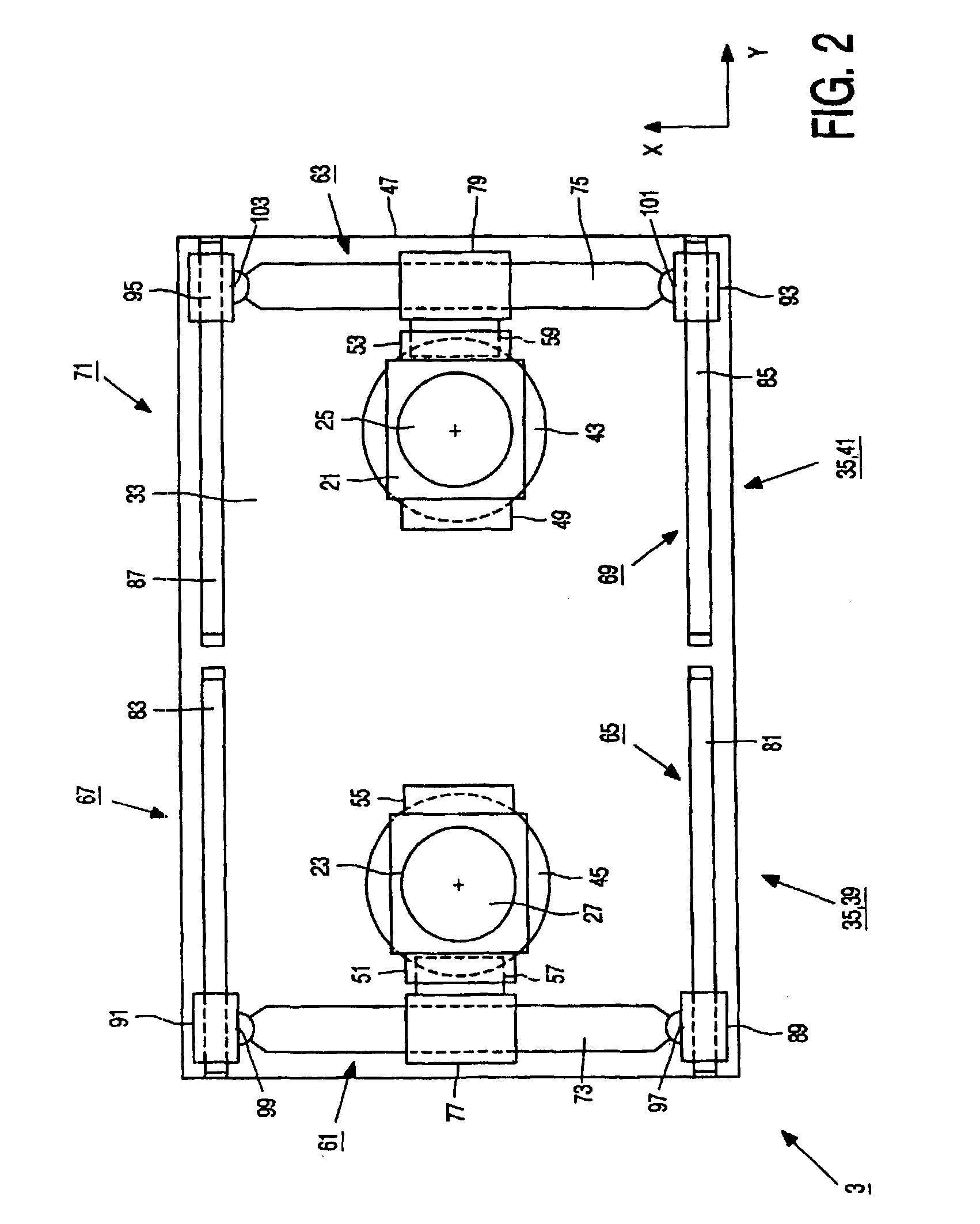

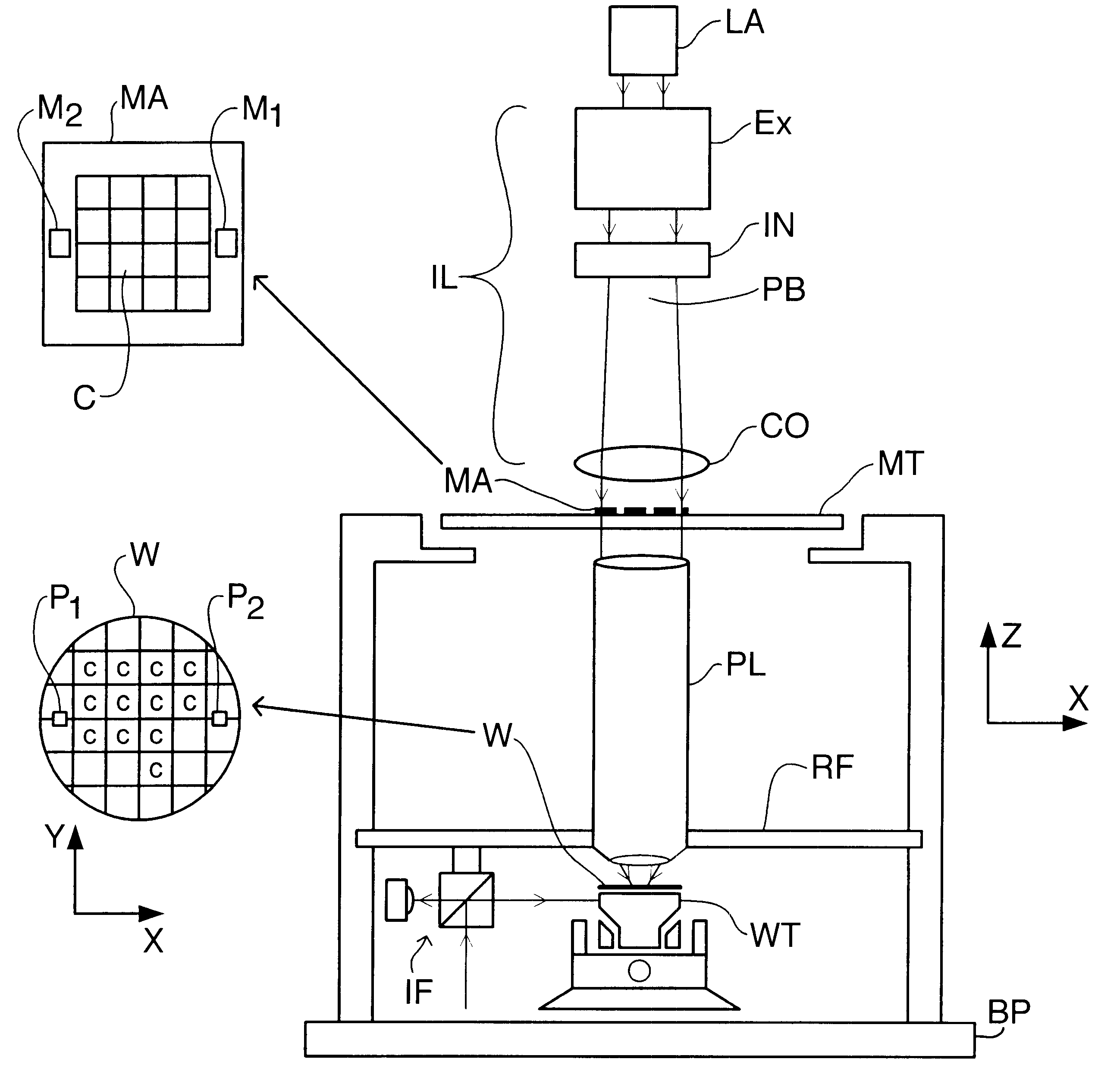

Guideless stage with isolated reaction stage

InactiveUS6841965B2Minimize couplingElectric discharge tubesNon-rotating vibration suppressionEngineeringActuator

A guideless stage for aligning a wafer in a microlithography system is disclosed, and a reaction frame is disclosed which isolates both external vibrations as well as vibrations caused by reaction forces from an object stage. In the guideless stage an object stage is disclosed for movement in at least two directions and two separate and independently movable followers move and follow the object stage and cooperating linear force actuators are mounted on the object stage and the followers for positioning the object stage in the first and second directions. The reaction frame is mounted on a base structure independent of the base for the object stage so that the object stage is supported in space independent of the reaction frame. At least one follower is disclosed having a pair of arms which are respectively movable in a pair of parallel planes with the center of gravity of the object stage therebetween. The linear positioning forces of the actuator drive means are mounted and controlled so that the vector sum of the moments of force at the center of gravity of the object stage due to the positioning forces of the drive means is substantially equal to zero. The actuator mounting means can include at least two thin flexible members mounted in series with the primary direction of flex of the members being orthogonal to one another.

Owner:NIKON CORP

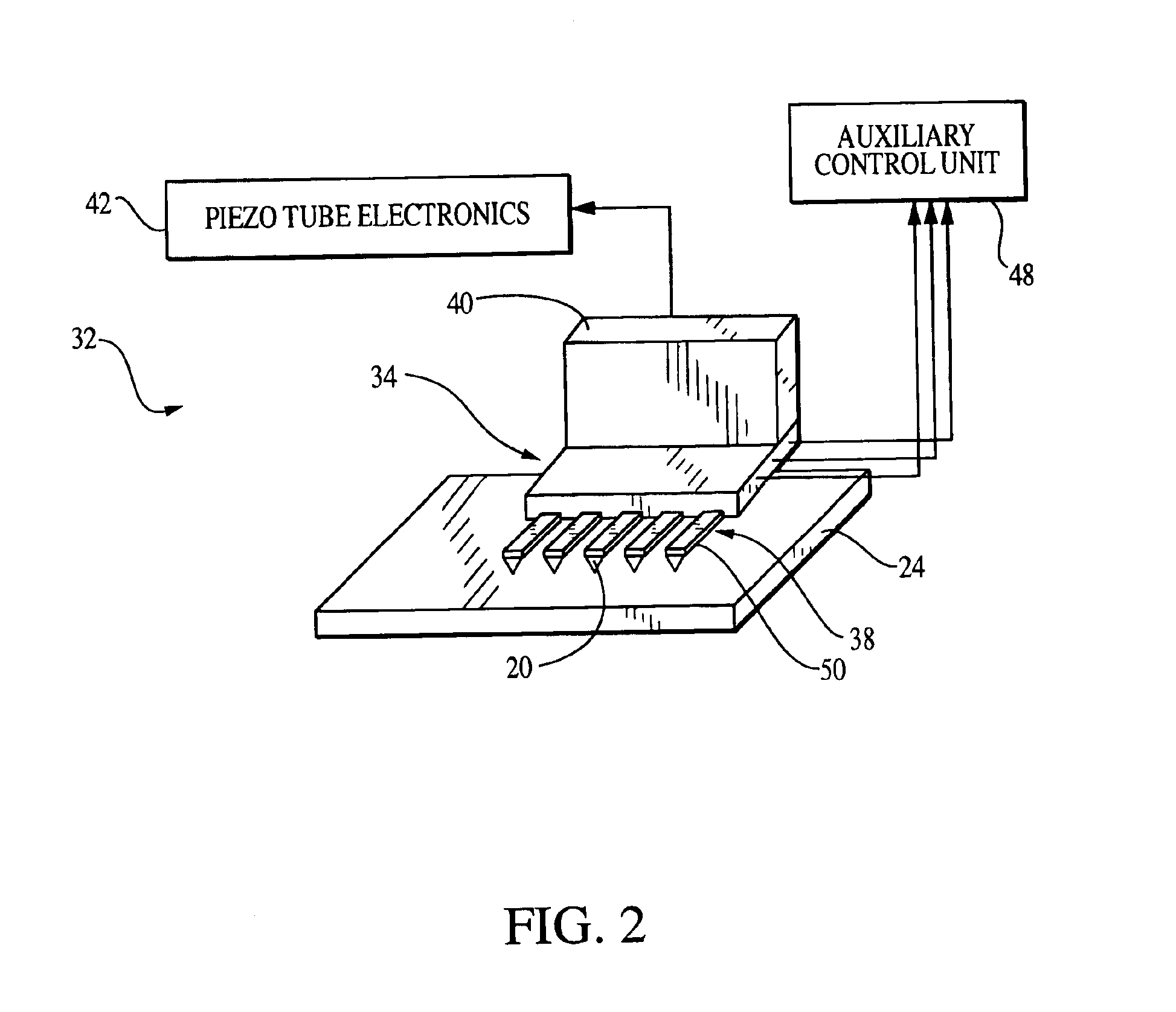

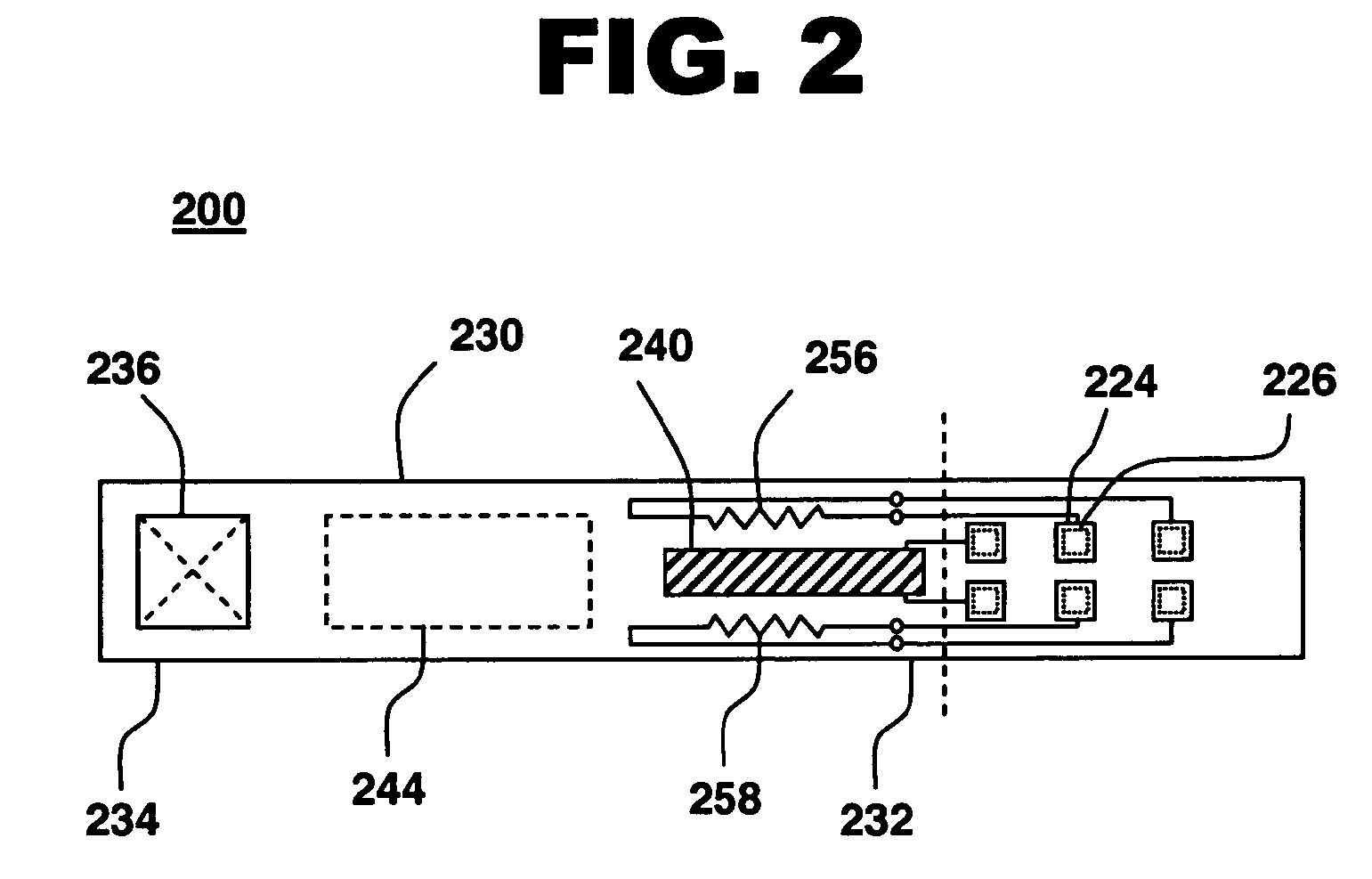

Parallel, individually addressable probes for nanolithography

InactiveUS6867443B2Increase temperatureImprove completenessNanoinformaticsSolid-state devicesNanolithographyImage resolution

A microfabricated probe array for nanolithography and process for designing and fabricating the probe array. The probe array consists of individual probes that can be moved independently using thermal bimetallic actuation or electrostatic actuation methods. The probe array can be used to produce traces of diffusively transferred chemicals on the substrate with sub-1 micrometer resolution, and can function as an arrayed scanning probe microscope for subsequent reading and variation of transferred patterns.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

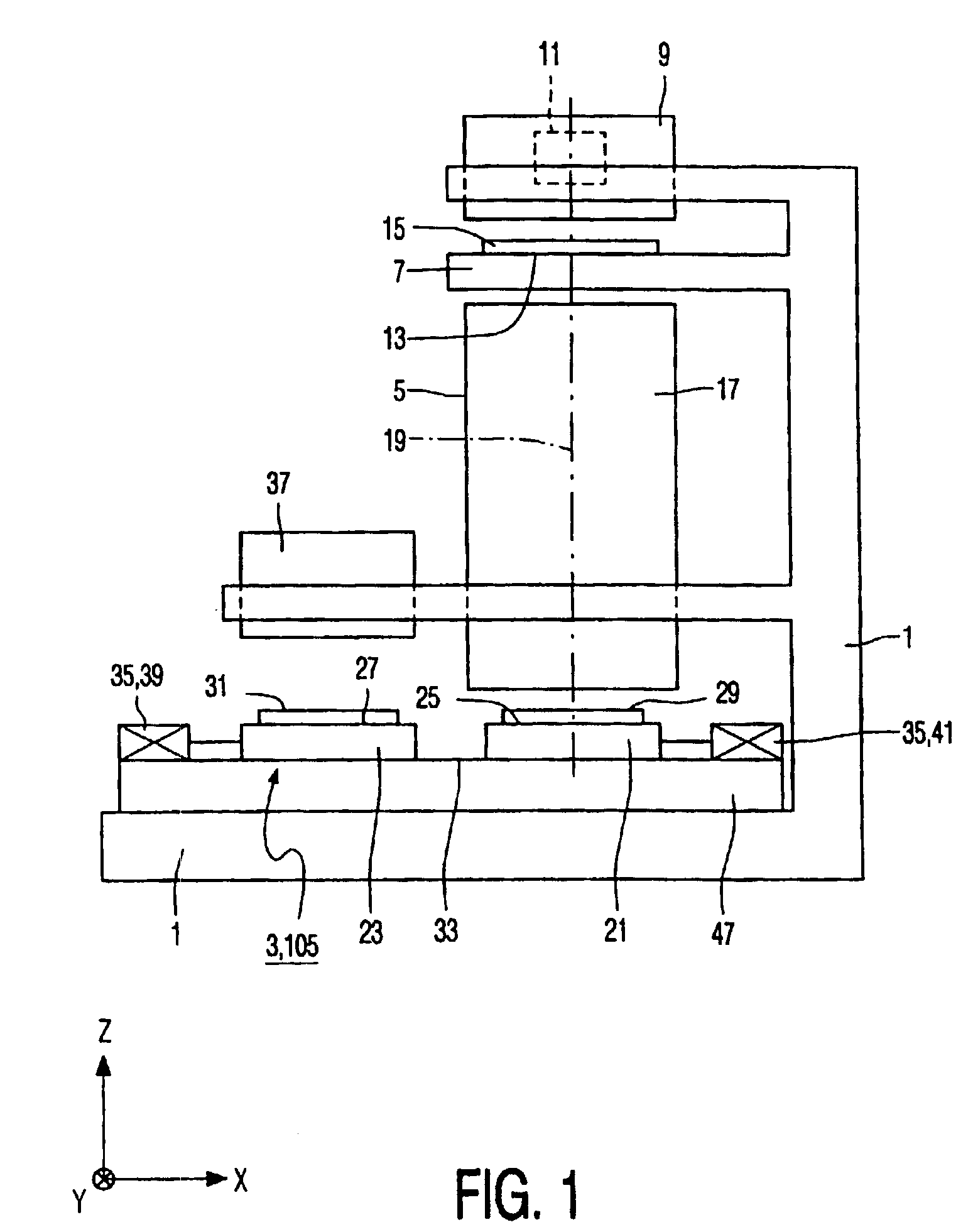

Positioning device having two object holders

InactiveUSRE40043E1Easy to adjustEasy constructionSemiconductor/solid-state device manufacturingInstrumental componentsEngineeringSemiconductor

A positioning device has first and second object holders that are guided over a guiding surface extending parallel to an X-direction and parallel to a Y-direction perpendicular to the X-direction and which are displaceable over the guiding surface from a first position into a second position by means of a displacement system. The displacement system includes a first displacement unit and a second displacement unit to which the object holders can be alternately coupled. The first displacement unit is suitable for carrying out a first series of positioning steps of the first object holder in the first position and for displacing the first object holder from the first position into an intermediate position between the first and second positions. The second displacement unit is suitable for carrying out a second series of positioning steps of the second object holder in the second position, simultaneously with and independently of the first displacement unit, and for displacing the second object holder from the second position into the intermediate position. In the intermediate position, the object holders are exchanged, after which the first series of positioning steps can be carried out by the first displacement unit with the second object holder in the first position and the second series of positioning steps can be carried out by the second displacement unit with the first object holder in the second position. The positioning device is suitable for use in a lithographic device to carry out an exposure process with a first semiconductor substrate in an exposure position and, simultaneously therewith and independently thereof, a characterization process with a second semiconductor substrate in a characterization position.

Owner:ASML NETHERLANDS BV

Liquid cell and passivated probe for atomic force microscopy and chemical sensing

ActiveUS20050199047A1Material analysis using sonic/ultrasonic/infrasonic wavesSurface/boundary effectAtomic force microscopyLiquid medium

The invention provides a liquid cell for an atomic force microscope. The liquid cell includes a liquid cell housing with an internal cavity to contain a fluid, a plurality of conductive feedthroughs traversing the liquid cell housing between the internal cavity and a dry side of the liquid cell, a cantilevered probe coupled to the liquid cell housing, and a piezoelectric drive element disposed on the cantilevered probe. The cantilevered probe is actuated when a drive voltage is applied to the piezoelectric drive element through at least one of the conductive feedthroughs. A method of imaging an object in a liquid medium and a method of sensing a target species with the liquid cell are also disclosed.

Owner:BOARD OF RGT NEVADA SYST OF HIGHER EDUCATION ON BEHALF OF THE UNIV OF NEVADA RENO

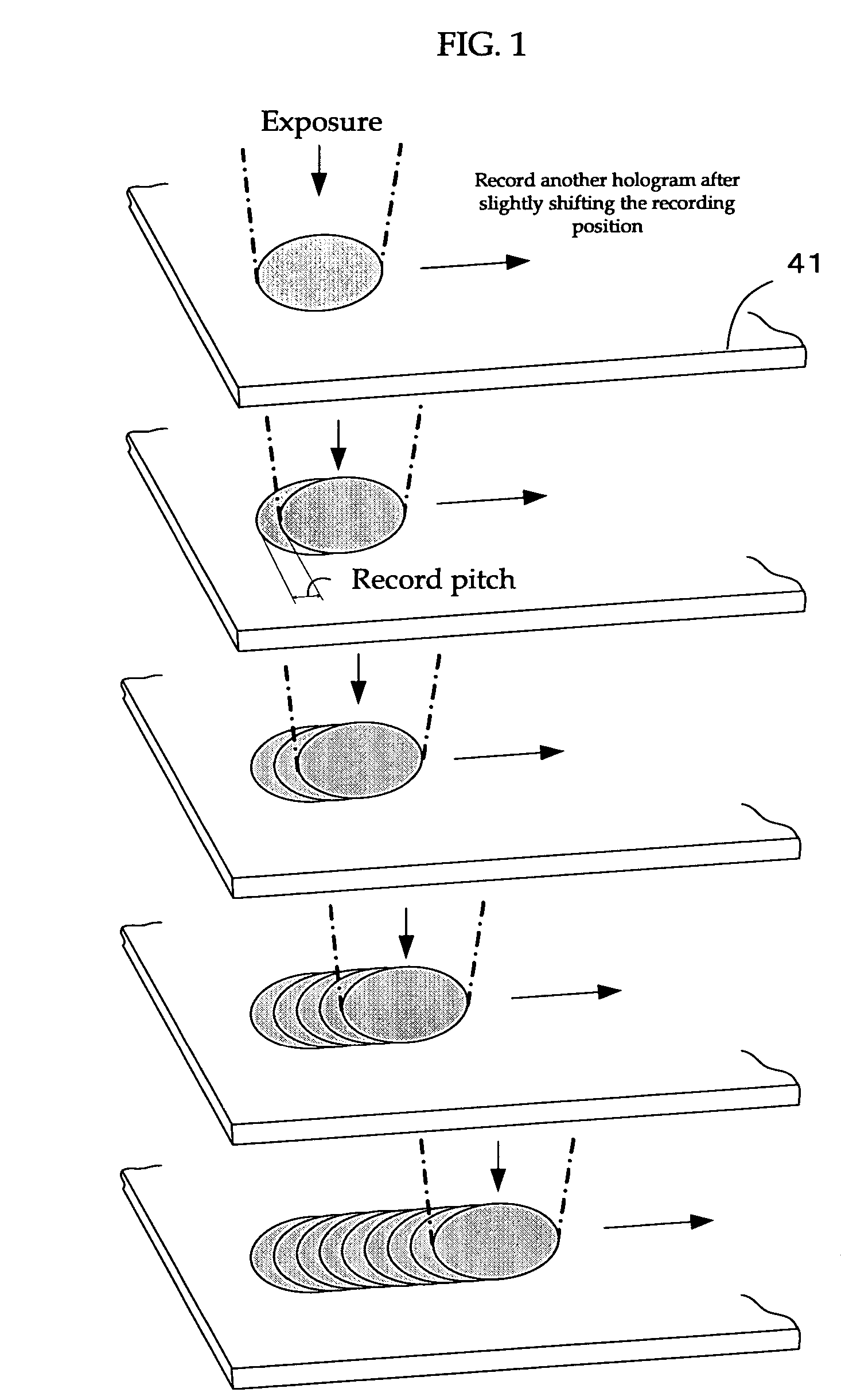

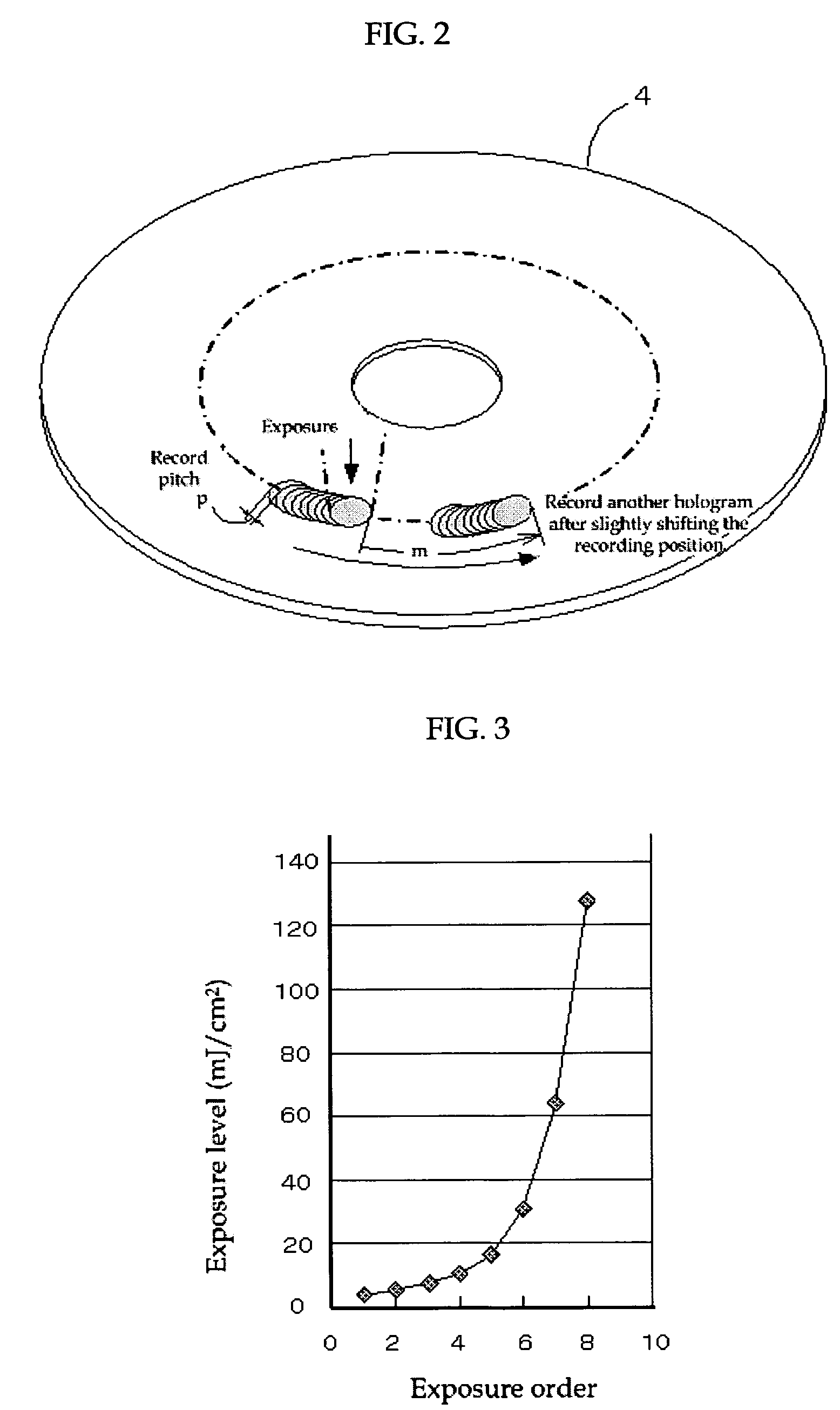

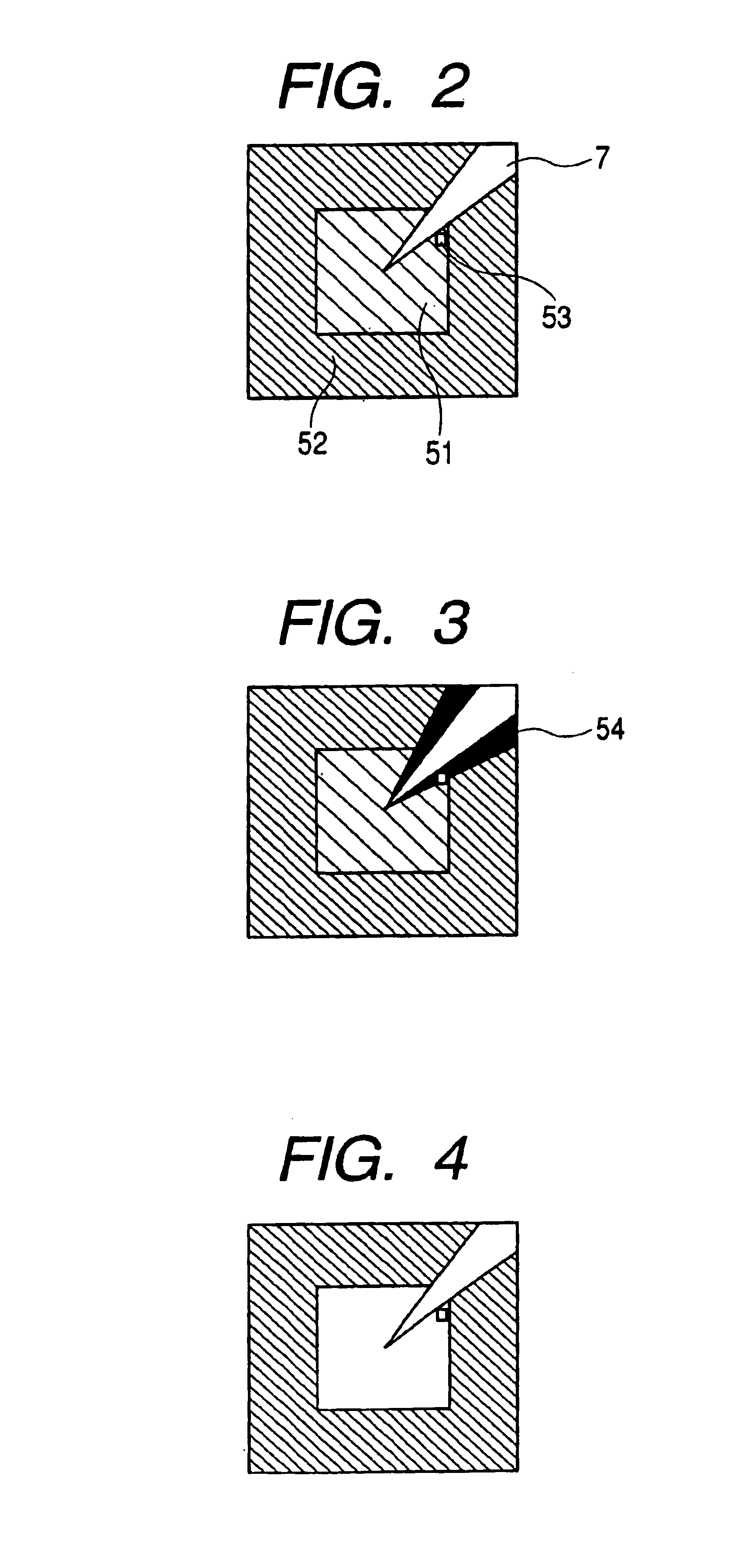

Optical information recording method, optical information recording apparatus and optical information recording medium

InactiveUS7626913B2Reduce sensitivitySufficient informationRecord information storageInstrumental componentsLight beamRecording layer

To provide an excellent optical information recording method, optical information recording medium and optical information recording apparatus both of which use the method. The method generates no excessively-exposed region, can sufficiently fix recorded information, and never reduce the sensitivity of non-recorded regions. This is achieved because the method applies a fixing beam onto at least a portion of an exposed region of a recording layer of the optical information recording medium, the recording layer recording information by holography, at an exposure level T (mJ / cm2) that satisfies the condition H<(S+T)<2H (where S is an integrated exposure level (mJ / cm2), which is the total of the exposure level in each predetermined region that constitutes the exposed region where an interference image has been recorded by irradiating the recording layer with an information beam and a reference beam, and H is a minimum fixing exposure level (mJ / cm2) required to fix the interference image).

Owner:FUJIFILM HLDG CORP

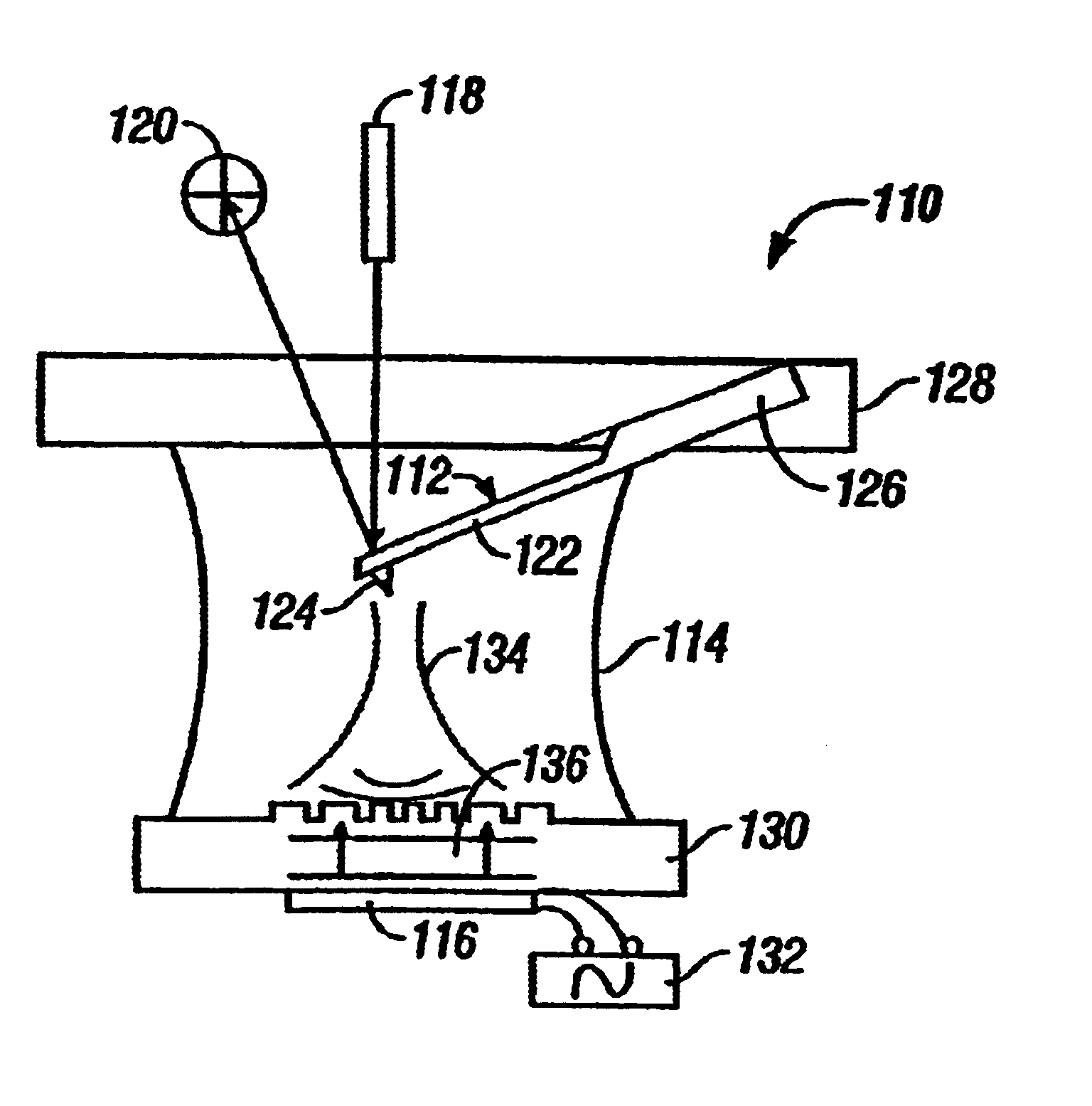

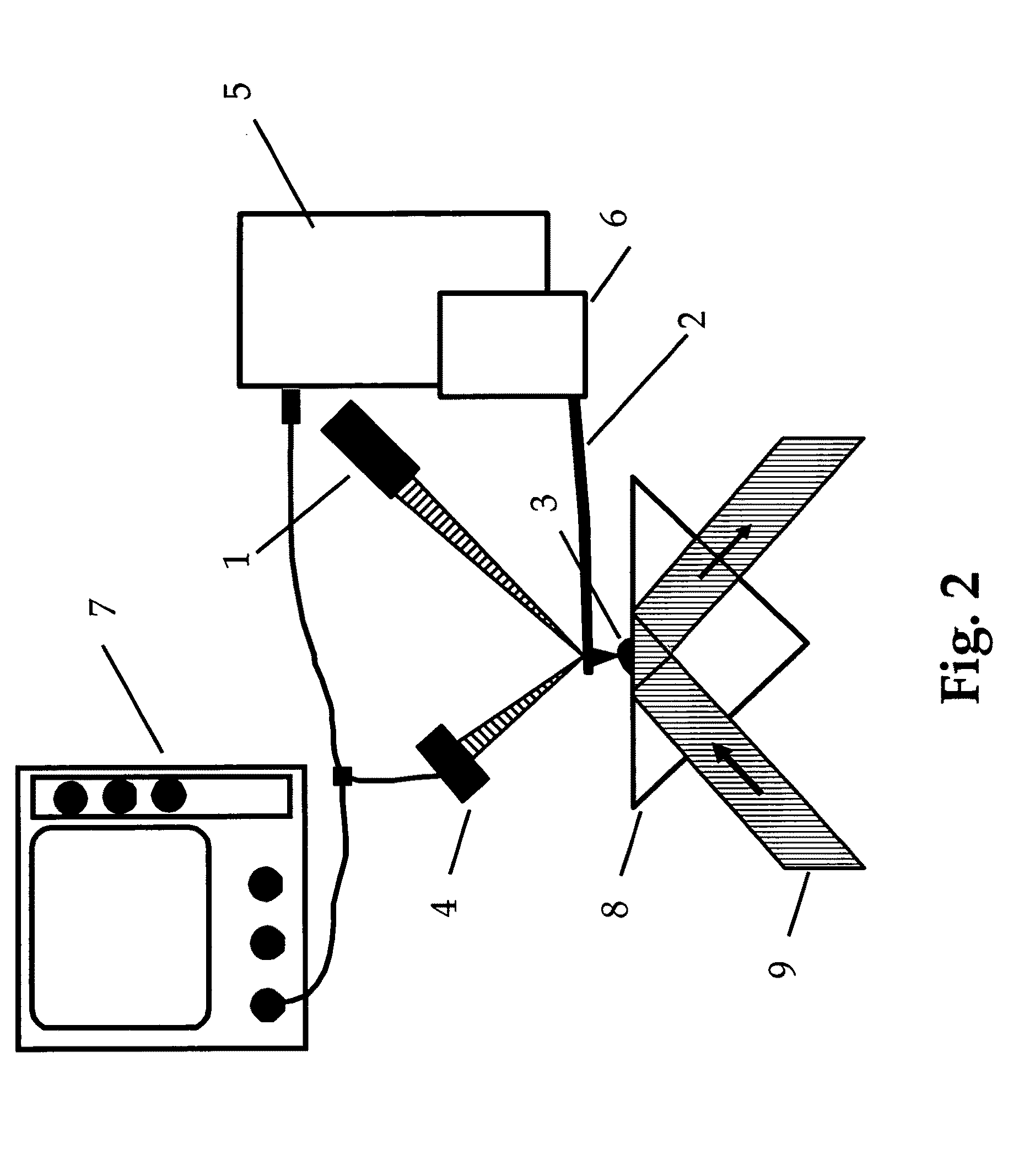

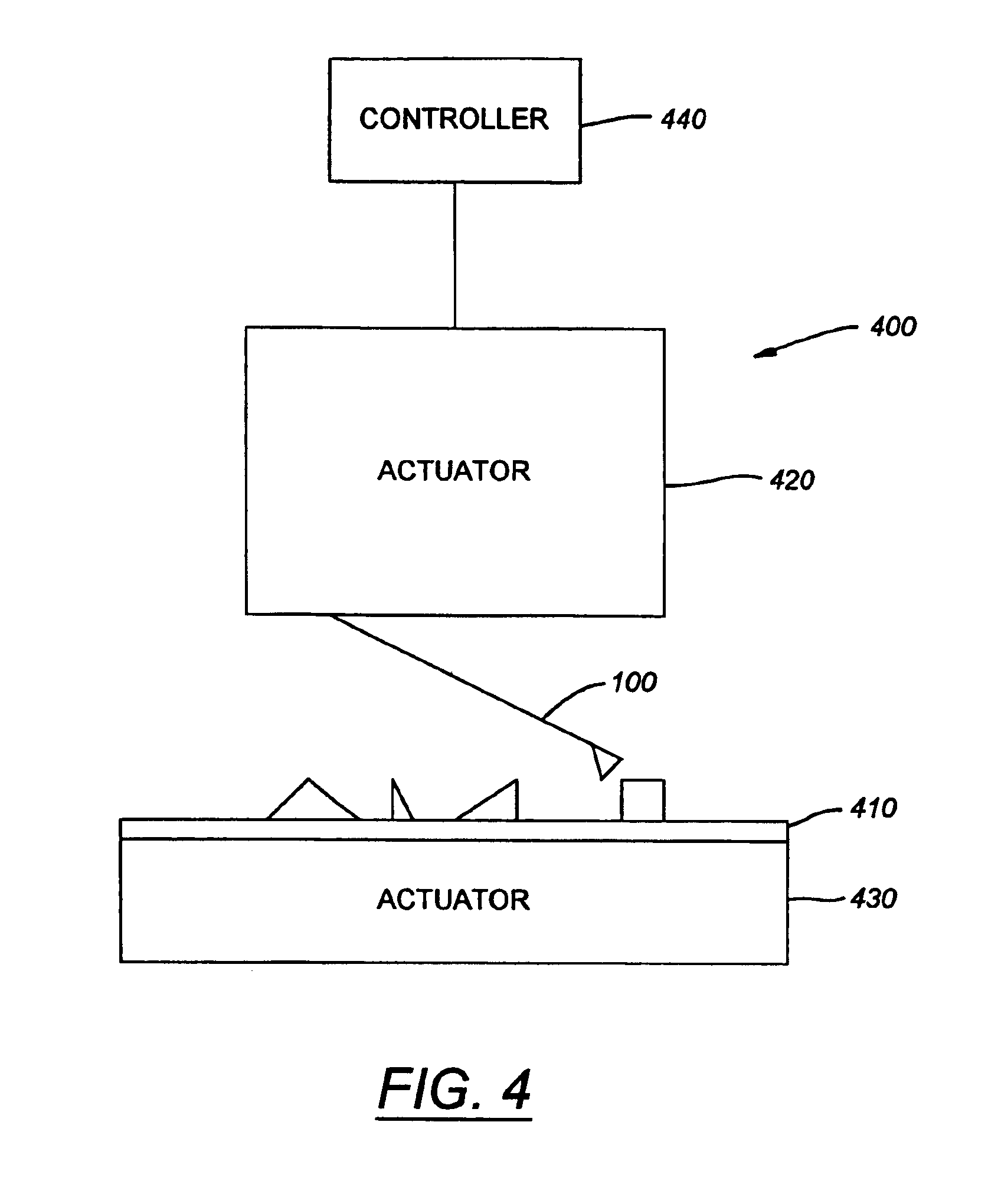

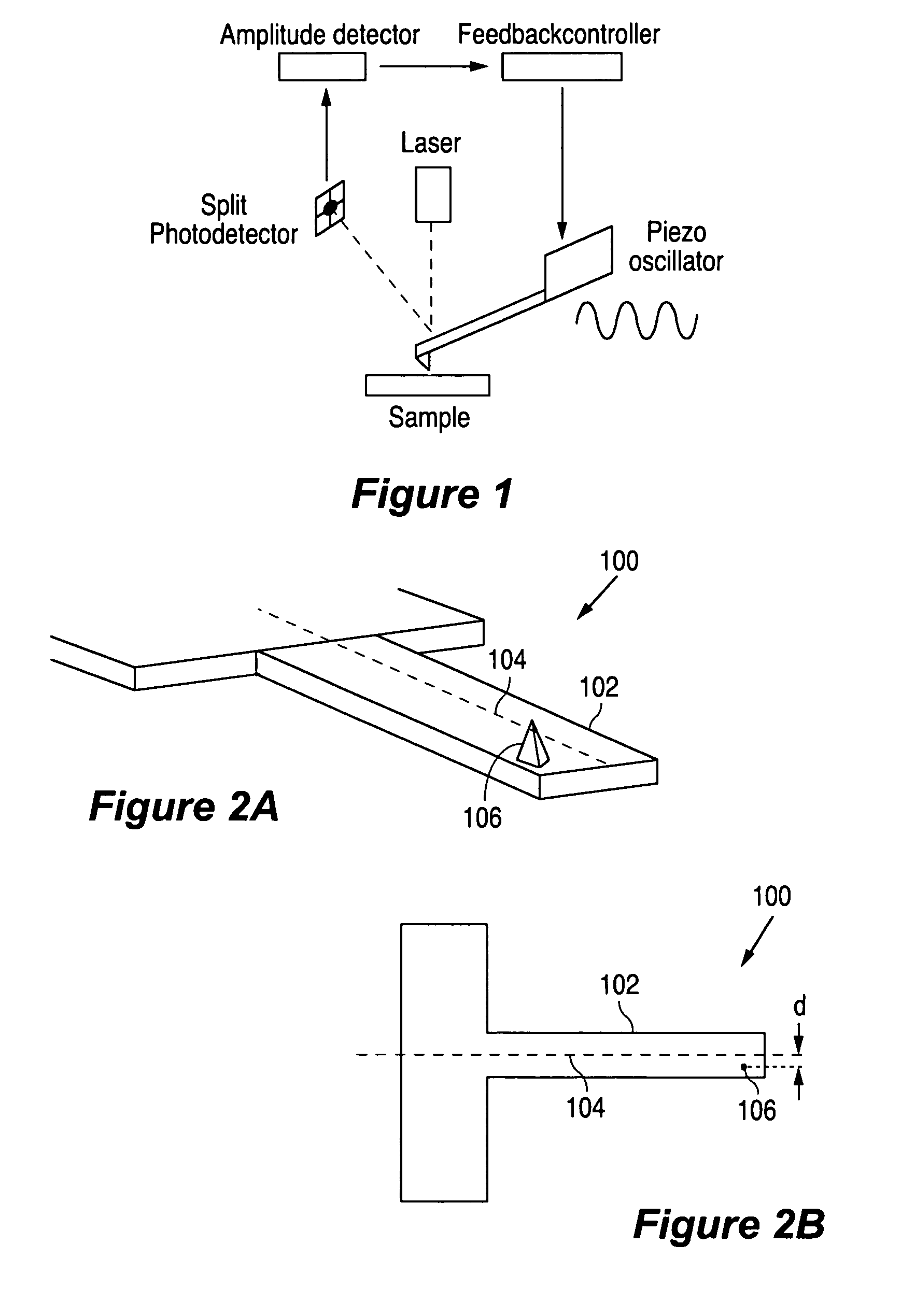

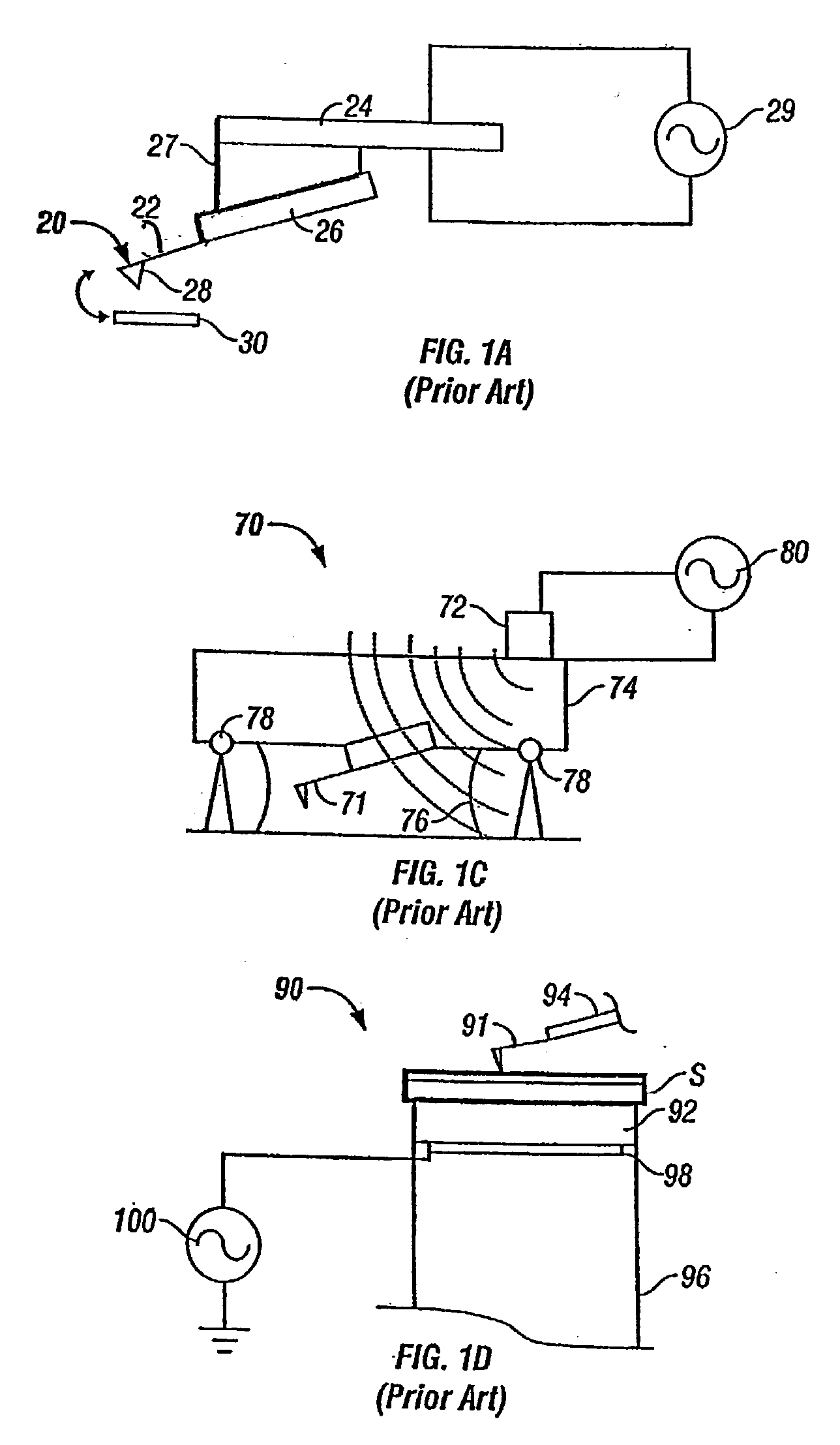

Method and apparatus for the ultrasonic actuation of the cantilever of a probe-based instrument

The cantilever of a probe-based metrology instrument such as an AFM is deflected by directing a beam of ultrasonic energy at the cantilever to apply ultrasonically generated acoustic radiation pressure to the cantilever. The energy is generated by an ultrasonic actuator such as a ZnO transducer driven by a power source such an RF signal generator. The transmitted beam preferably is shaped by focusing, collimation, or the like so that it impinges at least primarily on a region of interest of the cantilever such as the free end. The ultrasonic actuator produces a much better controlled force on the cantilever than can be achieved through the use of a traditional piezoelectric actuator and, accordingly, produces a response free of spurious effects (at least when the cantilever is operating in liquid). It also has a frequency bandwidth in the MHz range.

Owner:GEORGIA TECH RES CORP +1

High frequency deflection measurement of IR absorption

ActiveUS20090249521A1Discrimination evenEven identificationRadiation pyrometryMaterial analysis by optical meansIr absorptionComputational physics

An AFM based technique has been demonstrated for performing highly localized IR spectroscopy on a sample surface. Such a technique implemented in a commercially viable analytical instrument would be extremely useful. Various aspects of the experimental set-up have to be changed to create a commercial version. The invention addresses many of these issues thereby producing a version of the analytical technique that cab be made generally available to the scientific community.

Owner:BRUKER NANO INC

Scanning probe microscope probe with integrated capillary channel

InactiveUS20050236566A1Material nanotechnologyNanostructure manufactureCapillary channelScanning probe microscopy

A scanning probe microscope probe is disclosed. The scanning probe microscope probe includes a handle and a cantilever shank connected with the handle. The cantilever shank has at one end a base connected with the handle and at an opposing end a tip. The cantilever shank forms a capillary channel between the base to the tip of the cantilever shank.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

Integrated displacement sensors for probe microscopy and force spectroscopy

In accordance with an embodiment of the invention, there is a force sensor for a probe based instrument. The force sensor can comprise a detection surface and a flexible mechanical structure disposed a first distance above the detection surface so as to form a gap between the flexible mechanical structure and the detection surface, wherein the flexible mechanical structure is configured to deflect upon exposure to an external force, thereby changing the first distance.

Owner:GEORGIA TECH RES CORP

Method and apparatus for manipulating a sample

InactiveUS6862921B2Manipulation is accurateDoes not affect accuracyMaterial analysis using wave/particle radiationSurface/boundary effectCantileverBiomedical engineering

A method and apparatus for manipulating the surface of a sample including a cantilever, a first tip mounted on the cantilever, and a second tip mounted on the cantilever, the first and the second tip being configured to combine to form an imaging probe and to separate to form a manipulation probe. The first and second tips are configured to form a first position characterized in that the tips combine to form an imaging tip and the first and the second tip are configured to form a second position characterized in that the tips separate to manipulate particles on a surface of a sample. The tips can be configured to form the first position when a voltage is applied across the tips, and preferable extend downwardly from the cantilever substantially perpendicular thereto.

Owner:BRUKER NANO INC

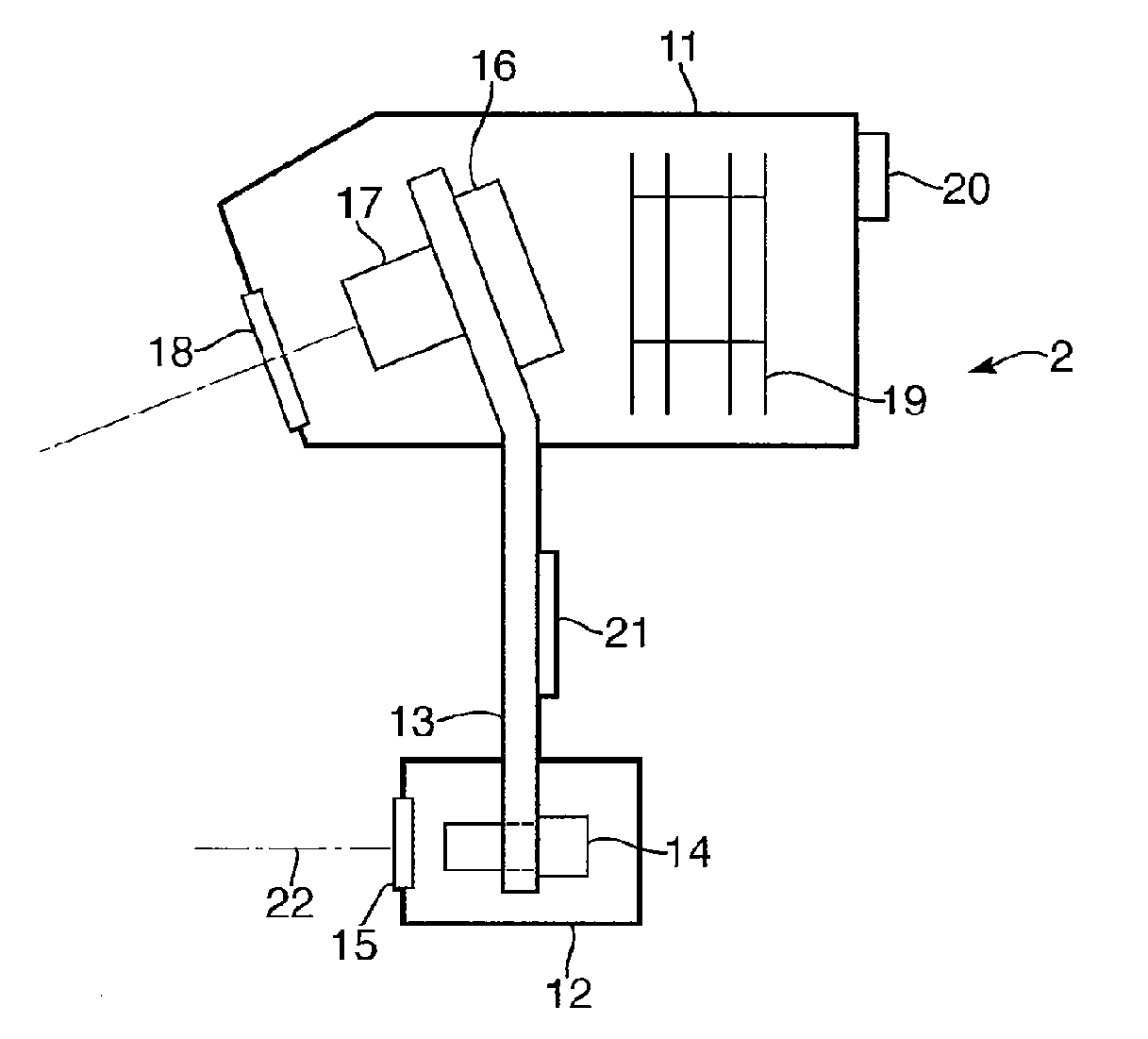

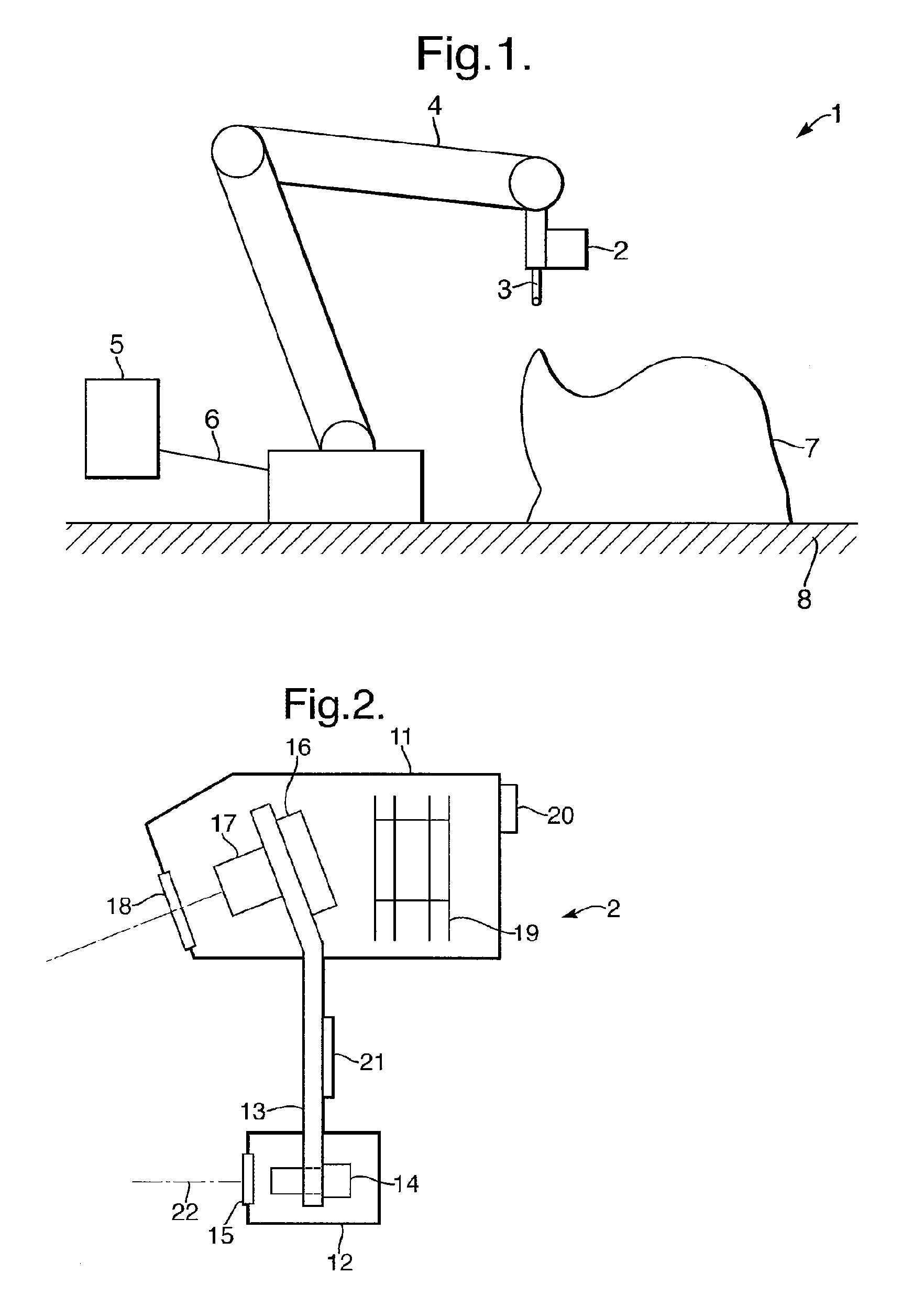

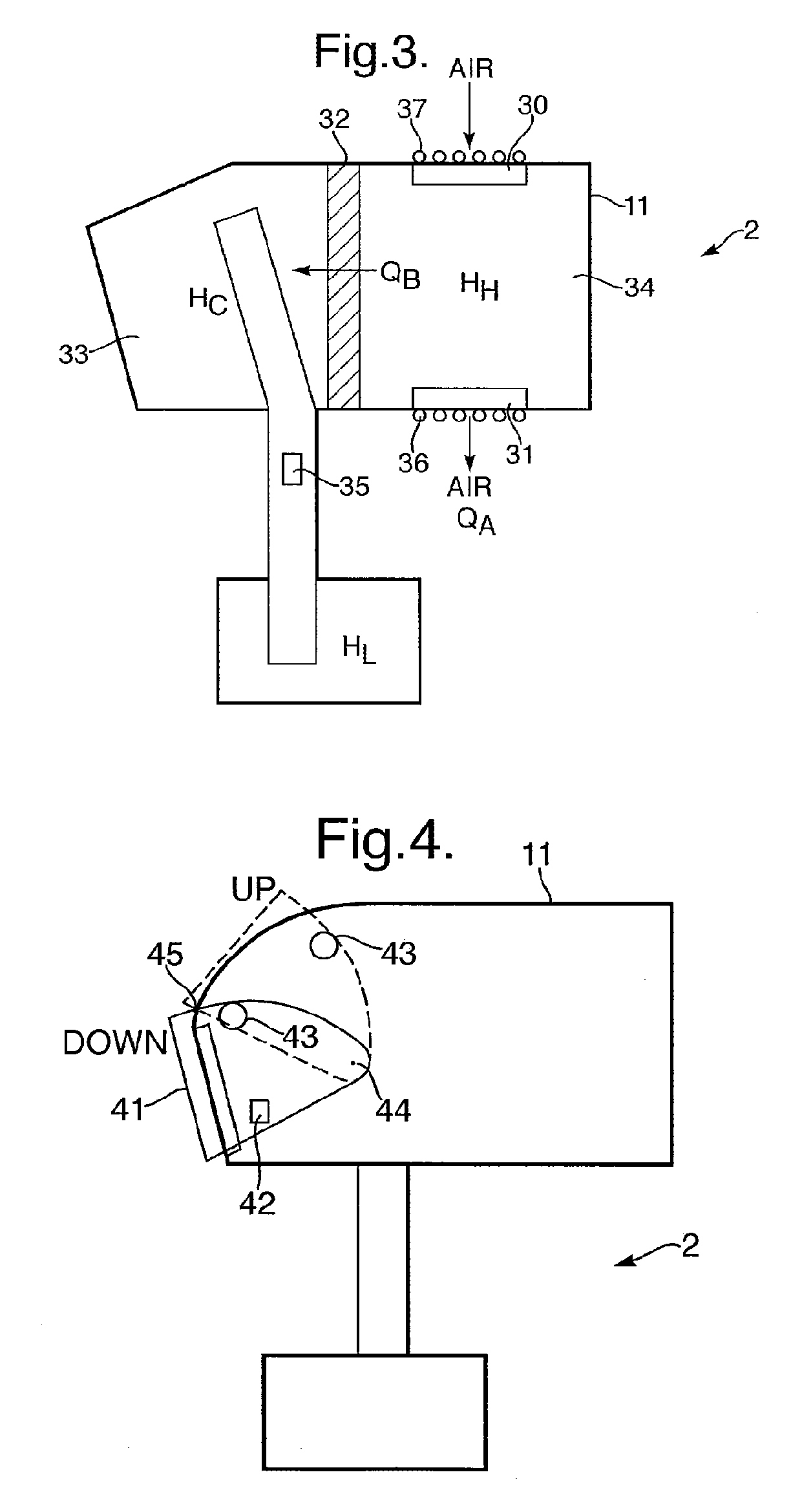

Optical Scanning Probe

ActiveUS20090205088A1Increase speedPointing accuratelyInstrumental componentsUsing optical meansUltimate tensile strengthOptical scanning

The present invention relates to a scanning probe (2) for capturing data from a plurality of points on the surface of an object by irradiating the object with a light stripe and detecting light reflected from the object surface, the scanning probe comprising (a) stripe generating means (14) for generating and emitting a light stripe (55); (b) a camera (16) comprising an imaging sensor having an array of pixels to detect the light stripe reflected from the object surface: (c) means for adjusting the intensity of the light stripe (55) during acquisition of the frame, in dependence upon the intensities detected by the camera (16). It also relates to a means to modify the stripe length, a scanner with separate compartment for the processing means, and an attachable dust cover for a scanner.

Owner:3D SCANNERS LTD

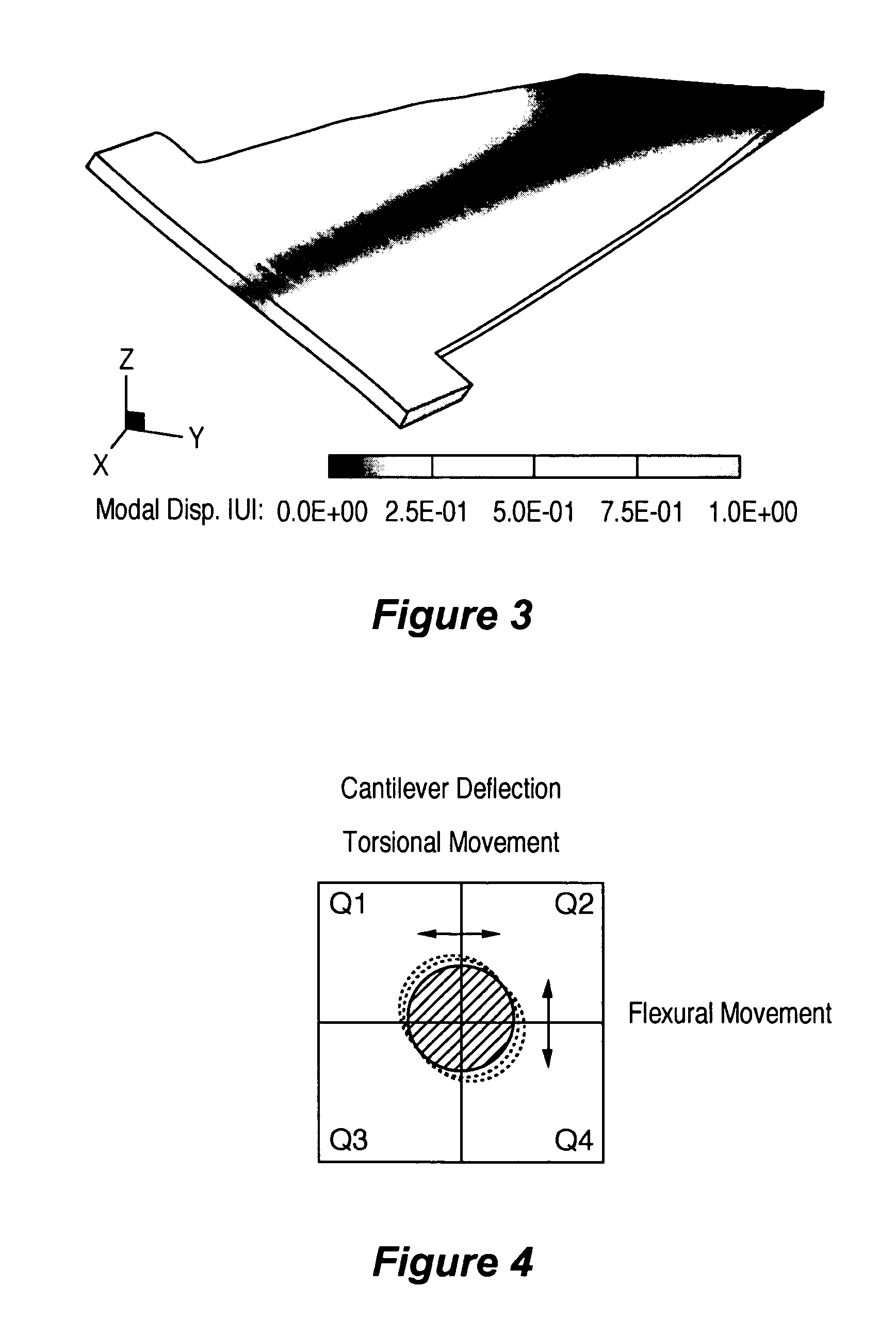

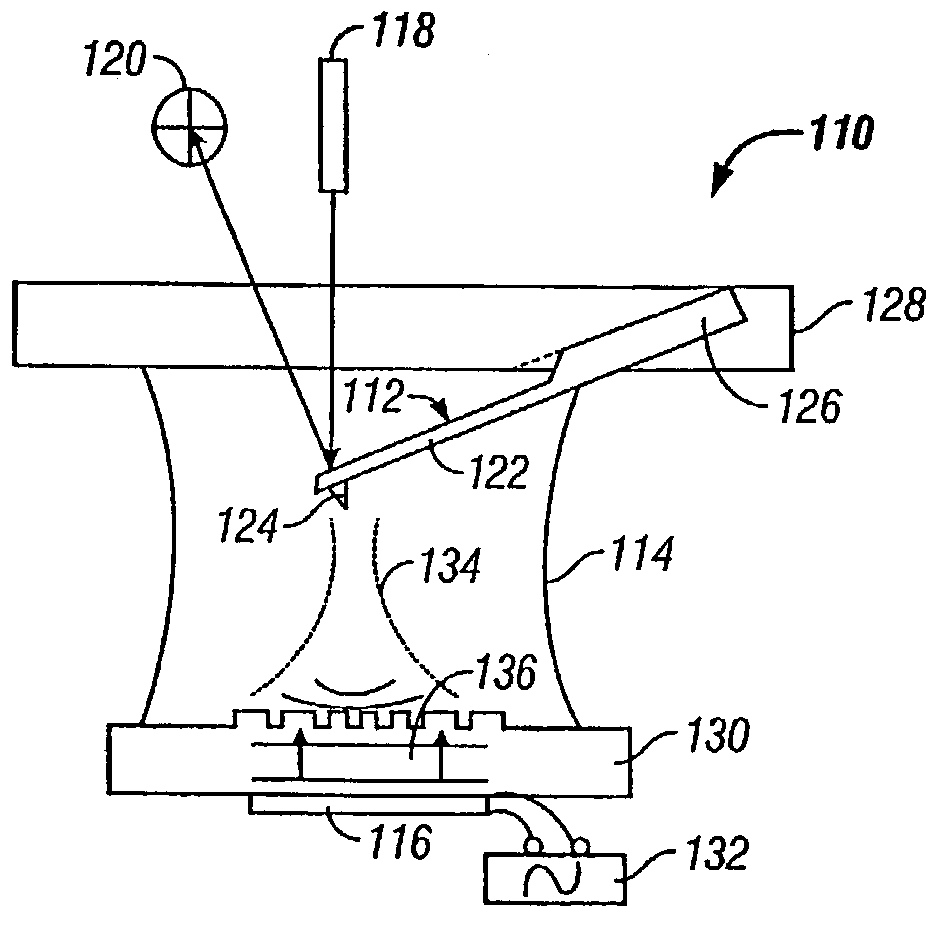

Torsional harmonic cantilevers for detection of high frequency force components in atomic force microscopy

InactiveUS7089787B2Fast response timeQuick checkForce measurement by measuring frquency variationsSurface/boundary effectAtomic force microscopyHarmonic

A cantilever for the use in atomic force microscopy includes a cantilever arm having a fixed end being attached to a base member and a free end where the cantilever arm has a first shape and an axis of torsion associated with the first shape, and a probe tip projecting from the cantilever arm near the free end where the probe tip is positioned in an offset displacement from the axis of torsion. Alternately, the cantilever arm has a first shape selected to tune a torsional resonance frequency of a selected torsional mode or the fundamental flexural resonance frequency of the fundamental mode so that the torsional resonance frequency and the fundamental flexural resonance frequency has an integer ratio. In this manner, the torsional motion of the torsional harmonic cantilever at that harmonic frequency will be largely enhanced by the corresponding torsional resonance.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

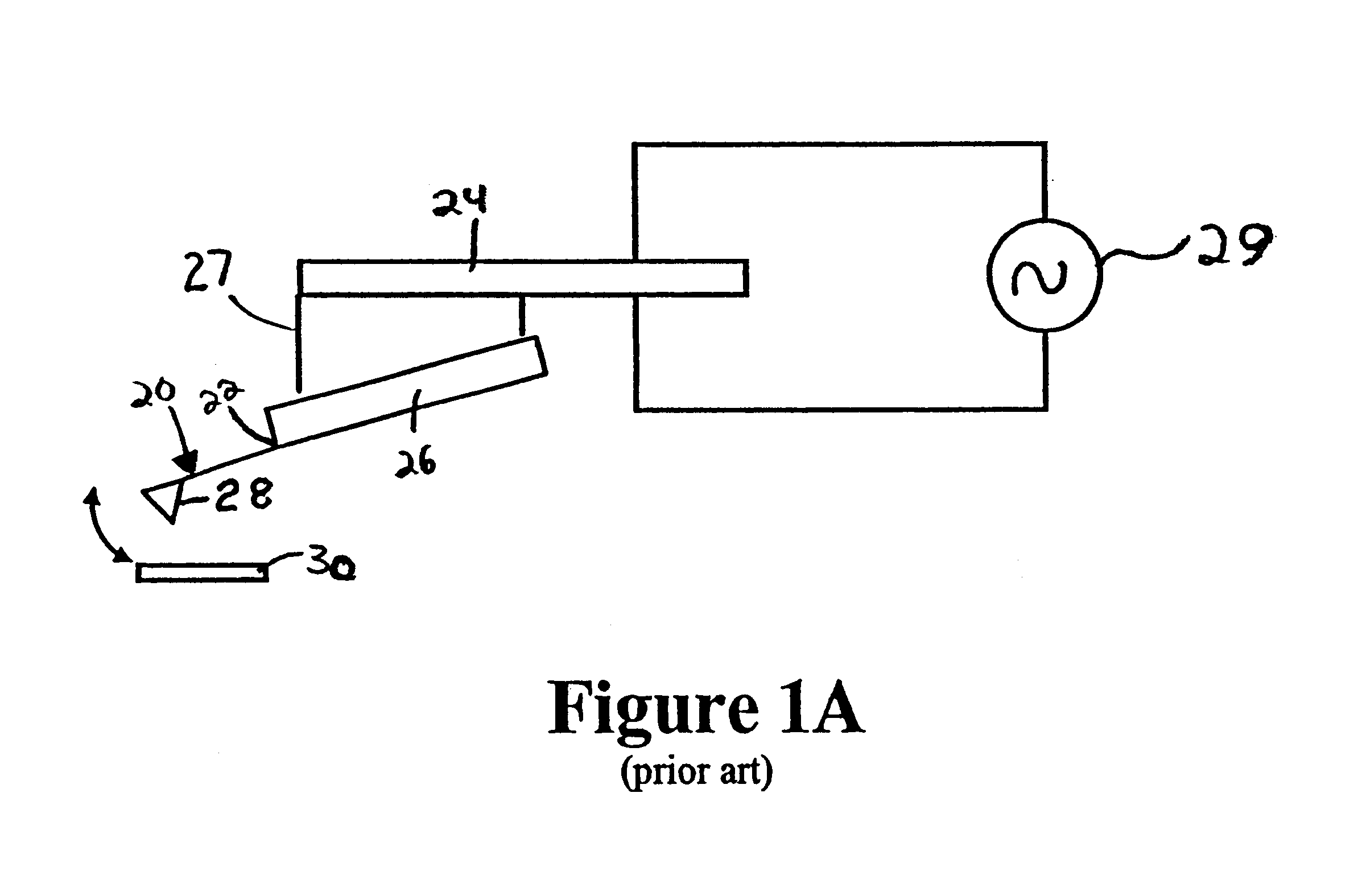

Method and apparatus for the actuation of the cantilever of a probe-based instrument

InactiveUS20040020279A1NanotechAnalysing solids using sonic/ultrasonic/infrasonic wavesResonanceCarrier signal

An electromagnetic drive causes a cantilever of a probe-based instrument to deform flexurally by transmitting a high frequency AC signal through an electromagnetic actuator located in the vicinity of the cantilever. The AC signal preferably is an RF carrier signal having a frequency that is substantially higher than the resonant frequency of the cantilever. The carrier signal may, if desired, be modulated with a lower frequency modulation signal to induce the cantilever to oscillate, preferably at resonance. Alternatively, the carrier signal may be transmitted to the electromagnetic actuator without being modulated in order to deflect the cantilever quasi-statically. Cantilever response can then be monitored either directly in response to the imposition of the electromagnetically induced deformation of the cantilever in response to probe / sample interaction to obtain measurements regarding characteristics of the sample, the environment, and / or the cantilever.

Owner:GEORGIA TECH RES CORP

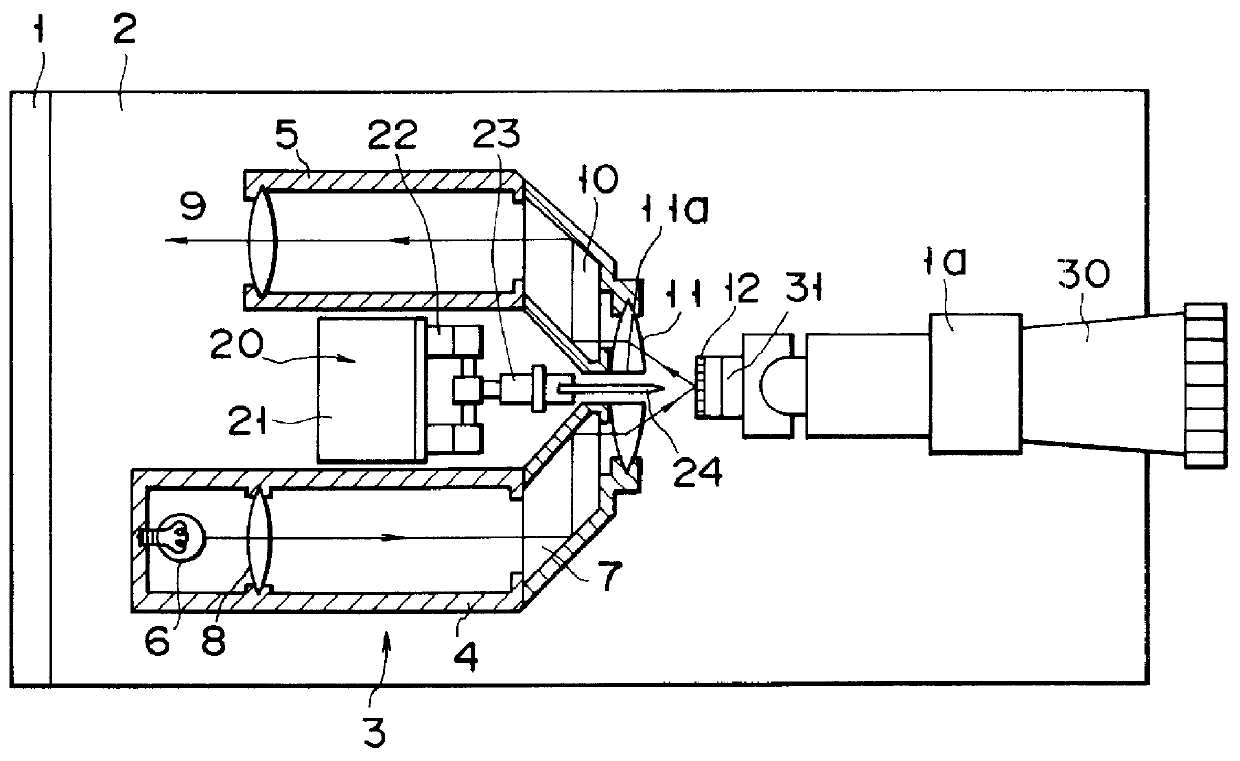

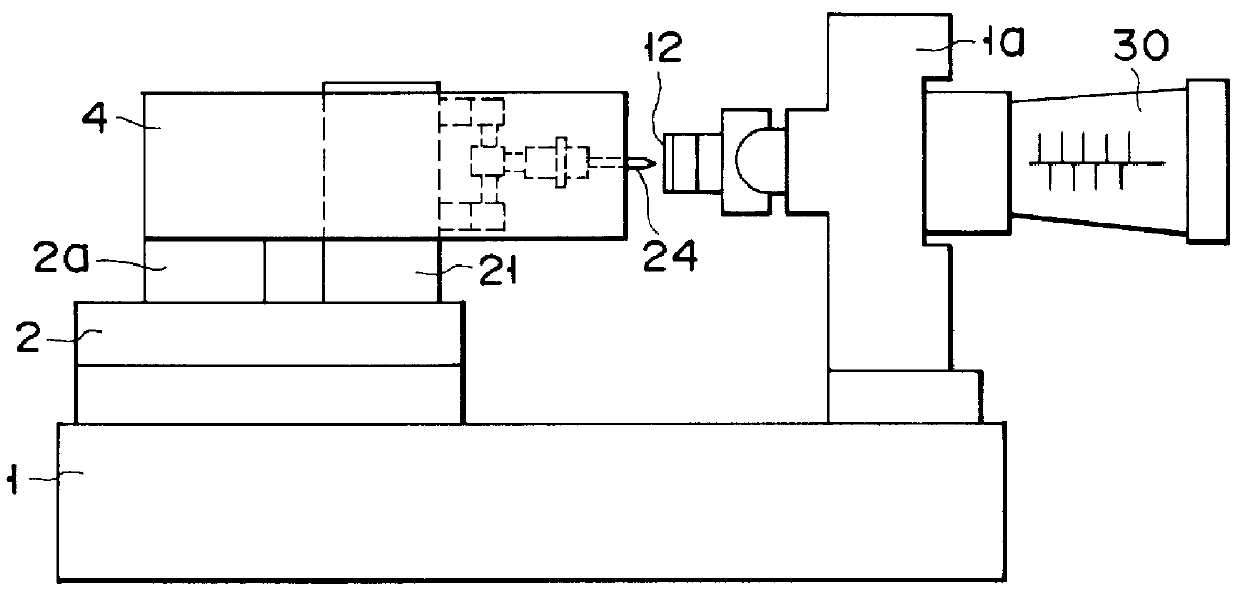

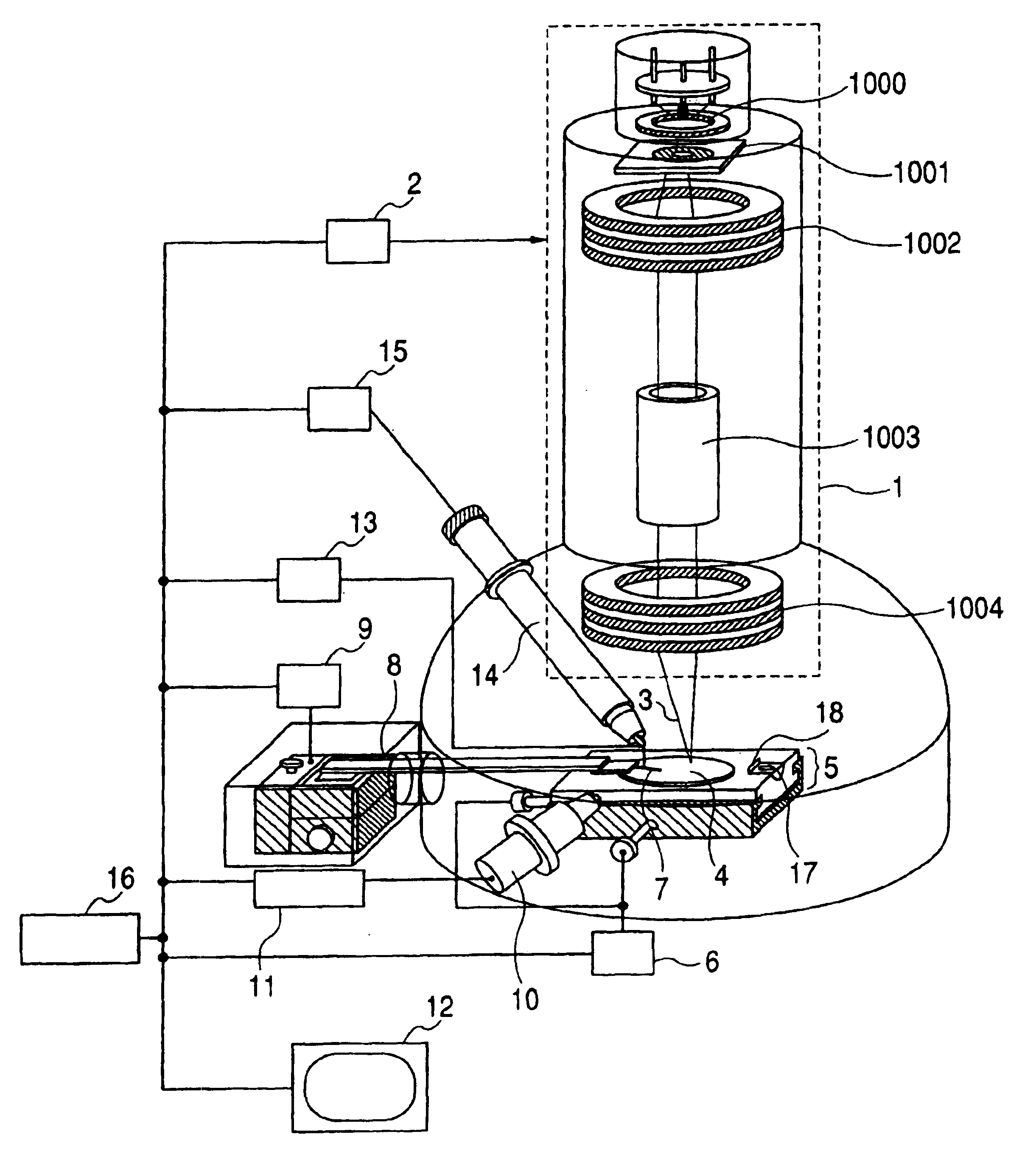

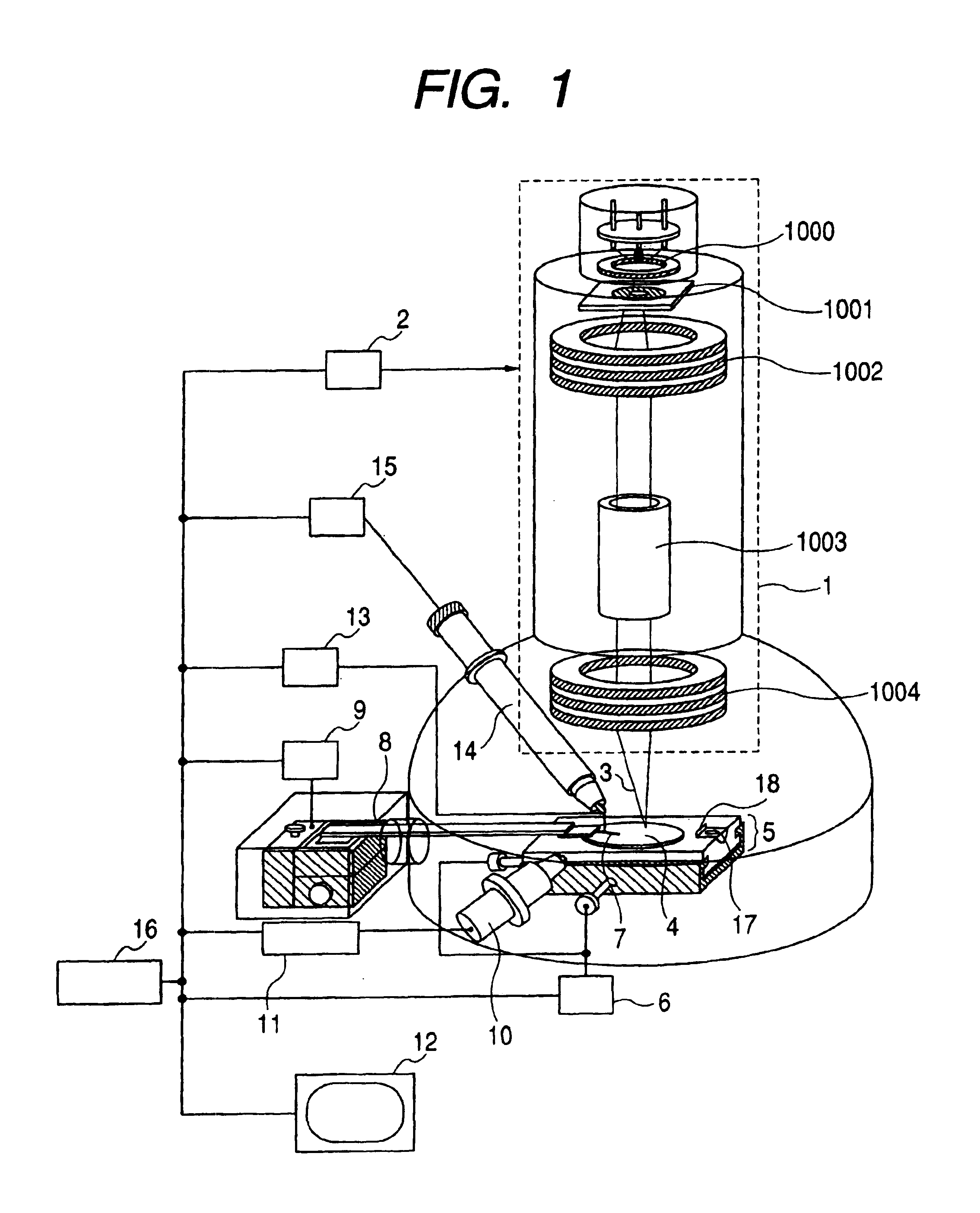

Scanning tunnel microscope

PCT No. PCT / JP88 / 00804 Sec. 371 Date Feb. 5, 1990 Sec. 102(e) Date Feb. 5, 1990 PCT Filed Aug. 12, 1988 PCT Pub. No. WO89 / 01603 PCT Pub. Date Feb. 23, 1989A scanning tunnel microscope is arranged by a combination of an optical microscope and a tunnel scanning unit. The scanning tunnel unit includes a probe held to be spaced apart from a sample placed on a sample table by a predetermined interval in an axial direction, and an actuator for axially moving the sample table and the probe to a tunnel region and relatively and three-dimensionally driving the sample table and the probe. An objective lens and the probe are arranged such that the axis of the probe of the scanning tunnel unit is aligned with an optical axis of the objective lens of the optical microscope. The sample and the probe are axially moved and brought into the tunnel region, and the sample is scanned in its surface direction while the sample and the probe are finely moved in the axial direction and a tunnel current is kept constant, thereby performing an STM observation of an observation surface of the sample. The objective lens of the optical microscope is axially moved to obtain an in-focus state, and the field of the STM observation surface is observed as an optical microscopic image through an eyepiece lens.

Owner:OLYMPUS OPTICAL CO LTD

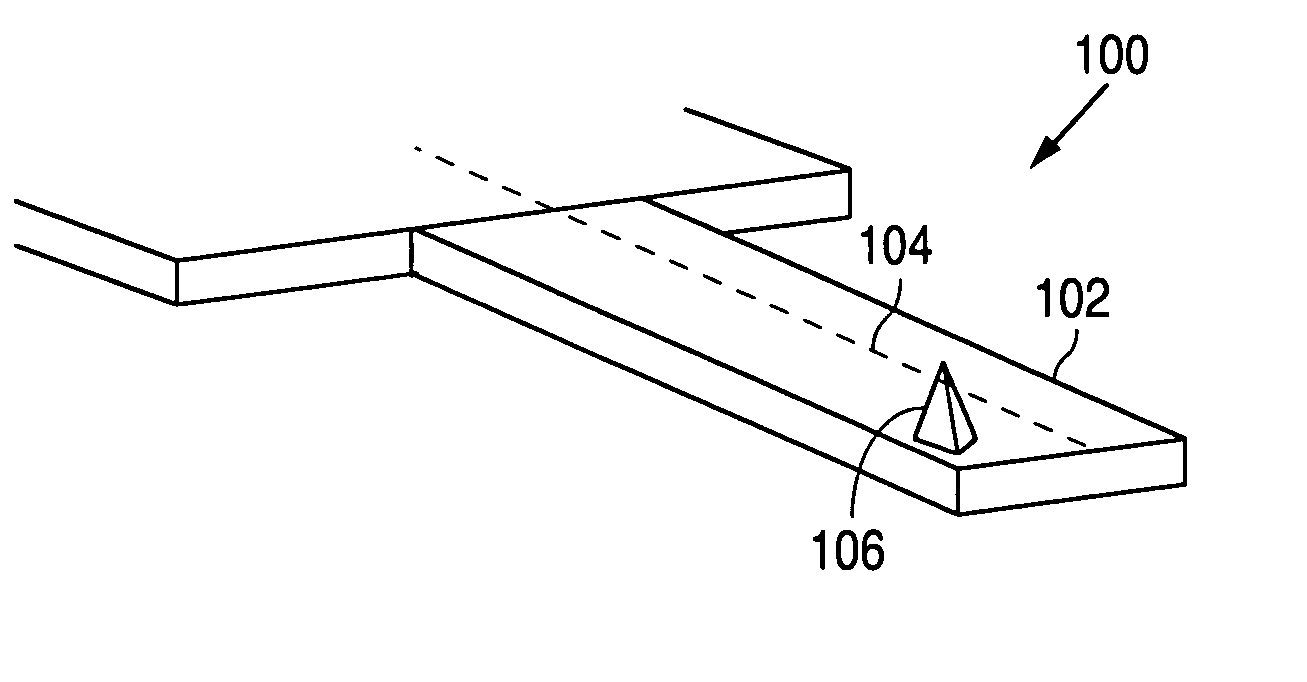

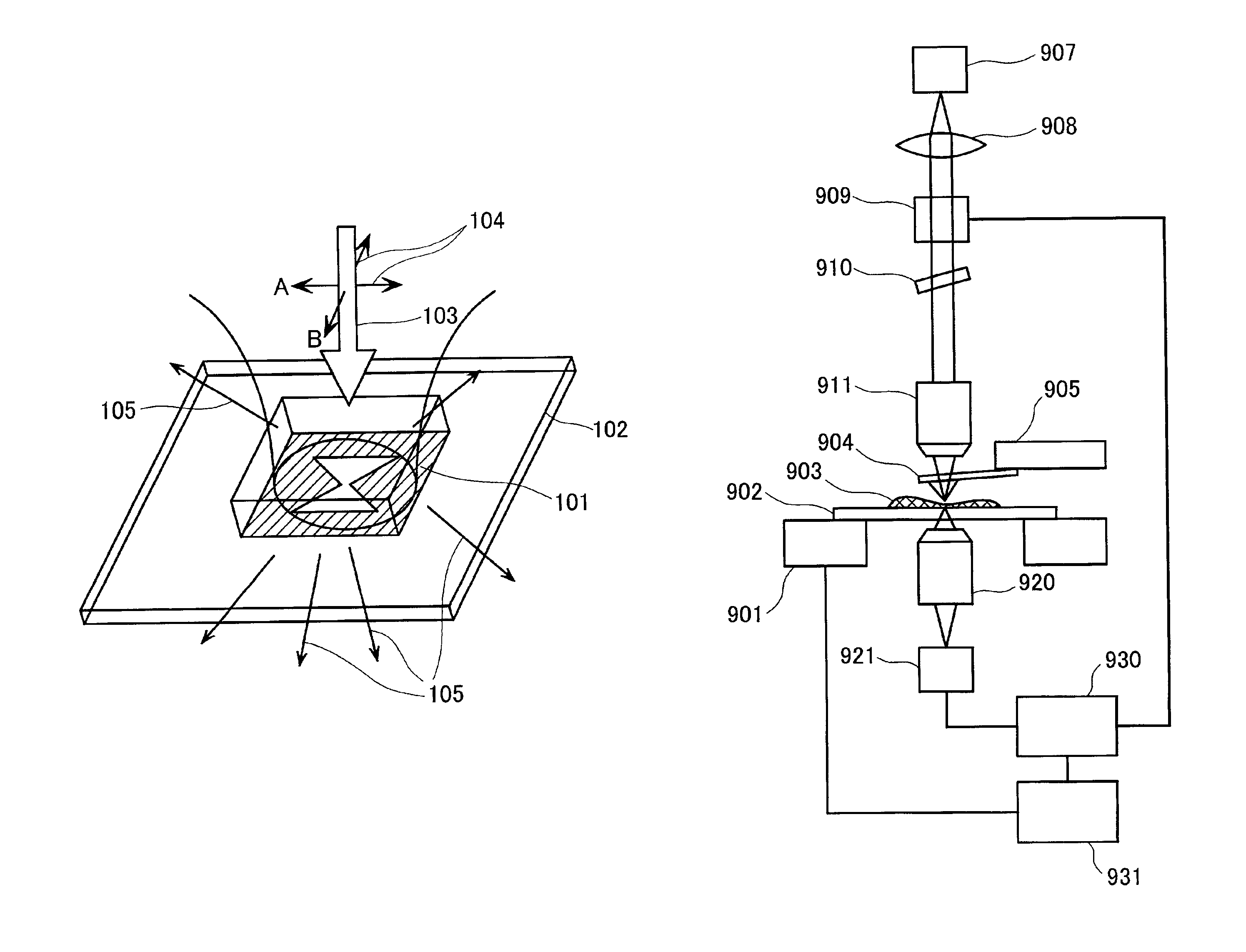

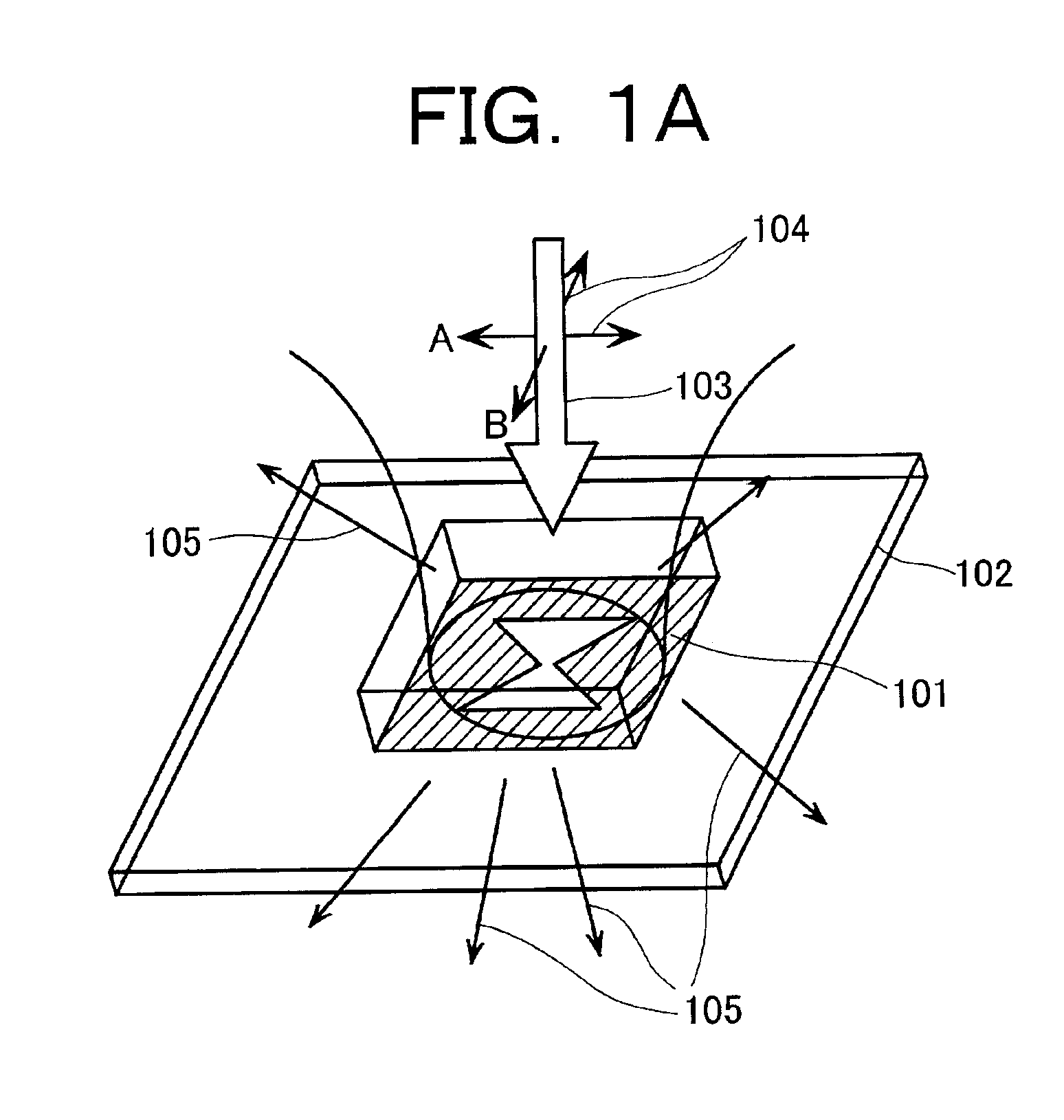

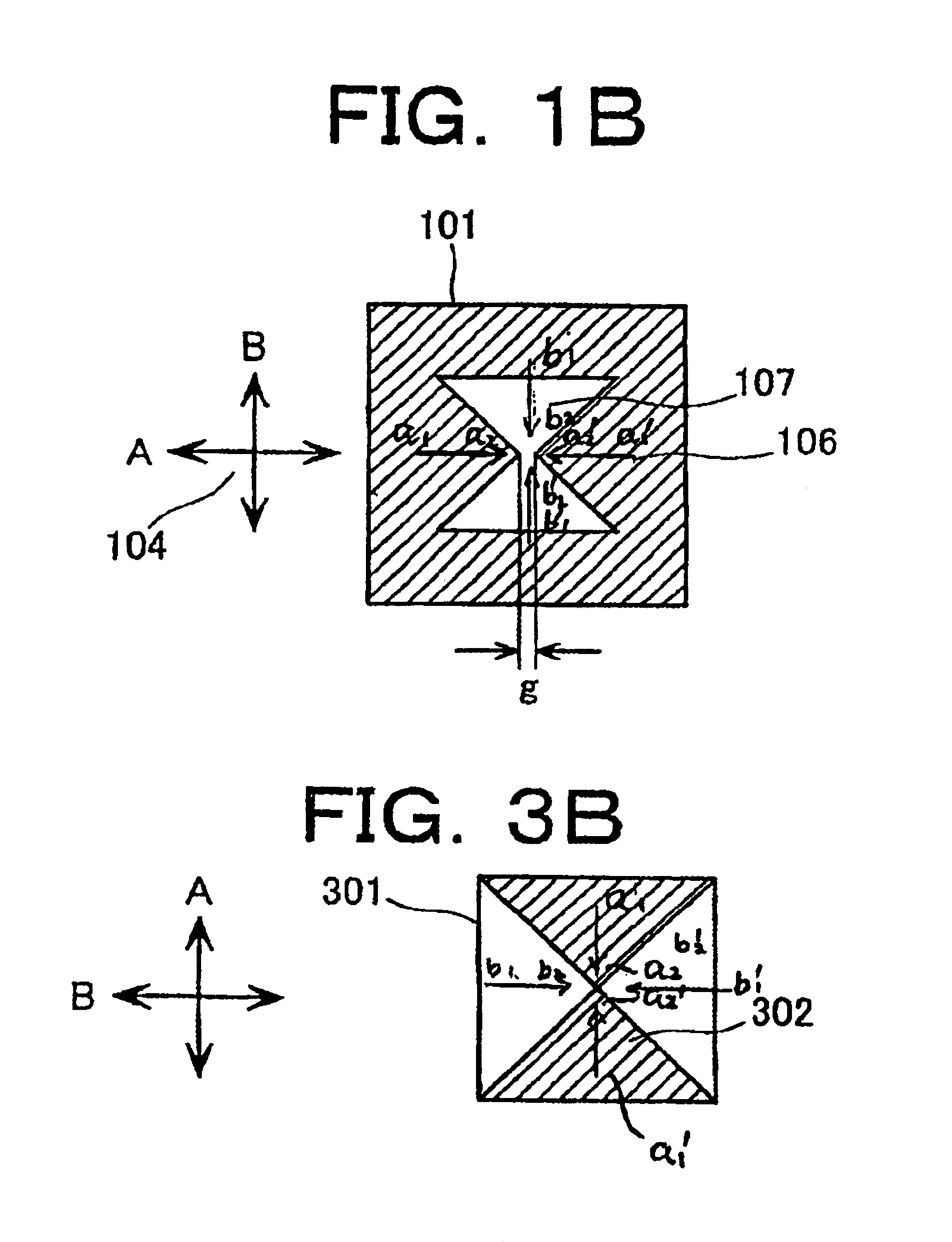

Optical apparatuses using the near-field light

InactiveUS6949732B2Improve signal-to-noise ratioSacrificing spatial resolutionMaterial analysis using wave/particle radiationBeam/ray focussing/reflecting arrangementsHigh spatial resolutionImage resolution

Optical apparatuses are provided that use near-field light, where high spatial resolution and high sensitivity are made compatible. Highly intense near-field light is generated in a narrow area using localized plasmons that are produced in a metal pattern 106 in a shape that bears anisotropy and is made to irradiate a measured subject. The direction of polarization 104 of incident light 103 is modulated and signal light is subjected to synchronous detection, so that background light is removed and high sensitivity is achieved.

Owner:HITACHI LTD

Multiple-source arrays with optical transmission enhanced by resonant cavities

InactiveUS6847029B2Altered propertySpread the wordBeam/ray focussing/reflecting arrangementsMaterial analysis by optical meansResonant cavityOptical cavity

A multiple source array for illuminating an object including: a reflective mask having an array of spatially separated apertures; at least one optic positioned relative to the mask to form an optical cavity with the mask; and a source providing electromagnetic radiation to the optical cavity to resonantly excite a mode supported by the optical cavity, wherein during operation a portion of the electromagnetic radiation built-up in the cavity leaks through the mask apertures towards the object.

Owner:ZETETIC INST

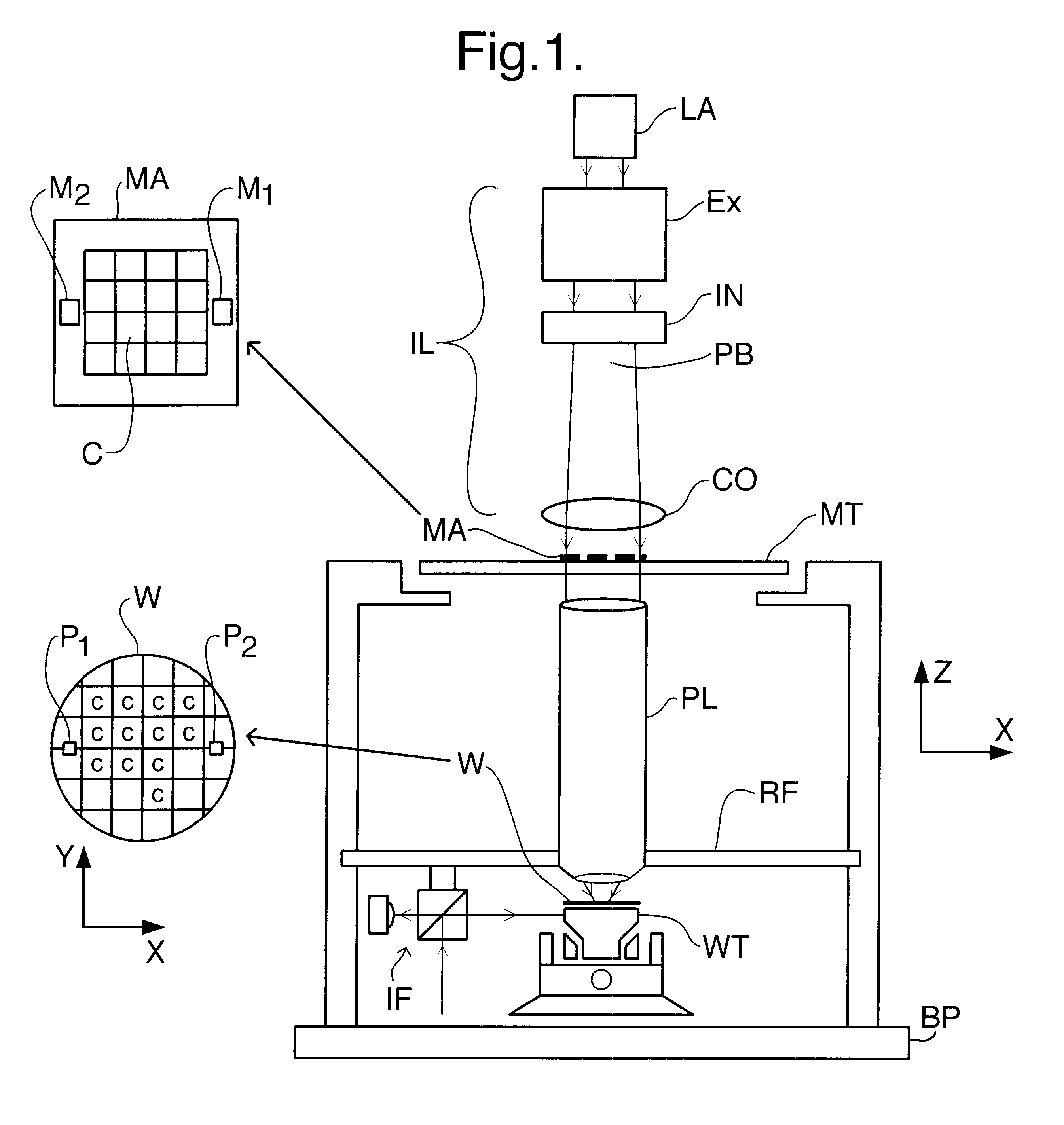

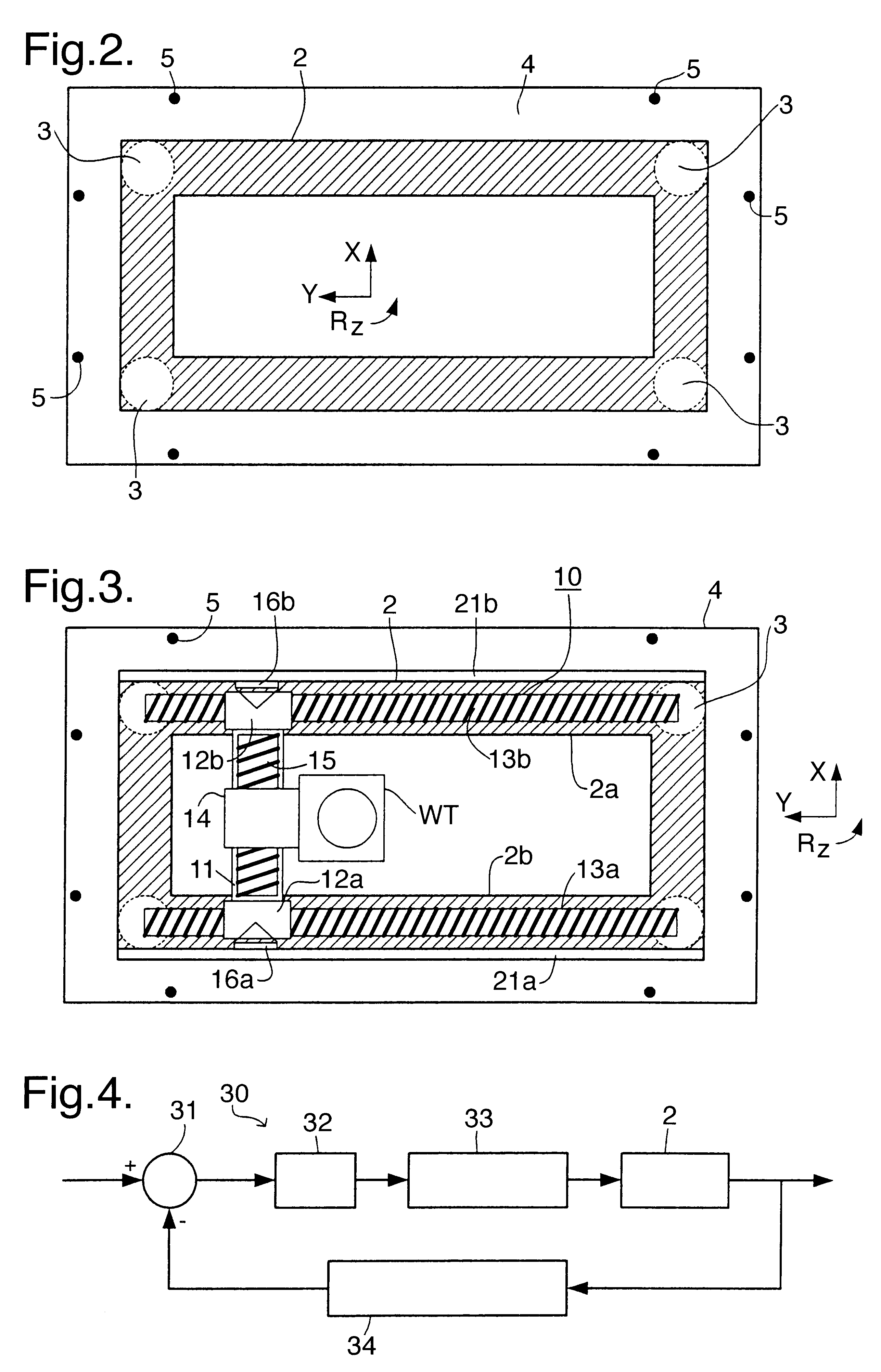

Balanced positioning system for use in lithographic apparatus

InactiveUS6525803B2Increase heightVibration minimizationPhoto-taking processesSemiconductor/solid-state device manufacturingThree degrees of freedomEngineering

A balanced positioning apparatus comprises a balance mass which is supported so as to be moveable in the three degrees of freedom, such as X and Y translations and rotation about the Z-axis. Drive forces in these degrees of freedom act directly between the positioning body and the balance mass. Reaction forces arising from positioning movements result in corresponding movement of the balance mass and all reaction forces are kept within the balanced positioning system. The balance mass may be a rectangular balance frame having the stators of two linear motors forming the uprights of an H-drive mounted on opposite sides. The cross-piece of the H-drive spans the frame and the positioned object is positioned within the central opening of the frame.

Owner:ASML NETHERLANDS BV

Probe driving method, and probe apparatus

InactiveUS6960765B2Easy to controlDecrease in luminanceSemiconductor/solid-state device testing/measurementInstrumental componentsIon beamSample image

A probe driving method and a probe apparatus for bringing a probe into contact with the surface of a sample in a safe and efficient manner by monitoring the probe height. Information about the height of the probe from the sample surface is obtained by detecting a probe shadow appearing immediately before the probe contacts the sample, or based on a change in relative positions of a probe image and a sample image that are formed as an ion beam is irradiated diagonally.

Owner:HITACHI LTD +1

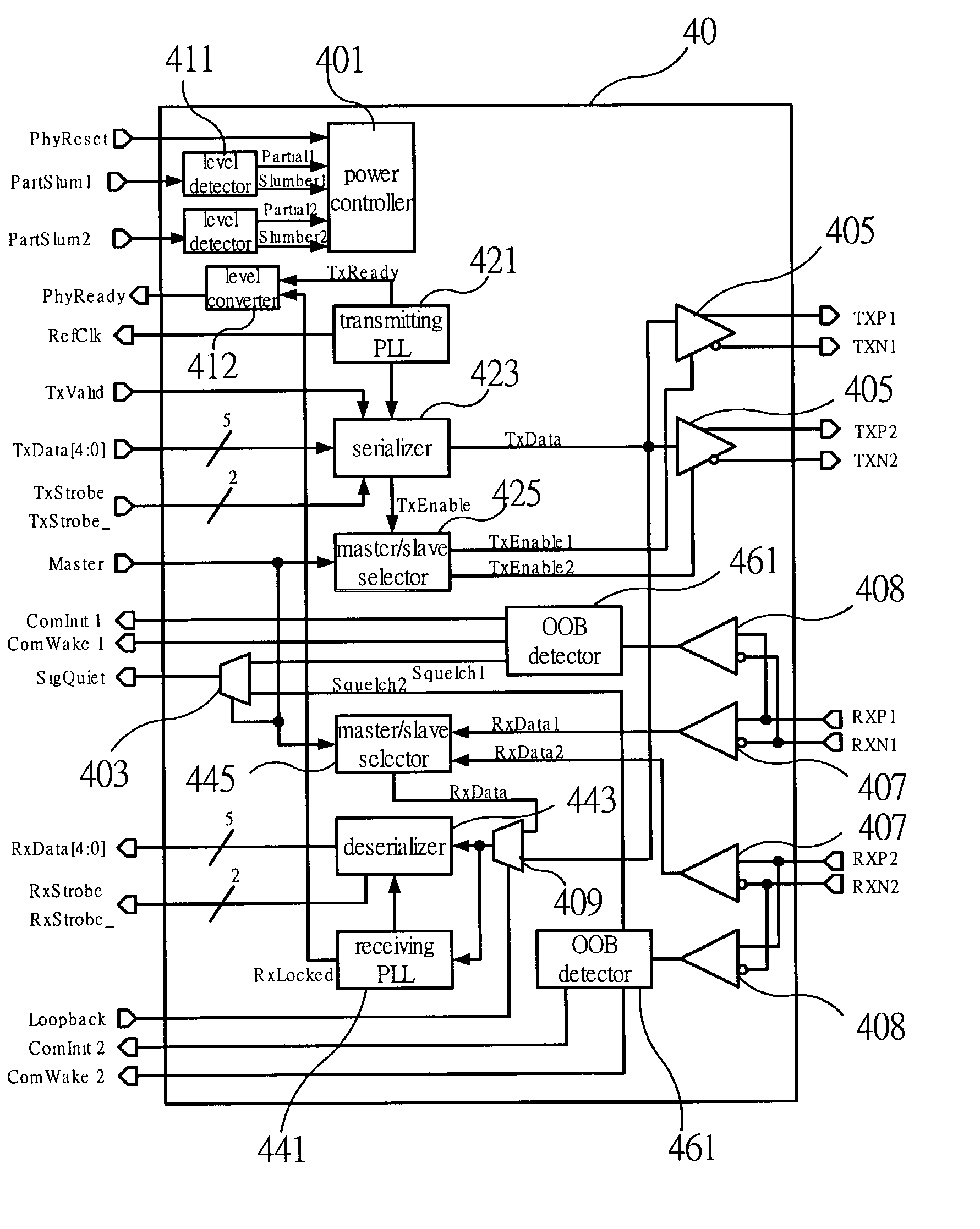

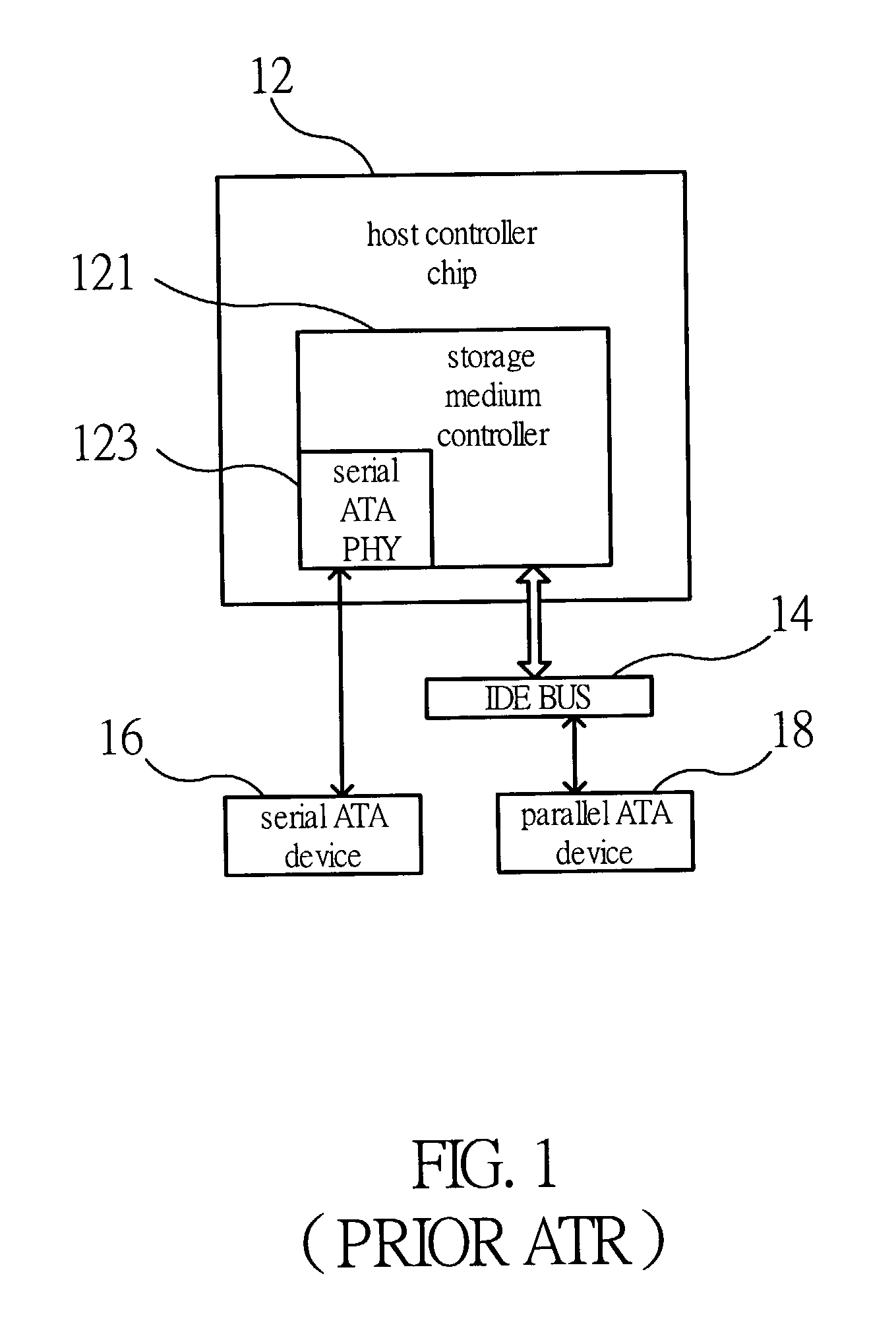

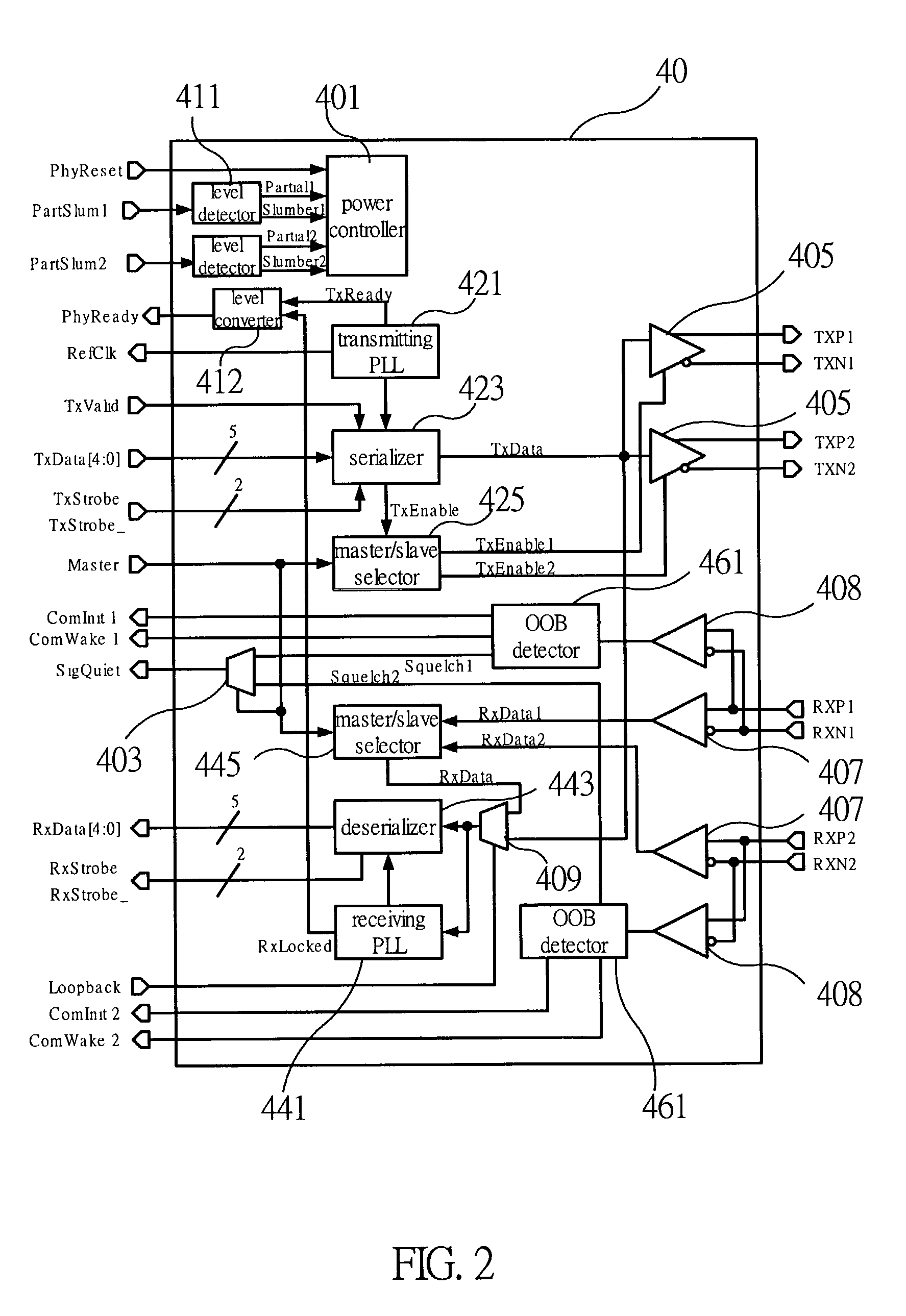

Circuit and signal encoding method for reducing the number of serial ATA external PHY signals

InactiveUS7020834B2Reduce in quantityMinimize the numberError preventionTransmission systemsControl signalData signal

A Circuit for reducing the number of serial ATA external PHY signals includes: a serializer / deserializer, connected to a storage medium controller through a set of parallel signal transmitting lines and a set of parallel signal receiving lines, so as to convert signals between parallel and serial specifications; a phase locked loop, connected to the serializer / deserializer so as to generate a clock signal required for data signal transmission; at least one pair of transmitter and receiver, each connected to the serializer / deserializer, each transmitter able to transmit the serial data signal from the serializer through a set of serial signal transmitting lines to a serial ATA device, and each receiver able to receive the serial data from the serial ATA device through a set of serial signal receiving lines to the deserializer; and at least one OOB signal detector, each connected to the corresponding receiving lines, so as to detect the out of band signals from the serial ATA device. The Circuit also employs in certain applications a signal encoding approach for reducing the number of serial ATA external PHY signals, wherein an encoder and a decoder are employed to encode control signals and status signals into special data codes transmitted between a serial ATA external PHY and a storage medium controller, so as to minimize the number of interface signals.

Owner:VIA TECH INC

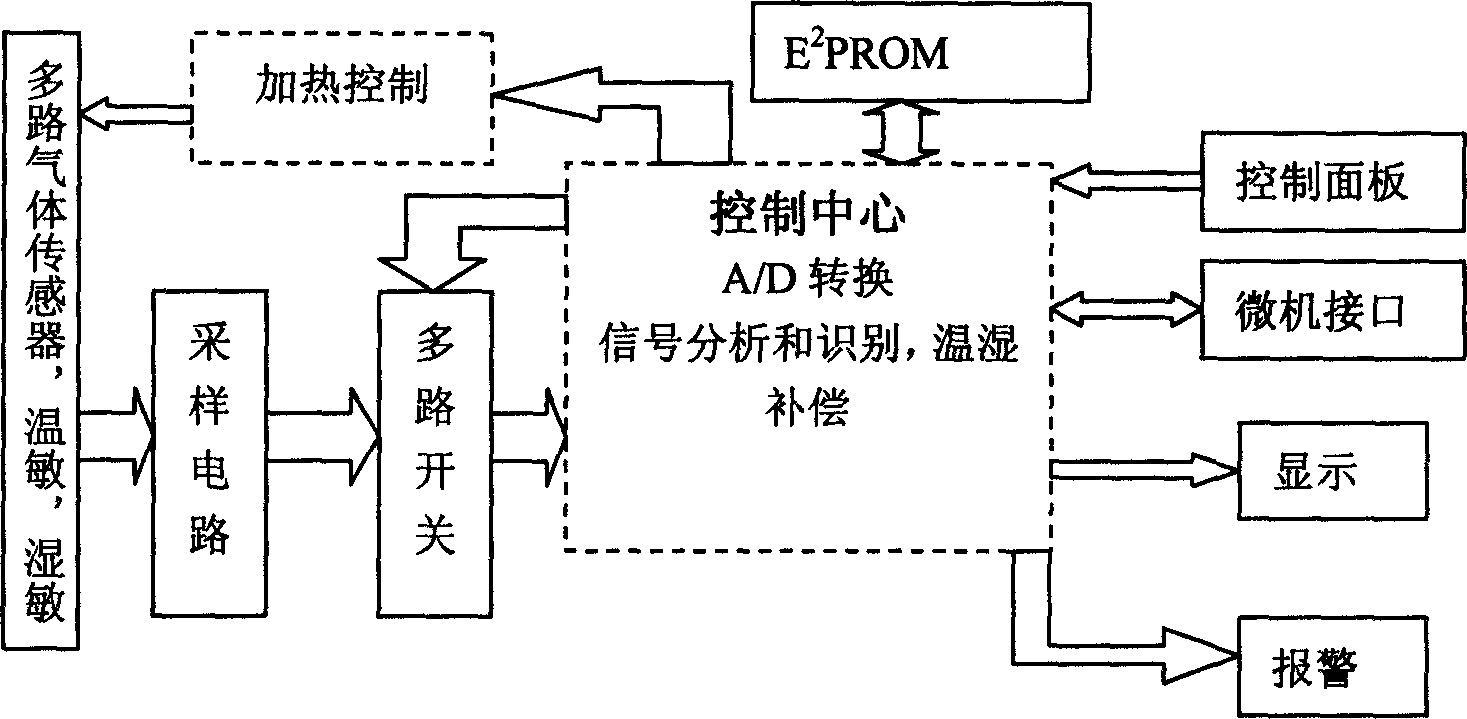

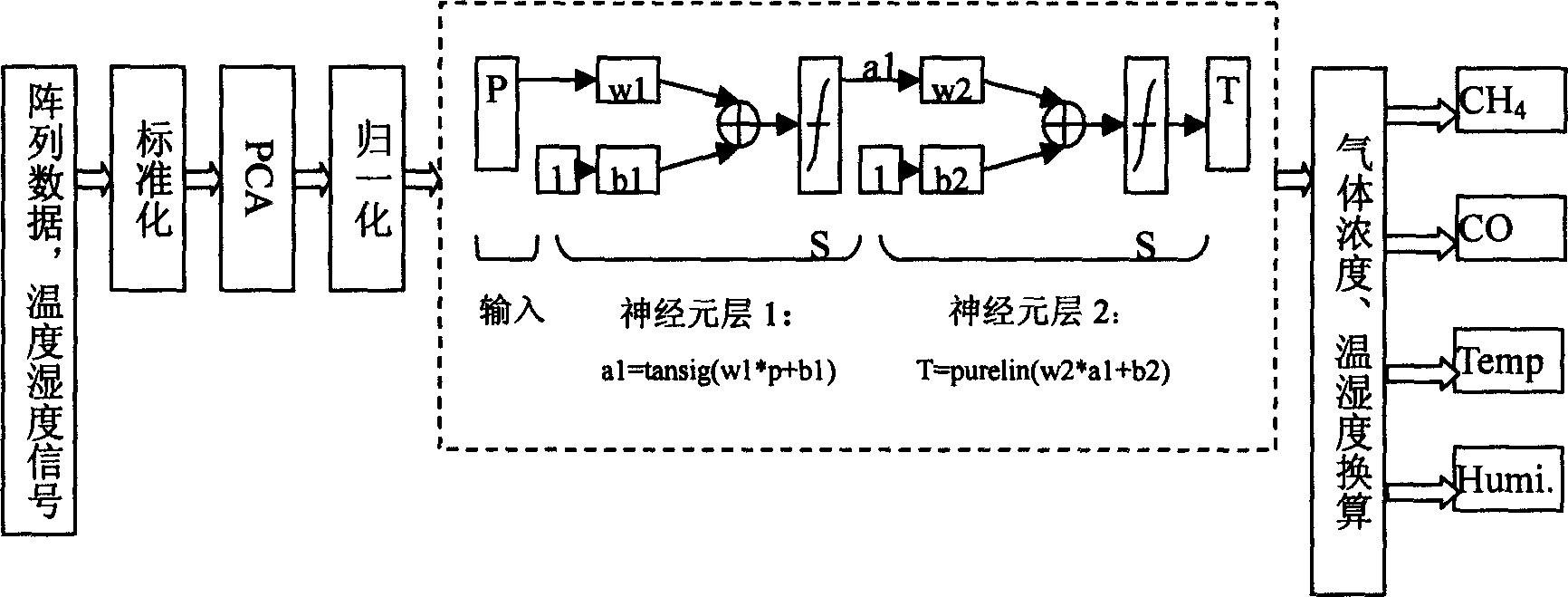

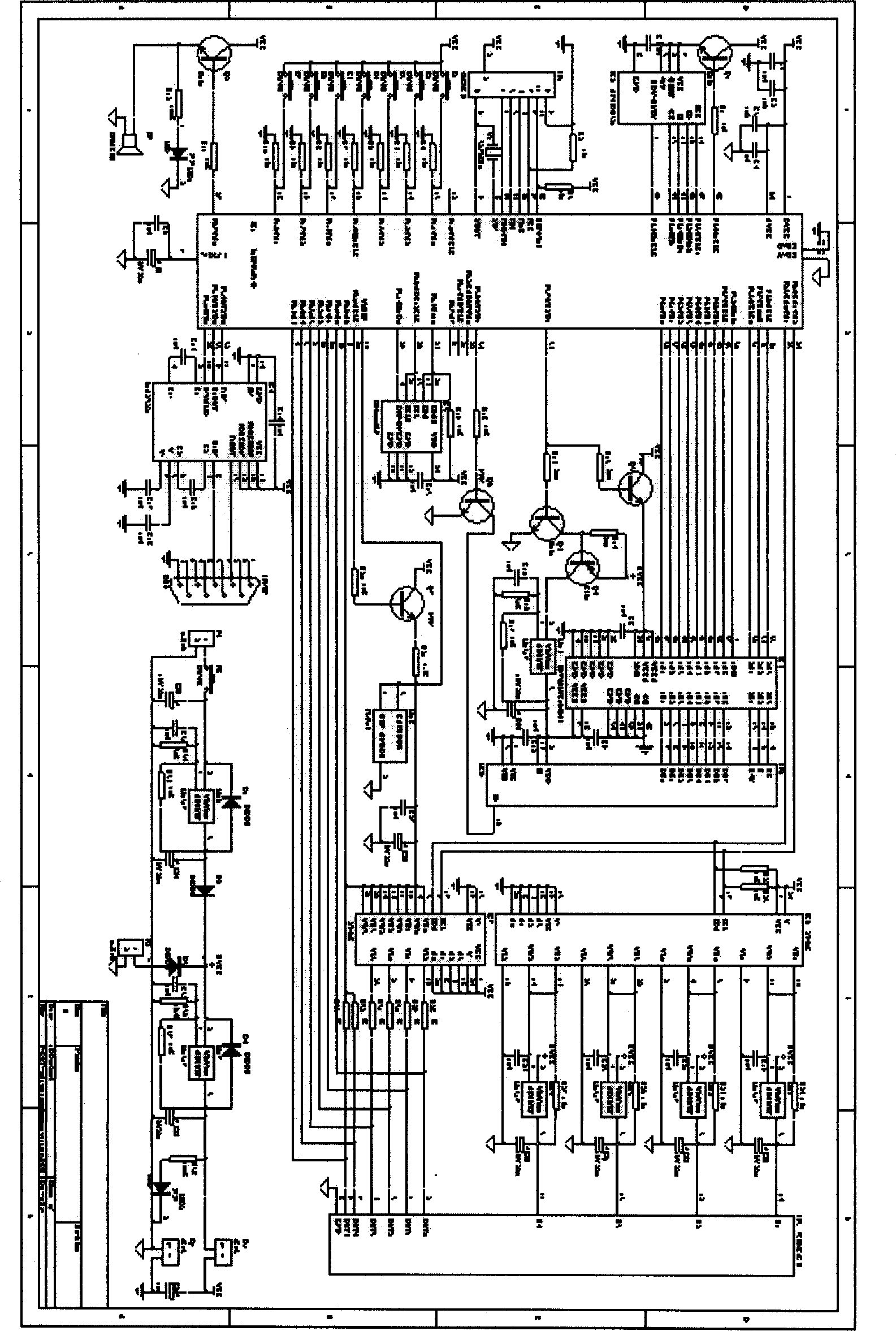

Portable gas detection analyzer with temperature and humidity compensation function

InactiveCN1588030AReal-time temperature and humidity compensationReal-time monitoring of temperature and humidity changesMaterial analysis by electric/magnetic meansInstrumental componentsEngineeringAnalytical technique

The invention provides a portable gas detecting and analysing instrument with temperature and humidity compensation function, which belongs to gas detecting and analysing field. It discloses a portable CO and CH4 gas detecting analysing instrument with a temperature and humidity compensation function. The instrument includes a control circuit and the circuits connected with it including the gas sensor detecting circuit, temperature detecting circuit, humidity detecting circuit, LCD circuit, acousto -optical alarming circuit, data storing circuit, PC communication interface circuit, timing circuit, heating control circuit and the power circuit. The gas detecting instrument in the invention can real-time detecte CO and CH4 content in the detected gas and the change of the environmental temperature and humidity and store the test data, time and environmental information into the memory for further analysis with computer and make the temperature and humidity compensation, collect, manage and keep the test information for retrieving. The instrument can be applied to detection of environment and gas content in mine and regions abundant of fuel gas such as CO and CH4, etc.

Owner:DALIAN UNIV OF TECH +1

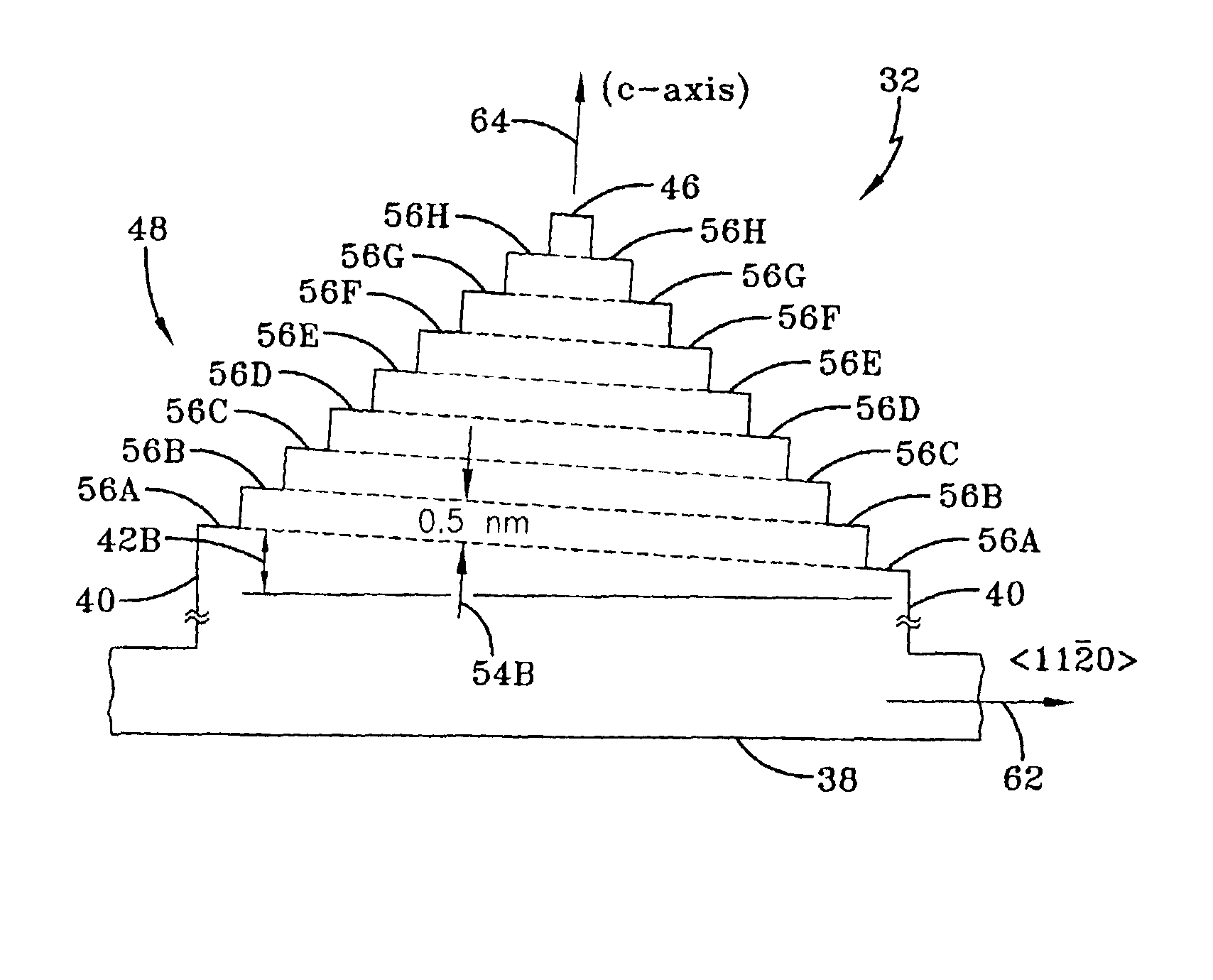

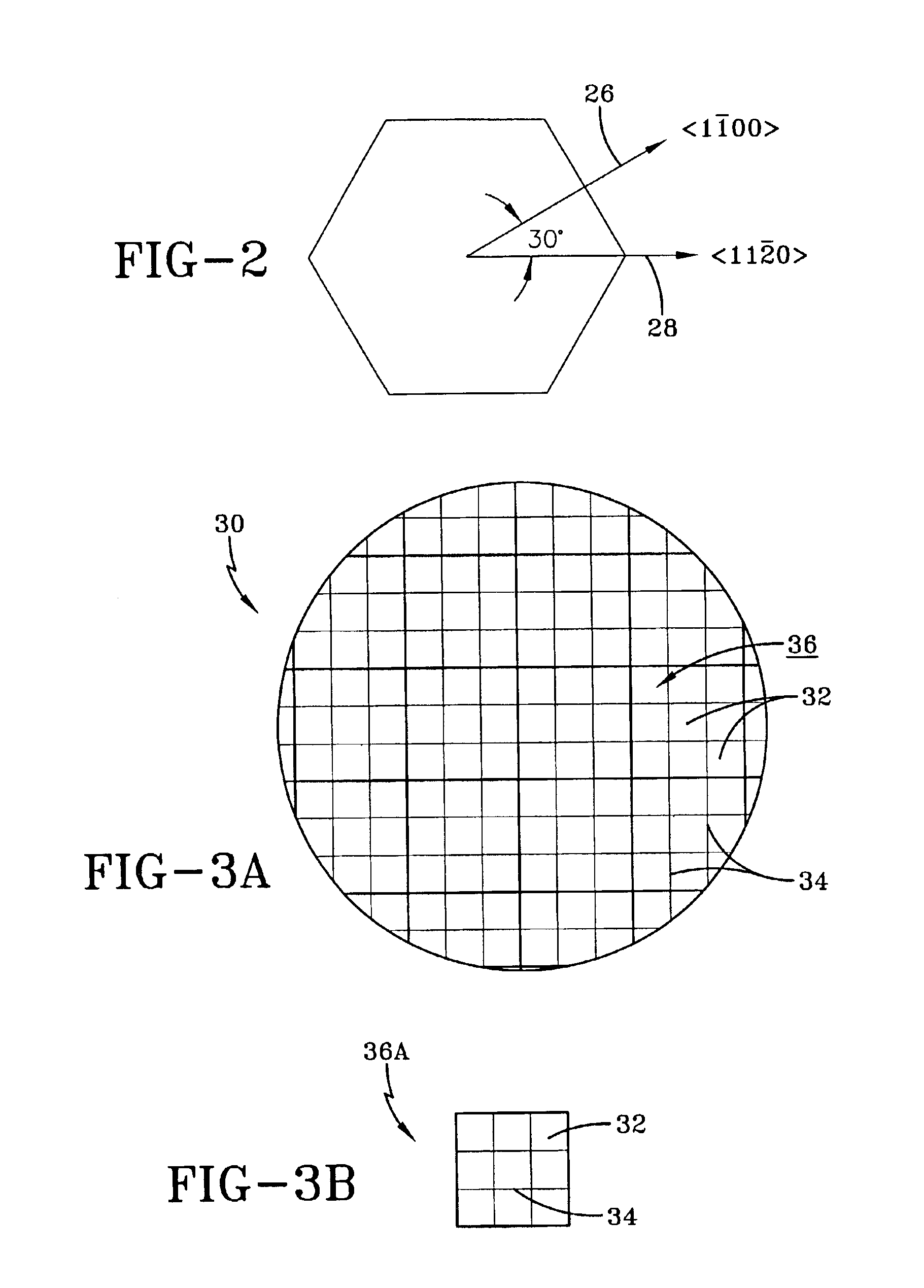

Method for the production of nanometer scale step height reference specimens

InactiveUS6869480B1Good precisionEliminate needPolycrystalline material growthAfter-treatment detailsReference sampleSingle crystal substrate

Methods are disclosed that provide for structures and techniques for the fabrication of ordered arrangements of crystallographically determined nanometer scale steps on single crystal substrates, particularly SiC. The ordered nanometer scale step structures are produced on the top surfaces of mesas by a combination of growth and etching processes. These structures, sometimes referred to herein as artifacts, are to enable step-height calibration, particularly suitable for scanning probe microscopes and profilometers, from less than one nanometer (nm) to greater than 10 nm, with substantially no atomic scale roughness of the plateaus on either side of each step.

Owner:NASA

Method and apparatus for force control of a scanning probe

A method for controlling a force acting on a scanning probe of a cantilever by setting bandwidth of a feedback loop constituted by detecting minute displacement of the cantilever and controlling a force of the scanning probe to be greater than a primary resonant frequency of the cantilever.

Owner:IBM CORP +1

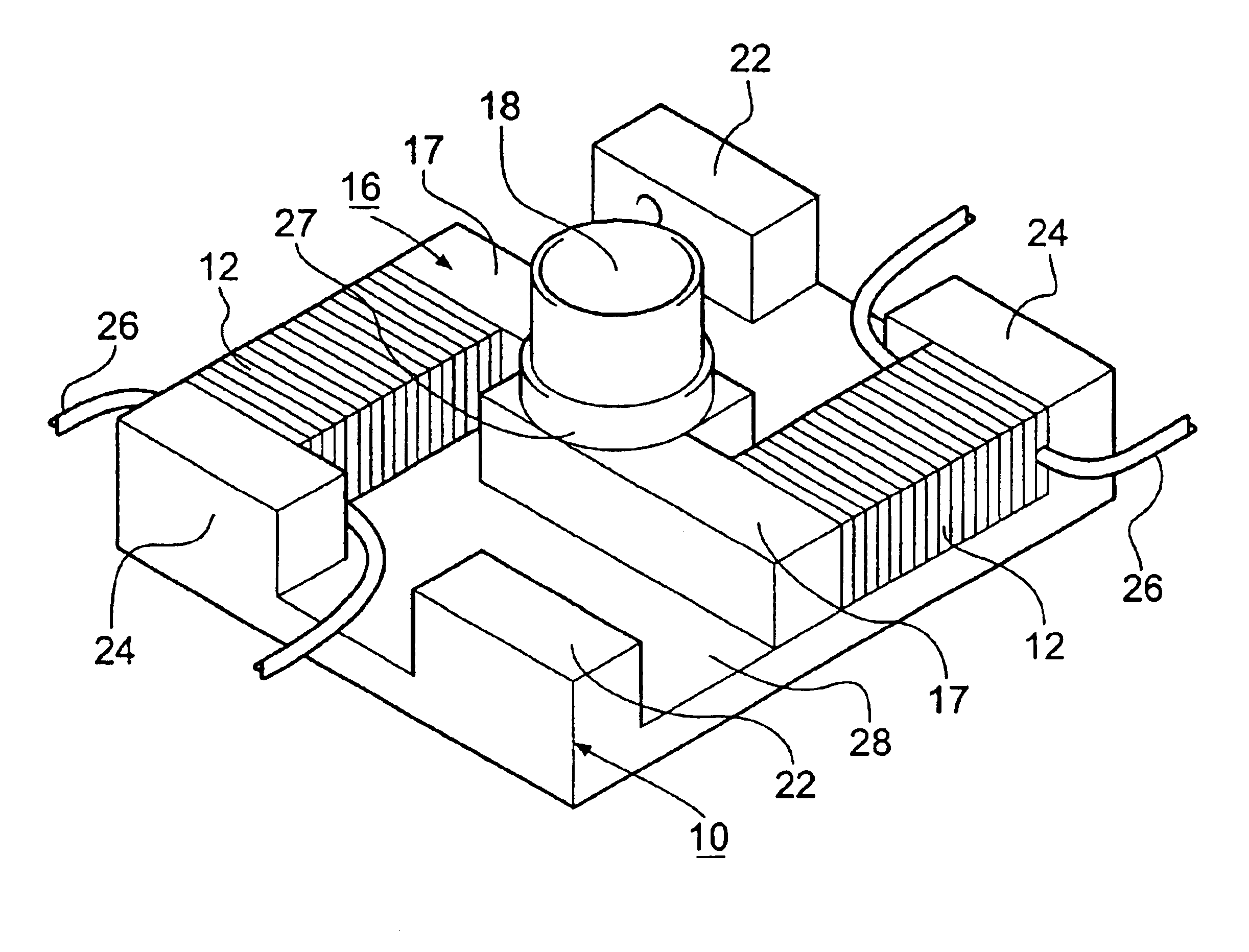

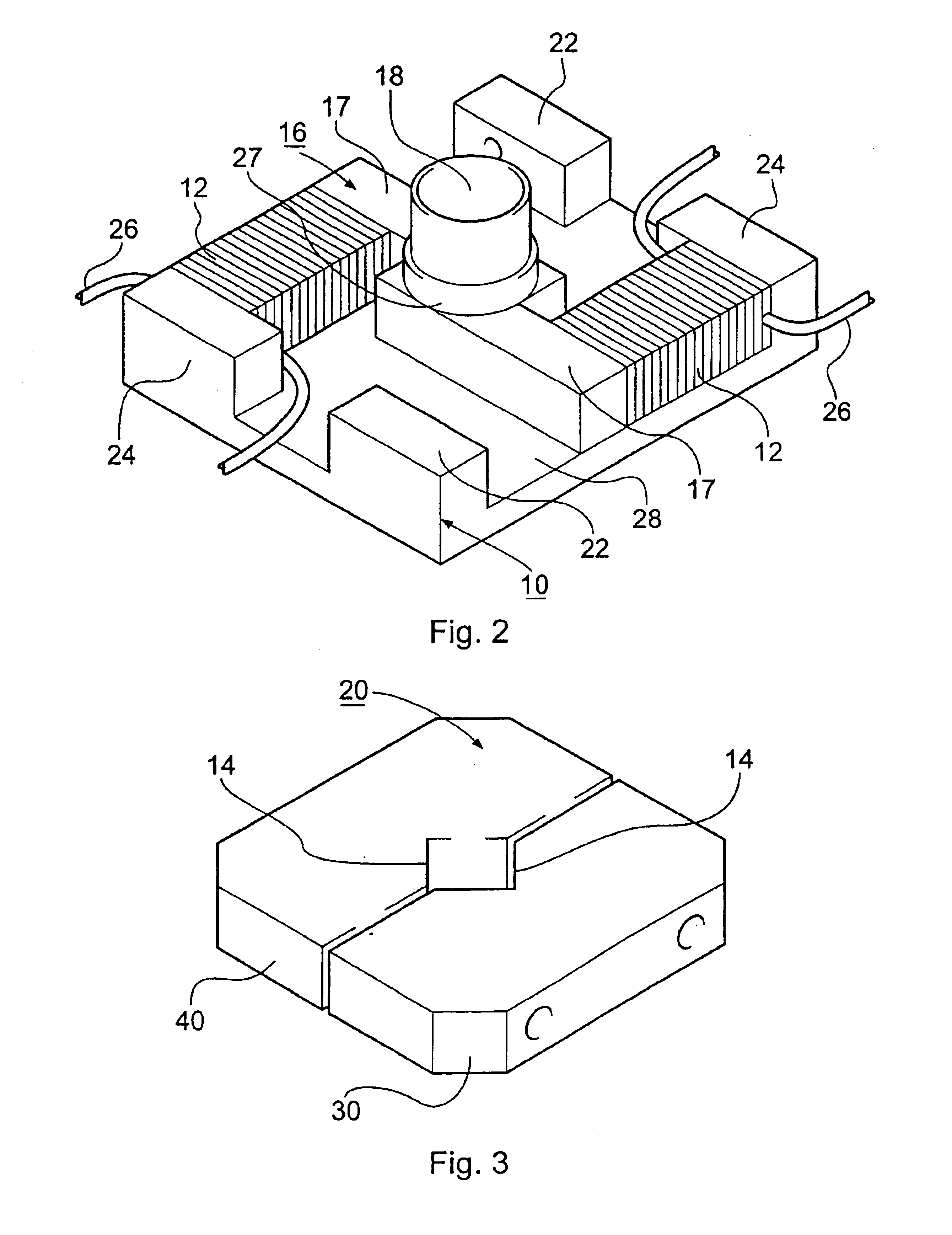

Inertial rotation device

InactiveUS6940210B2Reduce clamping forceEasy to operatePiezoelectric/electrostriction/magnetostriction machinesNanotechnologyElectricityPiezoelectric actuators

An inertial positioning device comprising: a base plate (10); a top plate (20) for mounting an element to be rotated; a rotation member (16) having a column (18) on which the top plate is mounted in frictional engagement for slip-stick rotational motion; and a pair of piezoelectric actuators (12) each secured to the base plate at one end and to lateral extensions (17) of the rotation member at their other ends. Simultaneous actuation of the piezoelectric actuators rotates the column of the rotation member about its axis. When a suitable asymmetric drive signal is supplied to the piezoelectric actuators, the top plate is rotated by slip-stick motion. The device is compact, has a good load capacity for an inertial motor and is operable in extreme environments such as liquid helium temperatures, high vacuum and high magnetic fields.

Owner:ATTOCUBE SYST AG

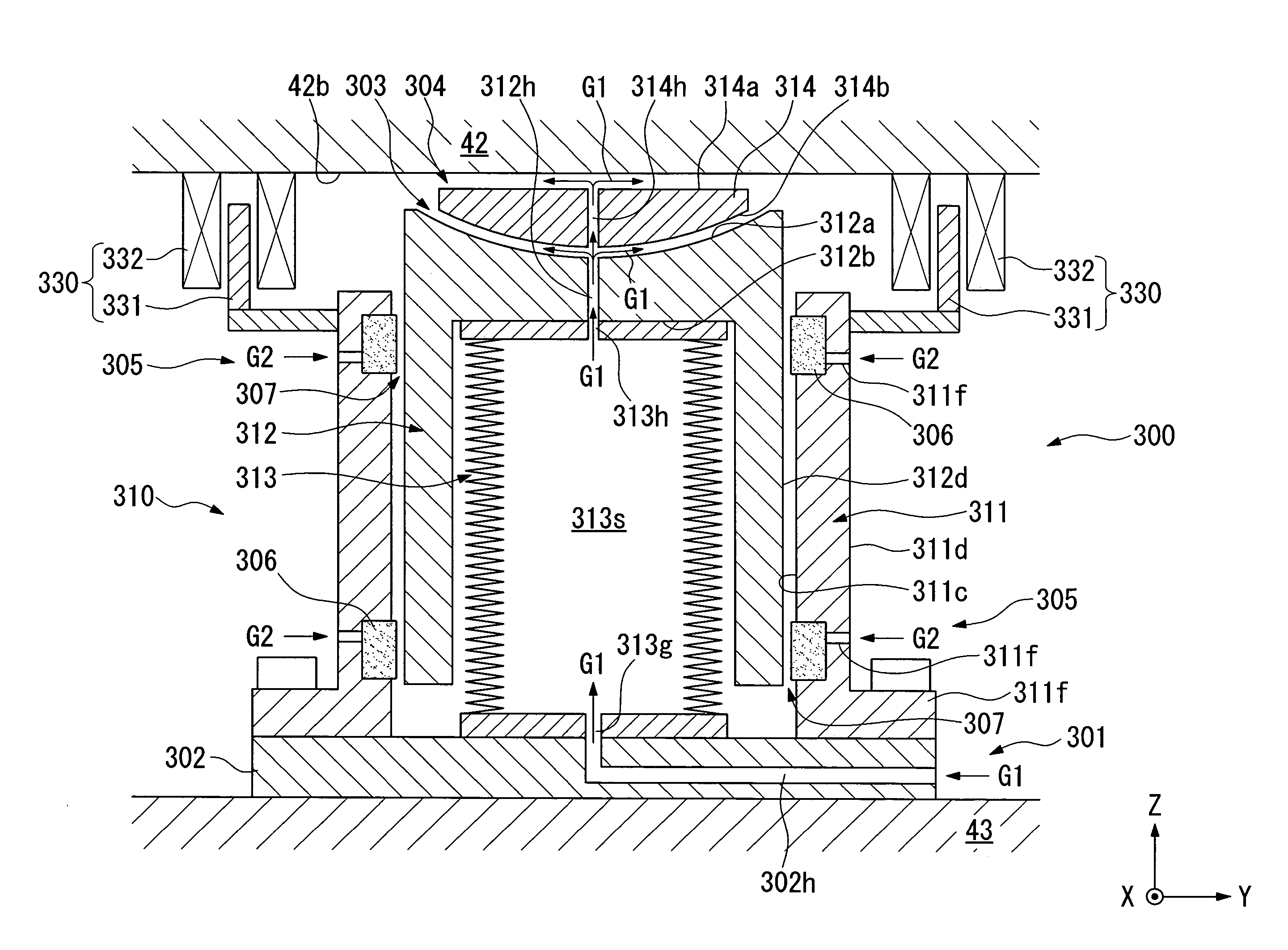

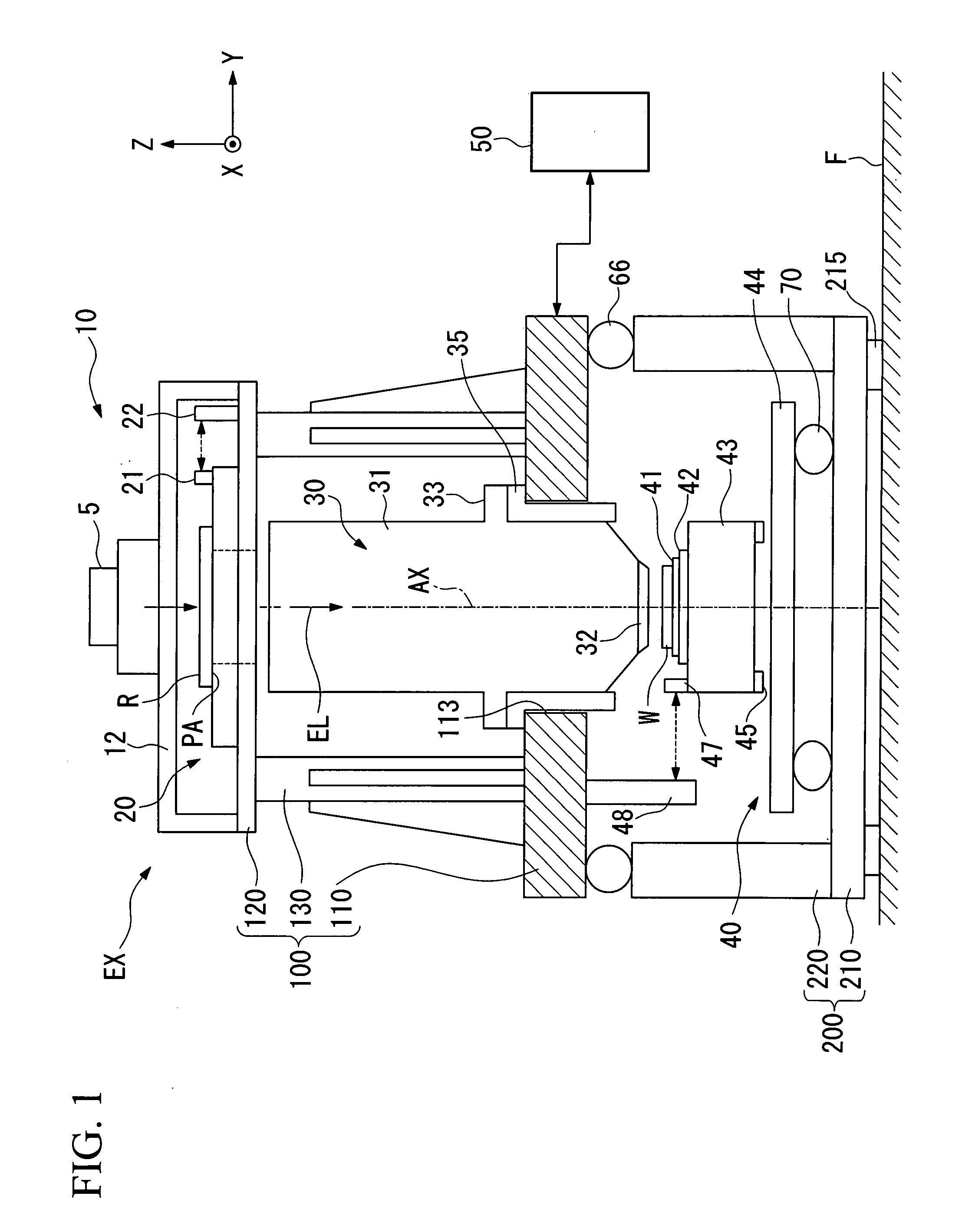

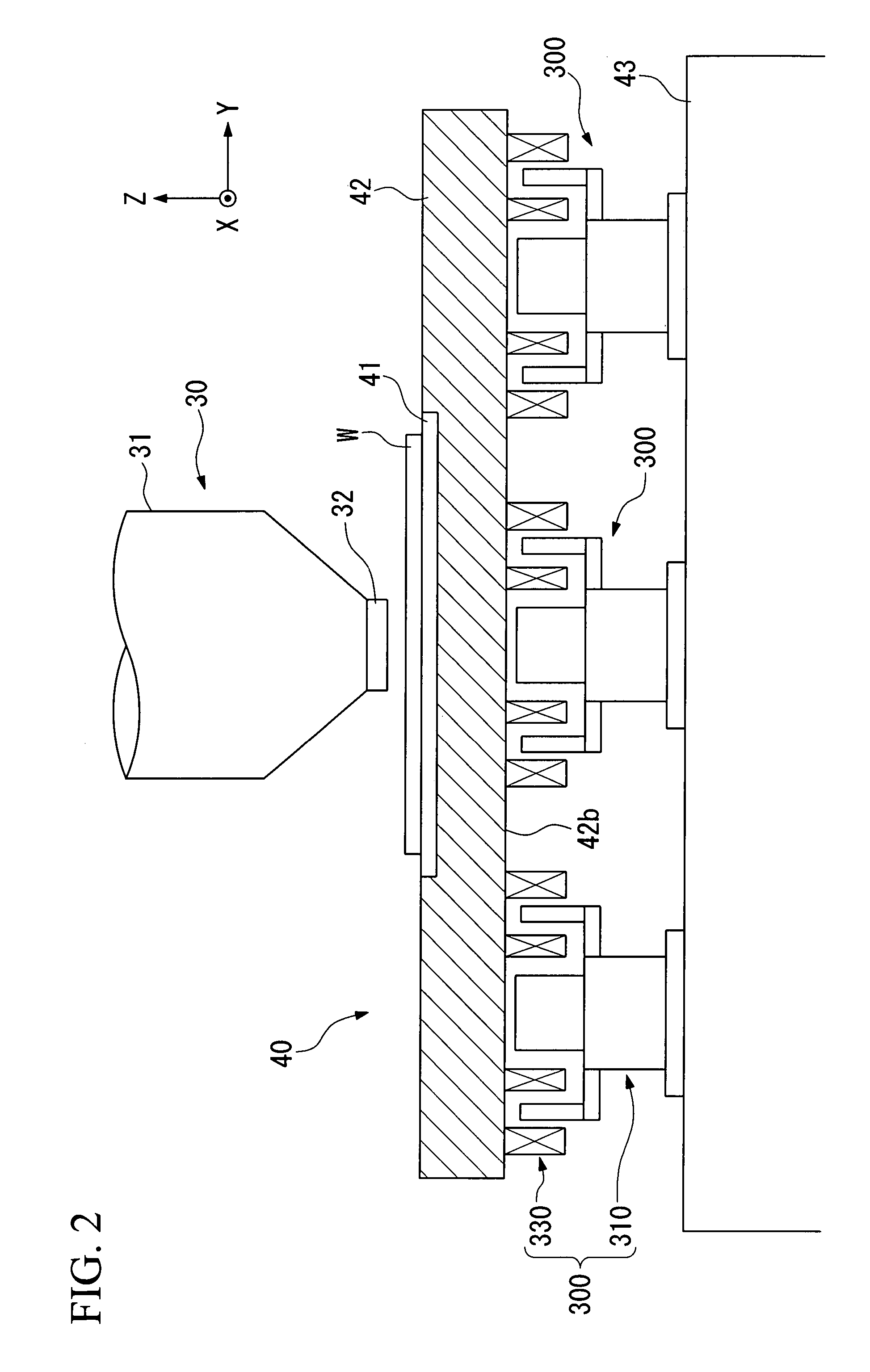

Support Apparatus, Stage Apparatus, Exposure Apparatus, And Device Manufacturing Method

InactiveUS20080013060A1Supported can be changedImprove responseLinear bearingsGas cushion bearingsEngineeringCylinder block

A support apparatus, a stage apparatus, an exposure apparatus, etc. are proposed that can increase response of a relative movement between a piston and a cylinder, etc. are proposed. There is provided a support apparatus including: a cylinder portion; a piston portion that is provided inside the cylinder portion and is movable in a Z direction; a fluid bearing formed in at least a portion between an inner wall of the cylinder portion and an outer wall of the piston portion, the support apparatus supporting a supported member in the Z direction with respect to a support member by means of a biasing force generated by the cylinder portion and the piston portion, in which fluids are supplied independently inside the fluid bearing and the cylinder.

Owner:NIKON CORP

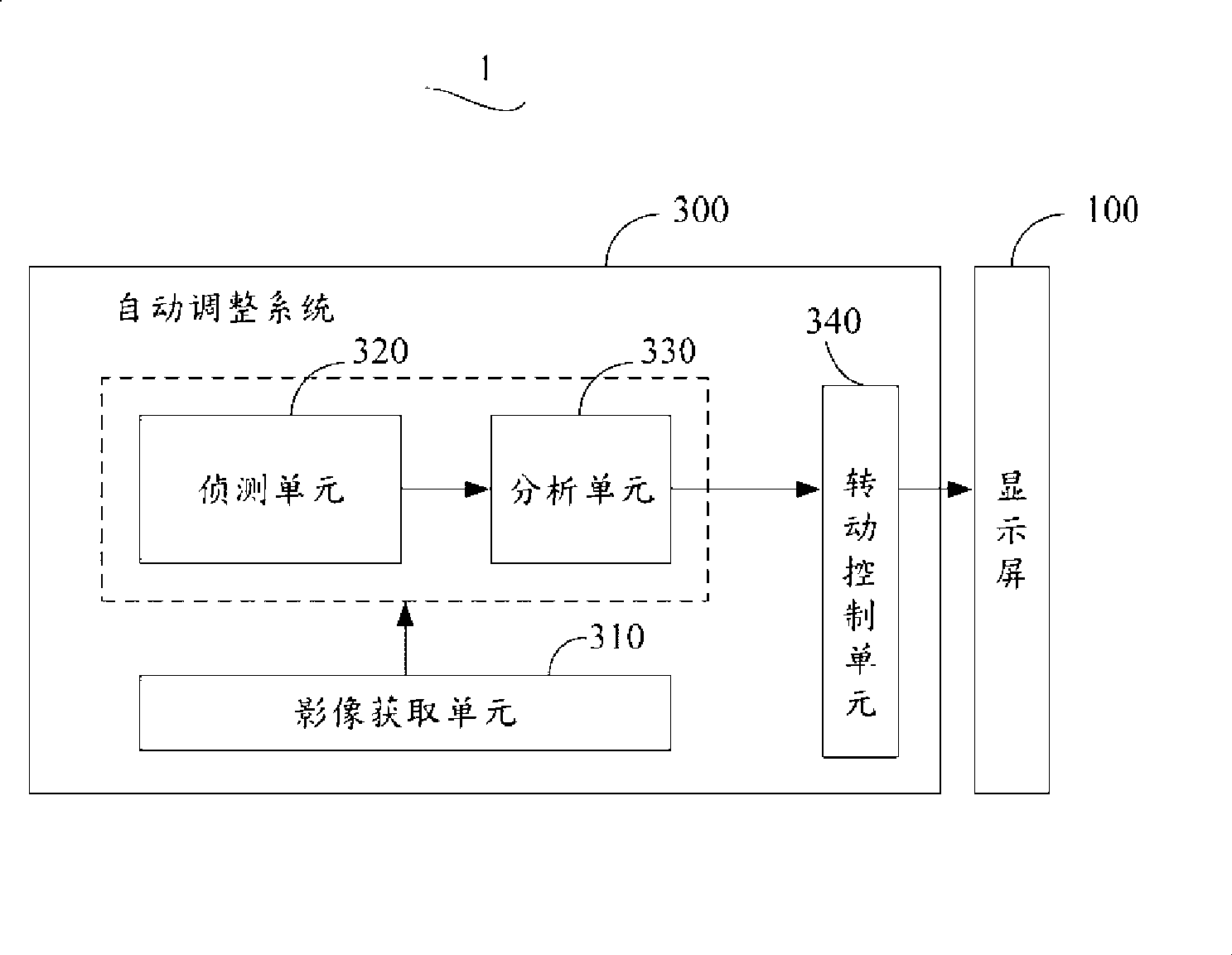

Display equipment and method for automatically regulating display direction

InactiveCN101470446AEasy to useTo achieve the effect of automatic adjustmentCharacter and pattern recognitionInstrumental componentsMedicineComputer graphics (images)

Owner:FOSHAN PREMIER SCI & TECH CO LTD +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com