Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1232 results about "Human-body model" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

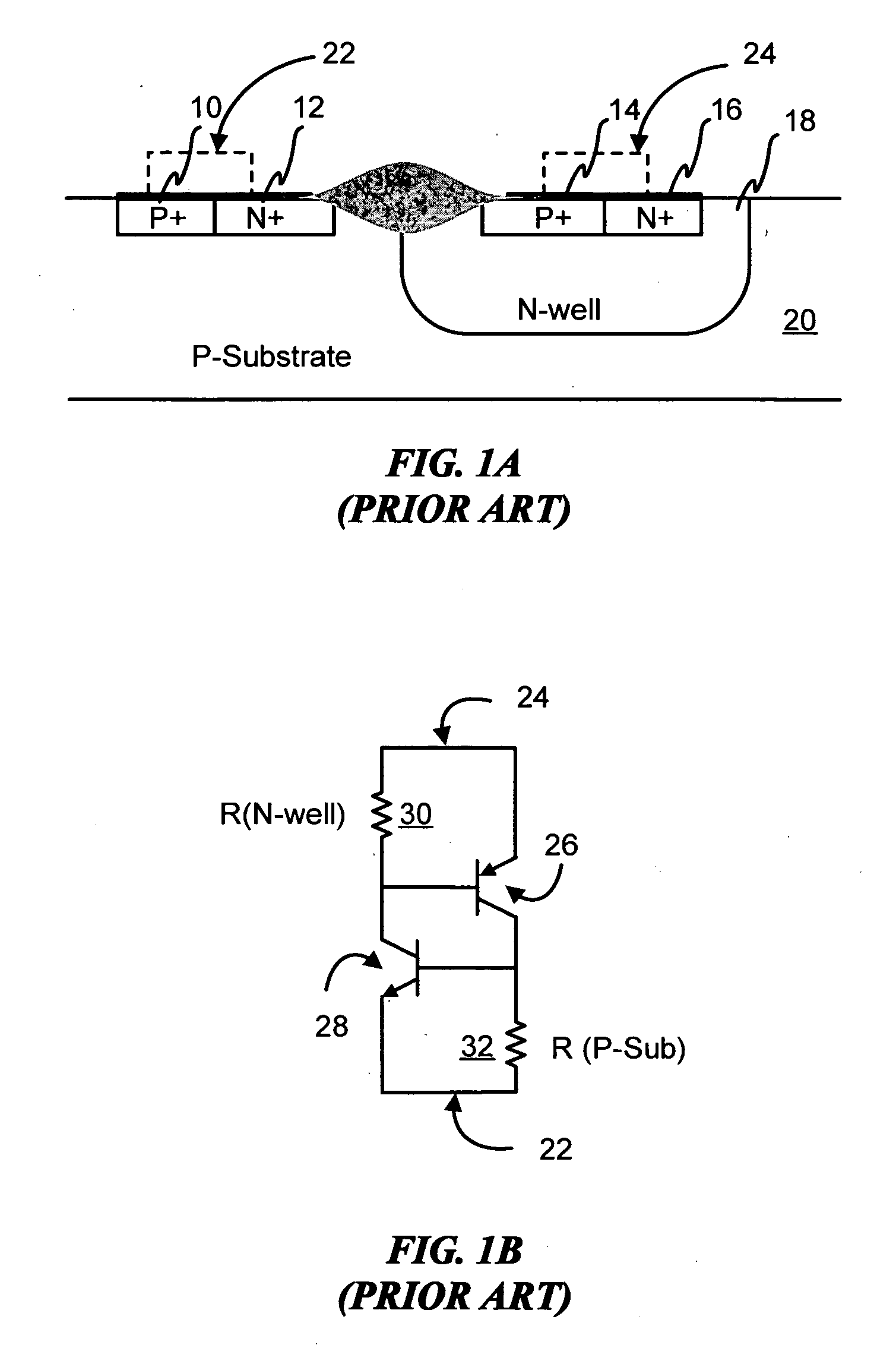

The human-body model (HBM) is the most commonly used model for characterizing the susceptibility of an electronic device to damage from electrostatic discharge (ESD). The model is a simulation of the discharge which might occur when a human touches an electronic device.

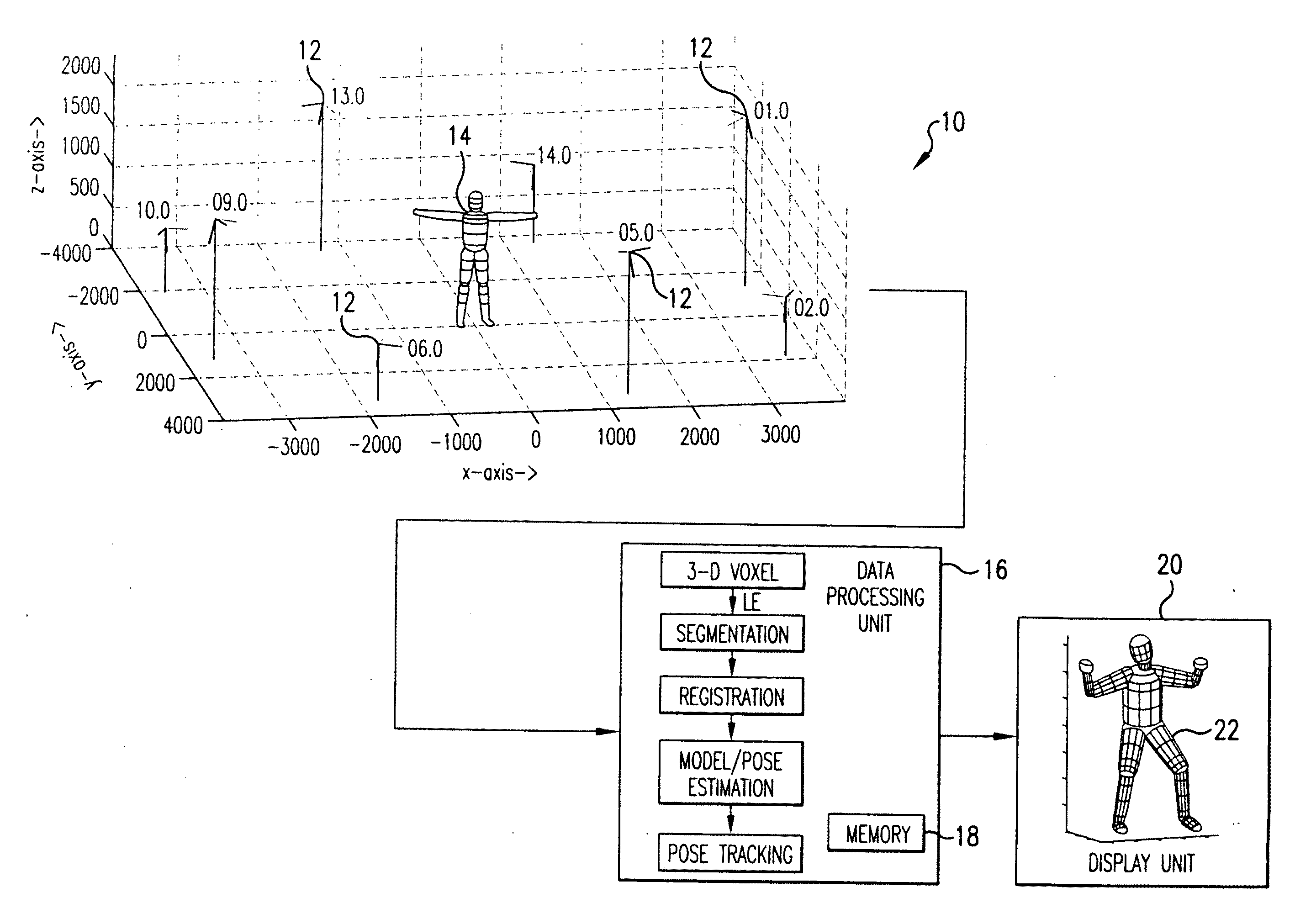

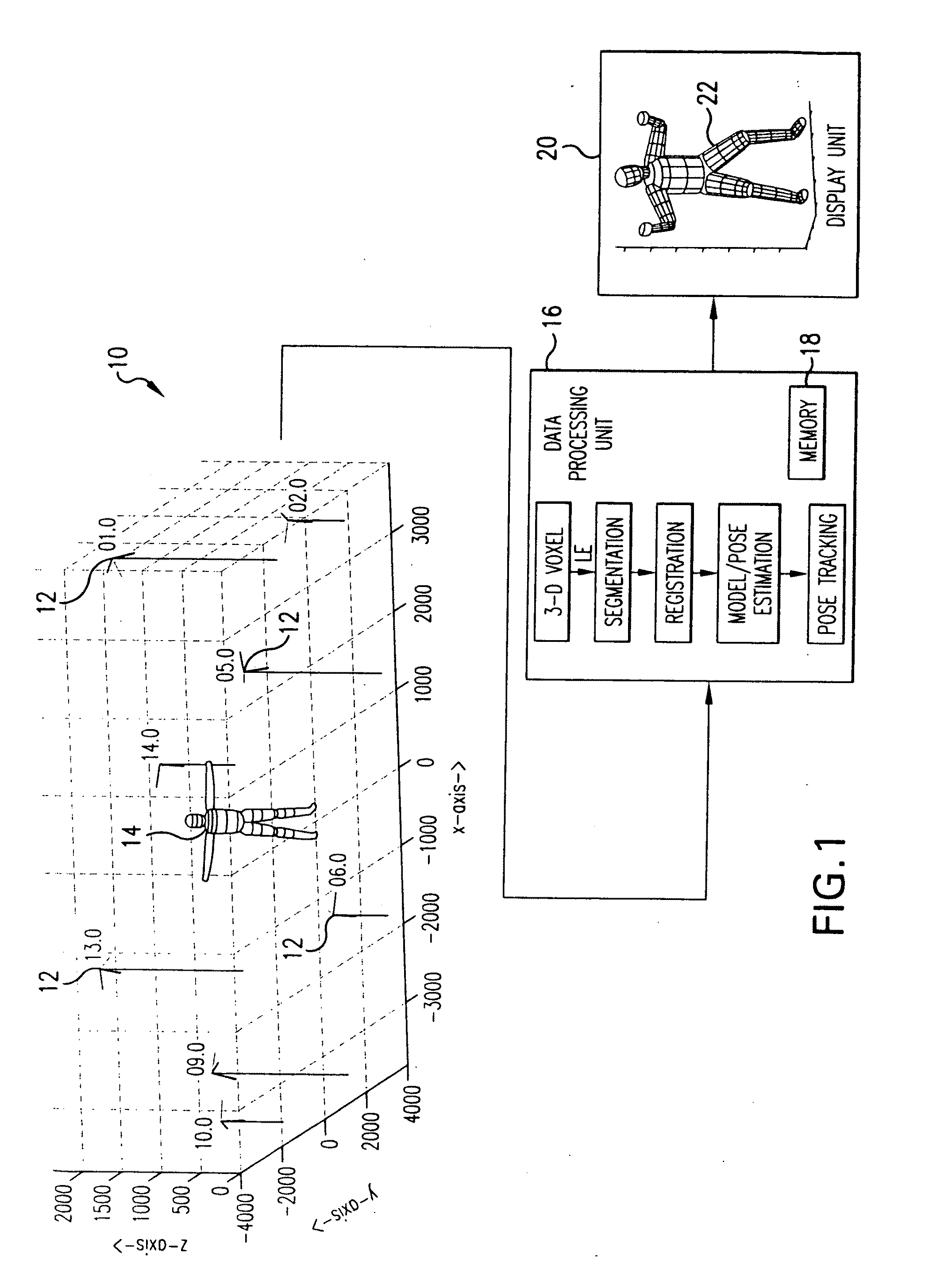

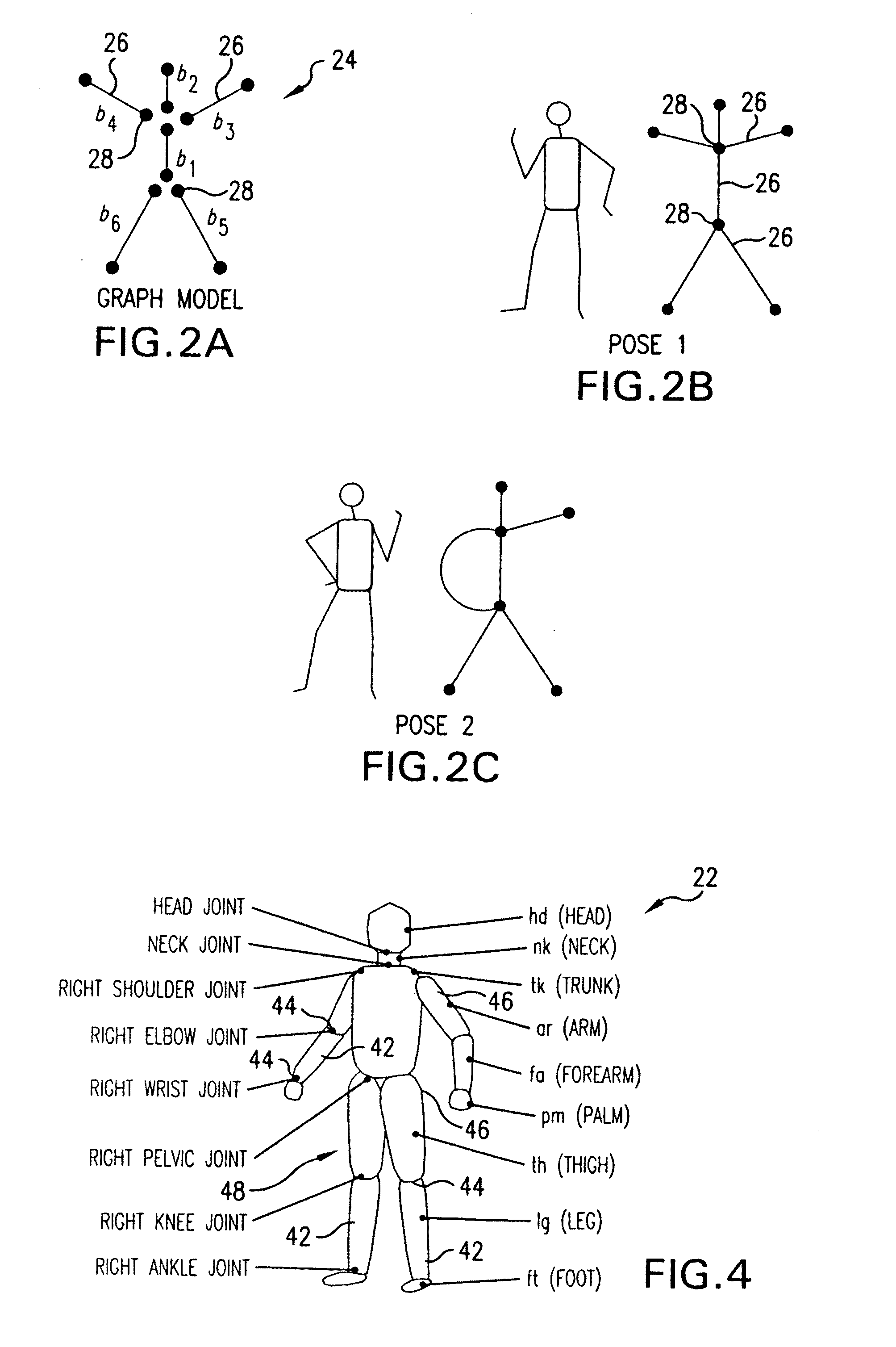

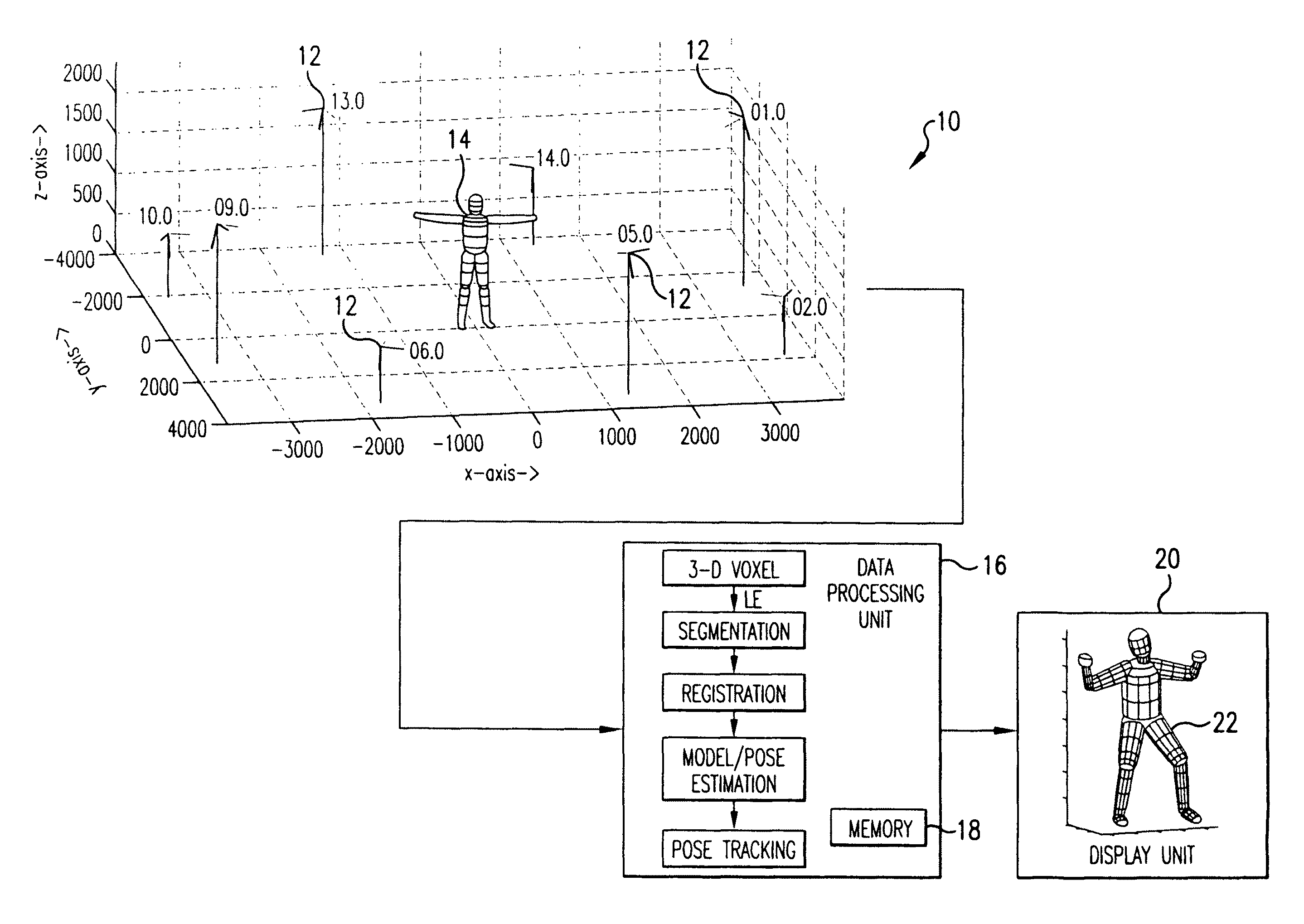

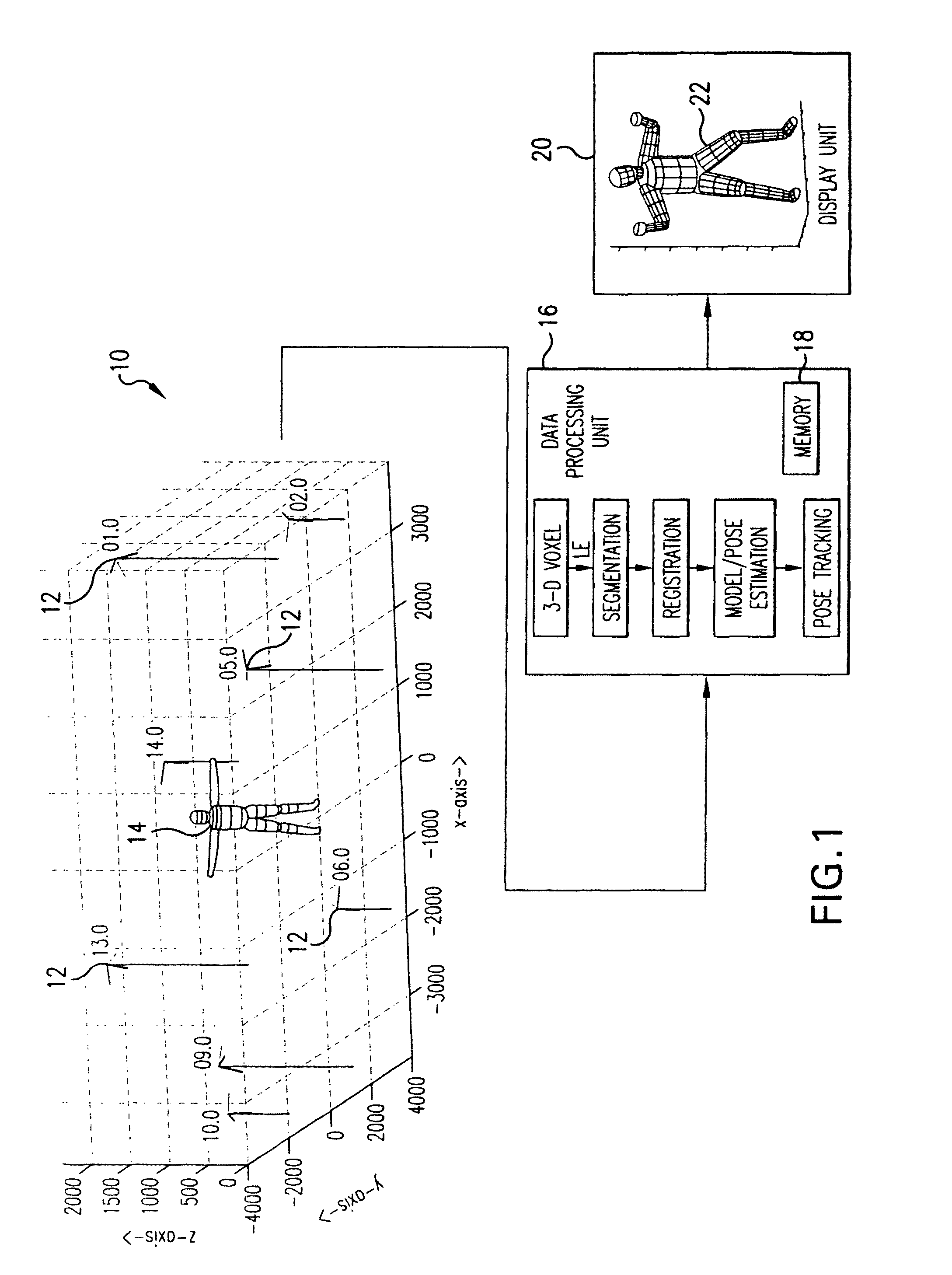

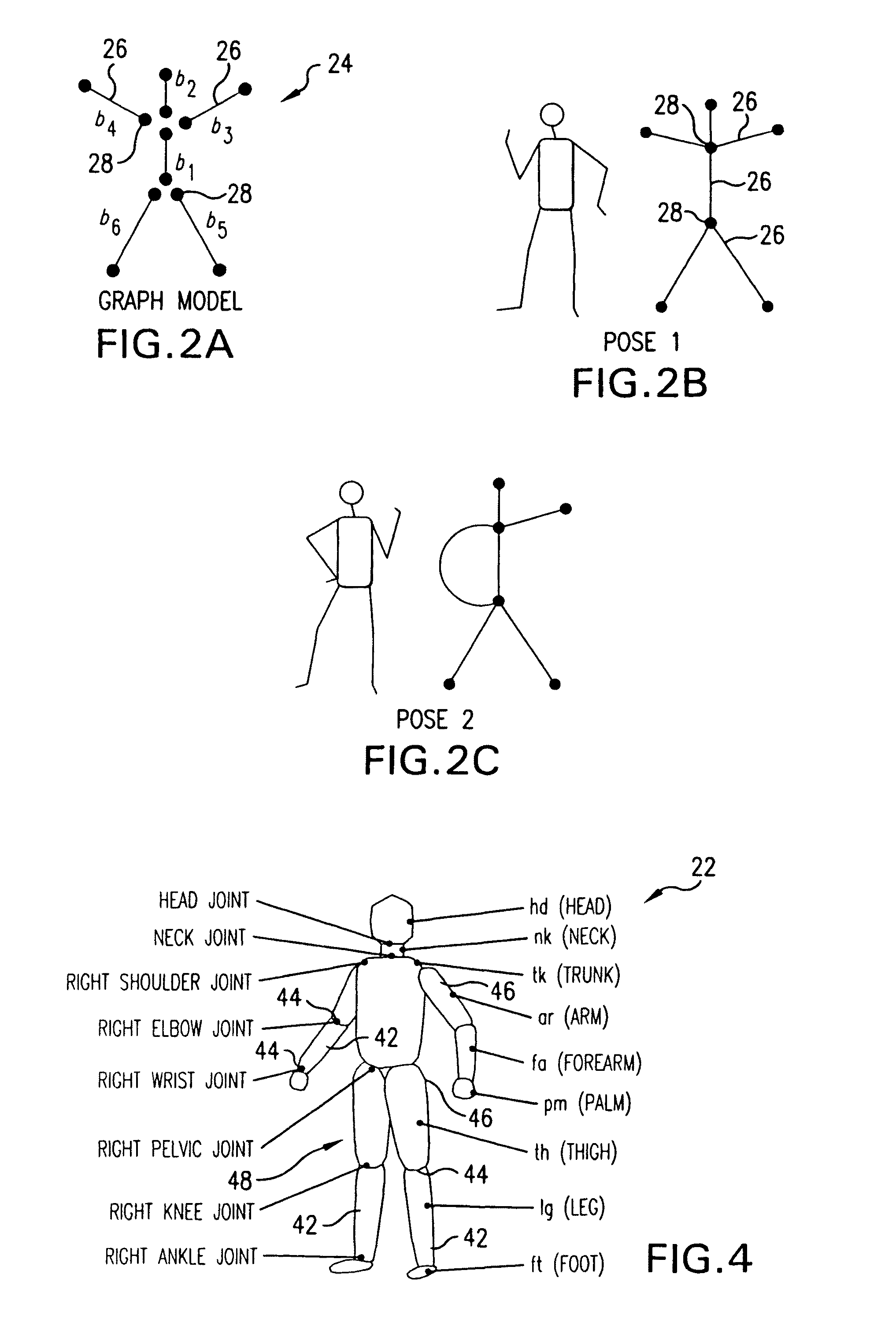

Method and system for markerless motion capture using multiple cameras

InactiveUS20090232353A1Accurate estimateAccurate presentationImage enhancementDetails involving processing stepsProbabilistic methodVoxel

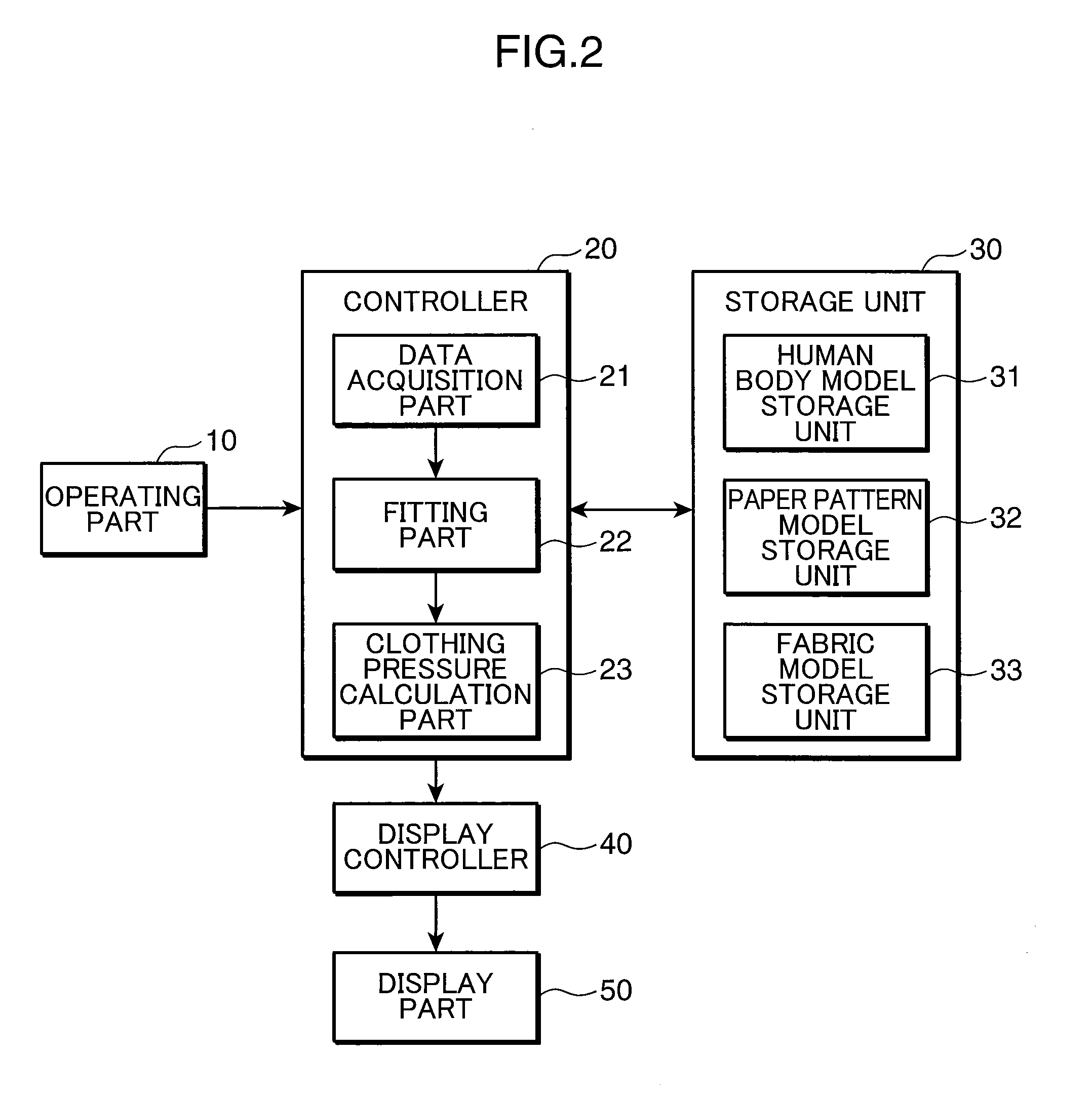

Completely automated end-to-end method and system for markerless motion capture performs segmentation of articulating objects in Laplacian Eigenspace and is applicable to handling of the poses of some complexity. 3D voxel representation of acquired images are mapped to a higher dimensional space (k), where k depends on the number of articulated chains of the subject body, so as to extract the 1-D representations of the articulating chains. A bottom-up approach is suggested in order to build a parametric (spline-based) representation of a general articulated body in the high dimensional space followed by a top-down probabilistic approach that registers the segments to an average human body model. The parameters of the model are further optimized using the segmented and registered voxels.

Owner:UNIV OF MARYLAND

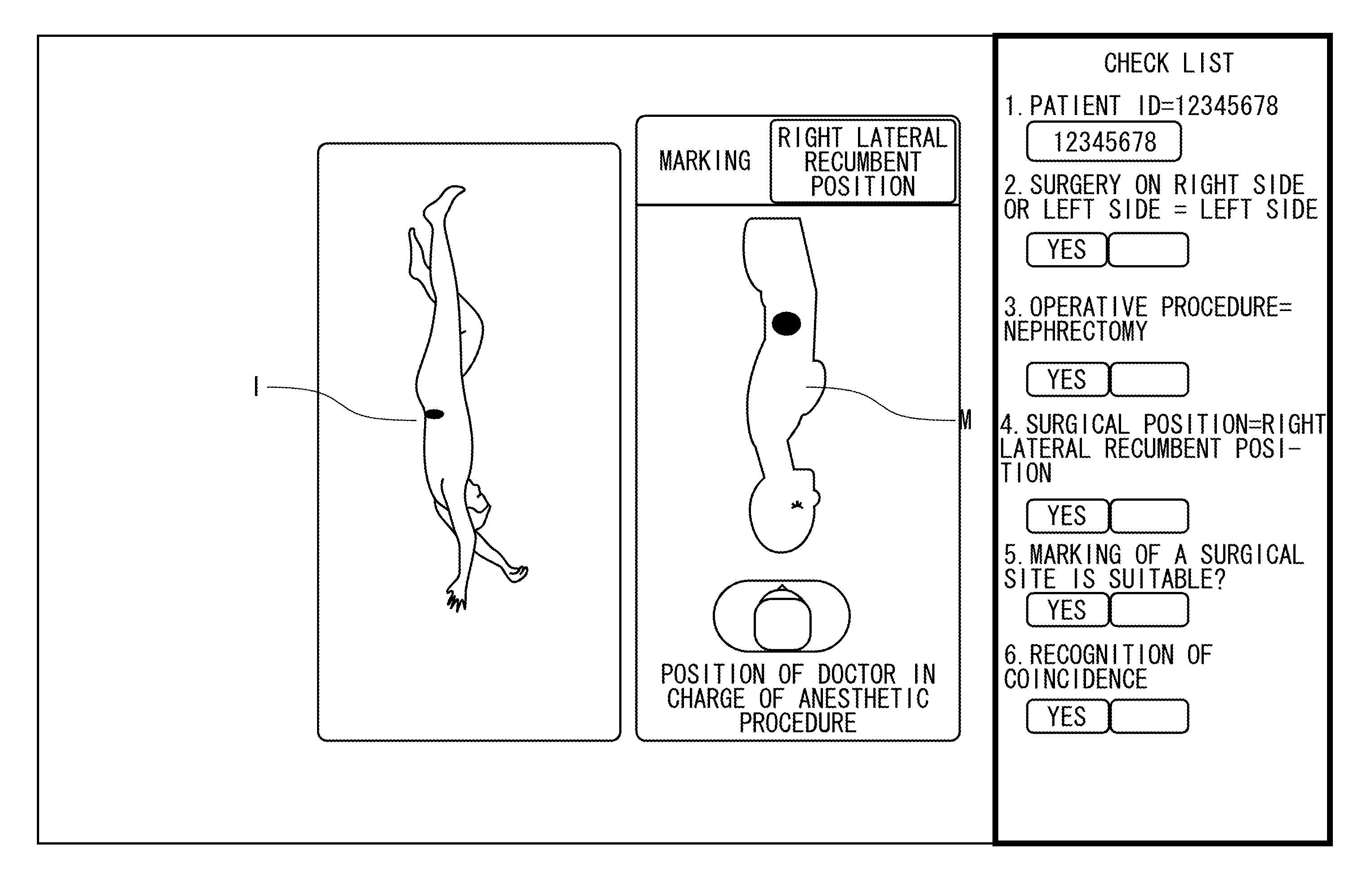

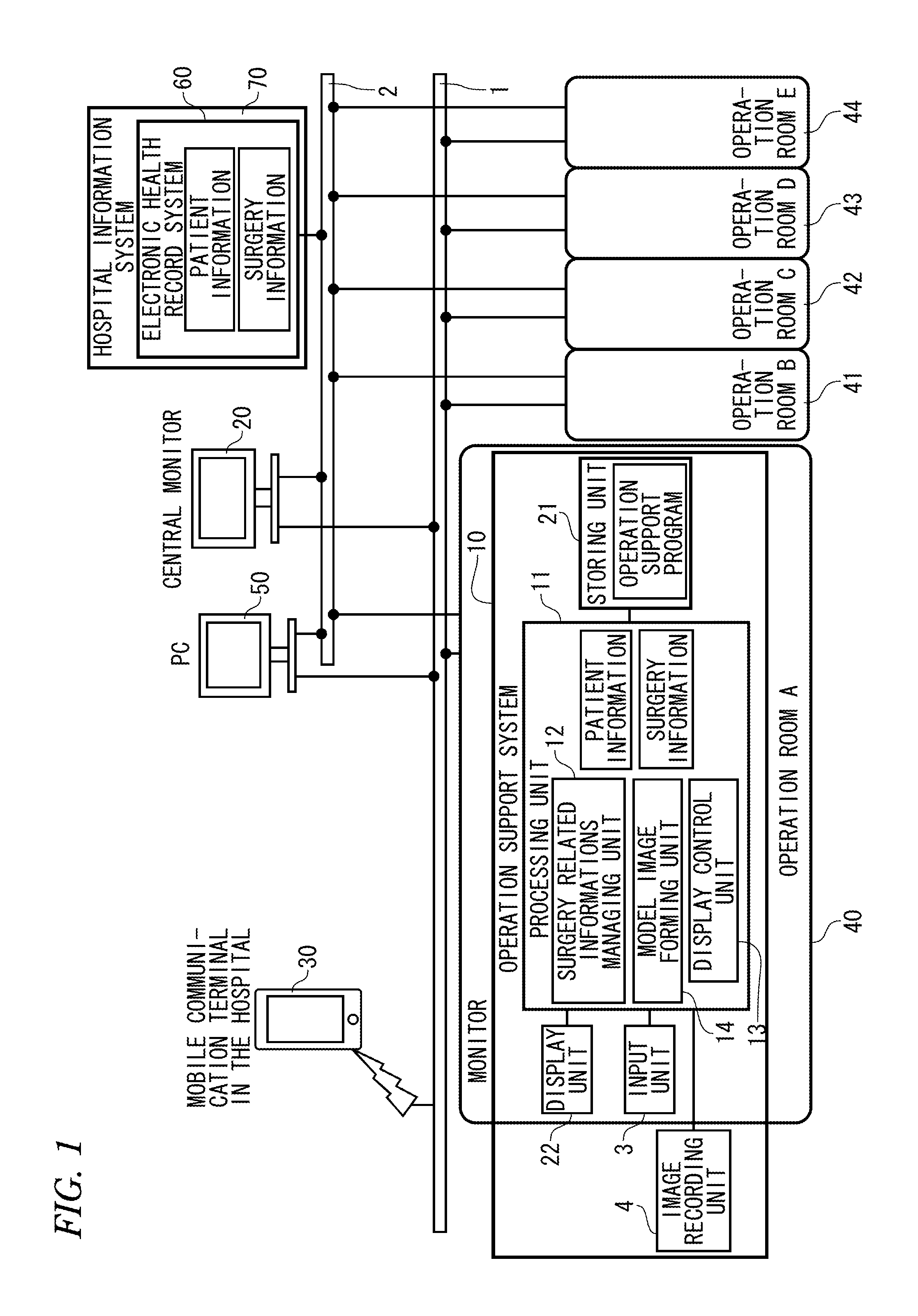

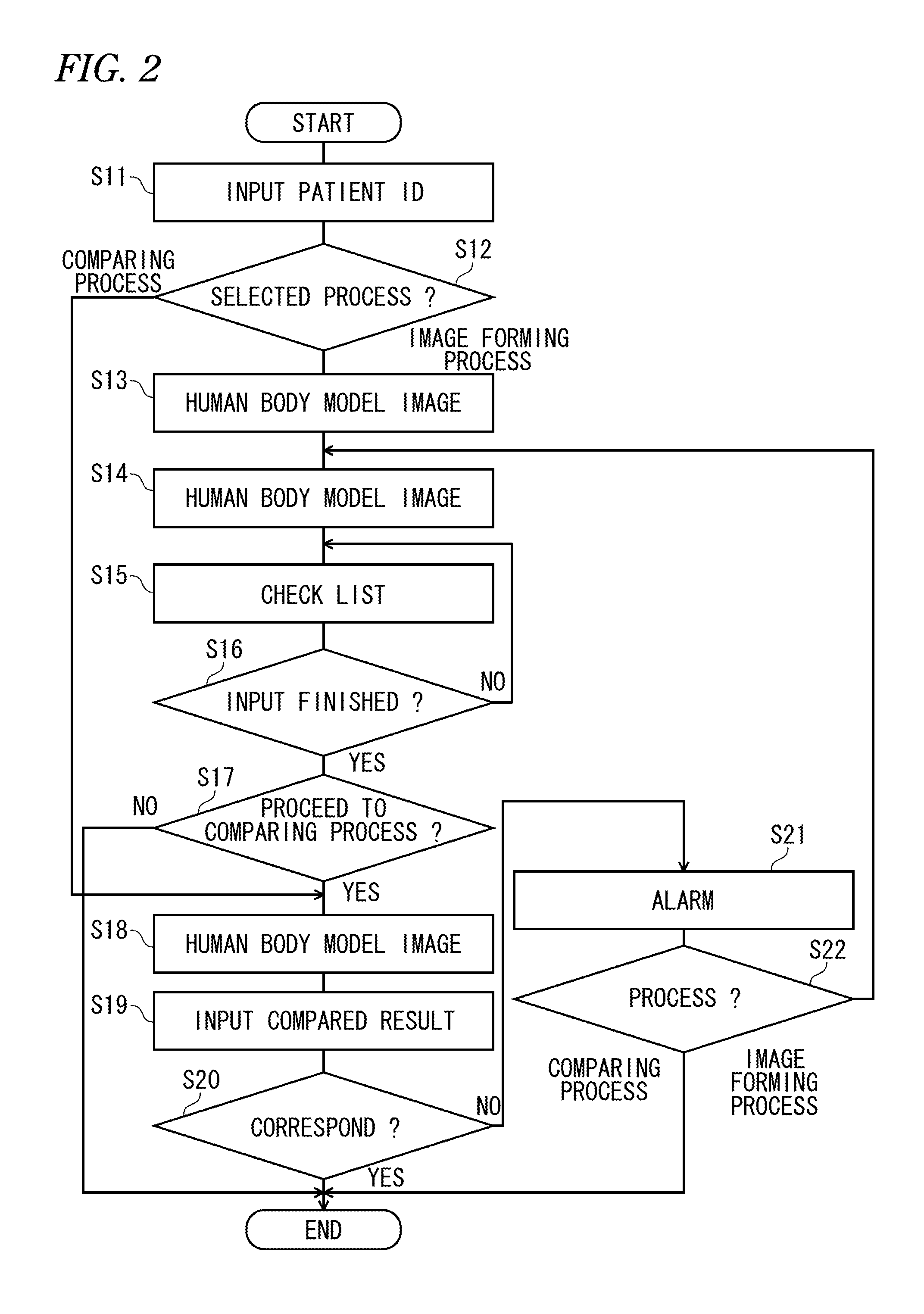

Operation support system

InactiveUS20140092089A1Reduce medical errorsReduce errorsMedical simulationMechanical/radiation/invasive therapiesSurgical siteSurgical positions

To reduce medical mistakes, for instance, a surgical site is mistaken for another part. An operation support system includes a model image forming unit which applies a mark to a surgery site of a corresponding surgical position in accordance with inputted surgery information including an operative procedure, a surgery on right side or left side and the surgical position to form a human body model image and a display control unit which displays the human body model image formed by the model image forming unit on a display unit.

Owner:NIHON KOHDEN CORP

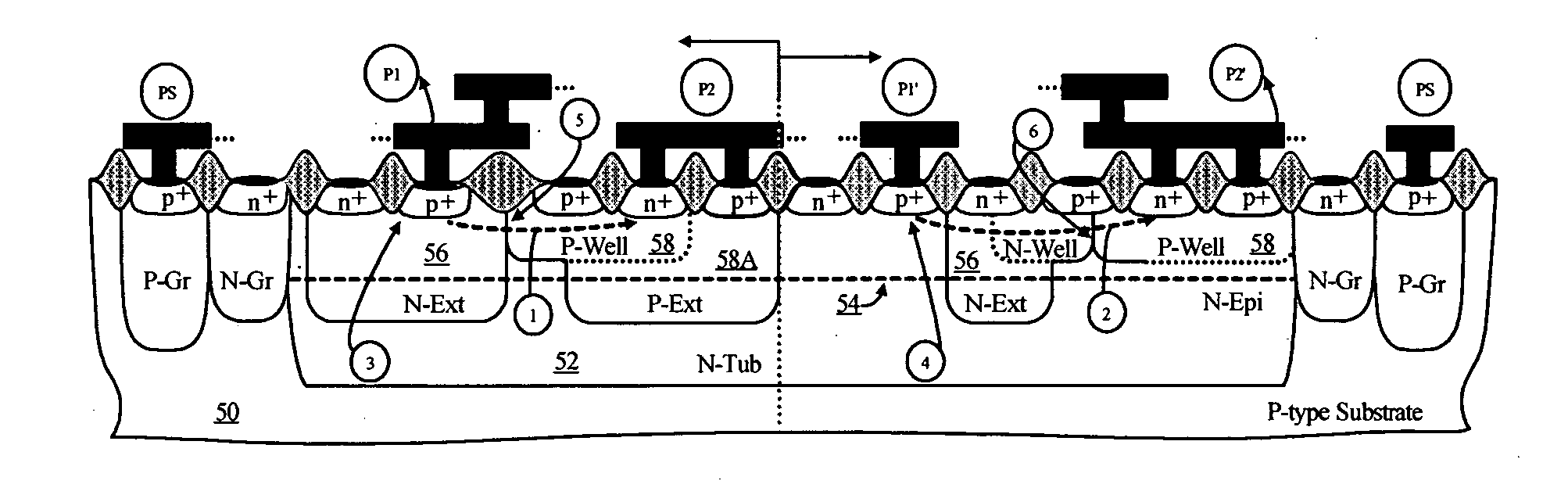

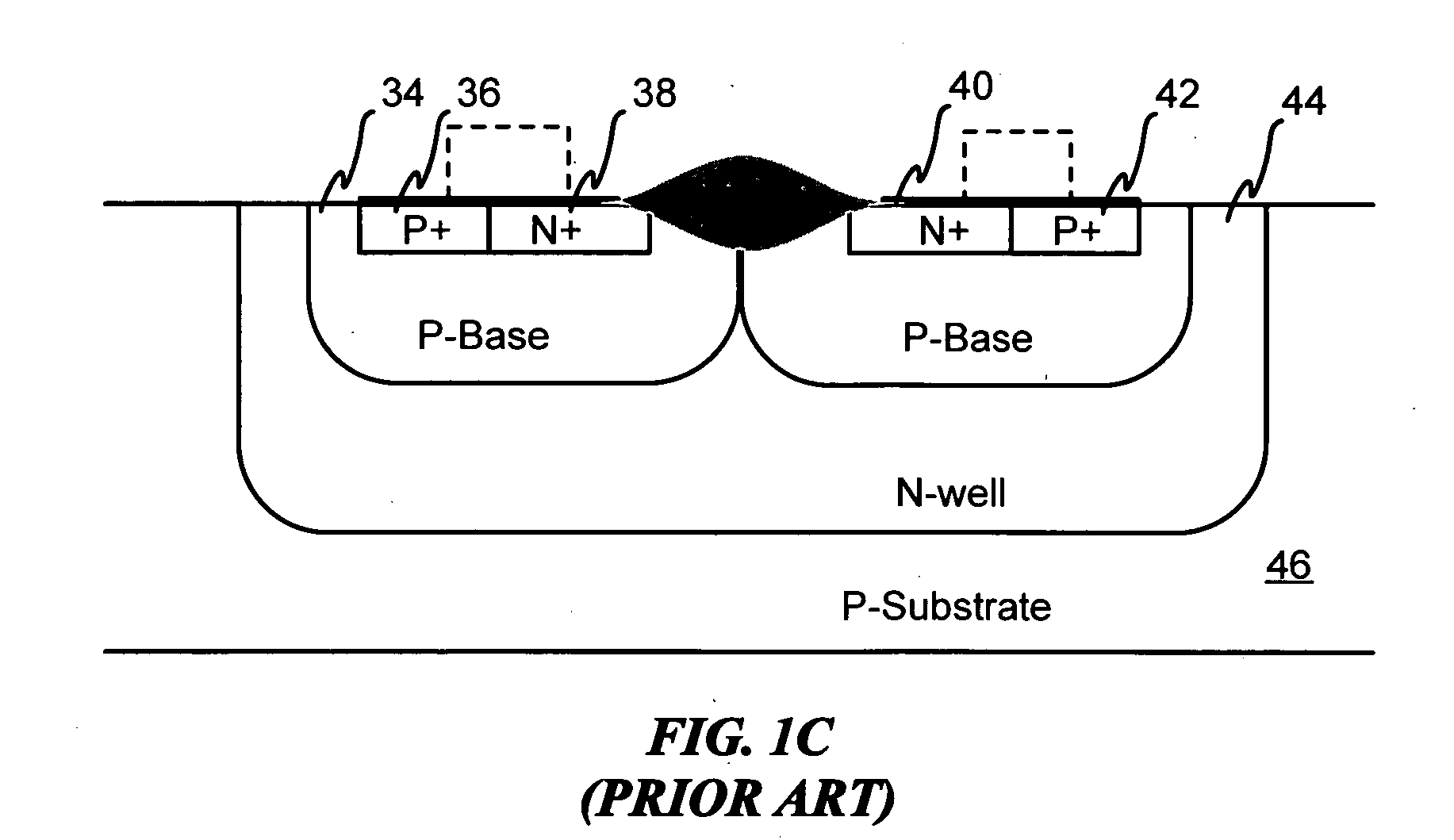

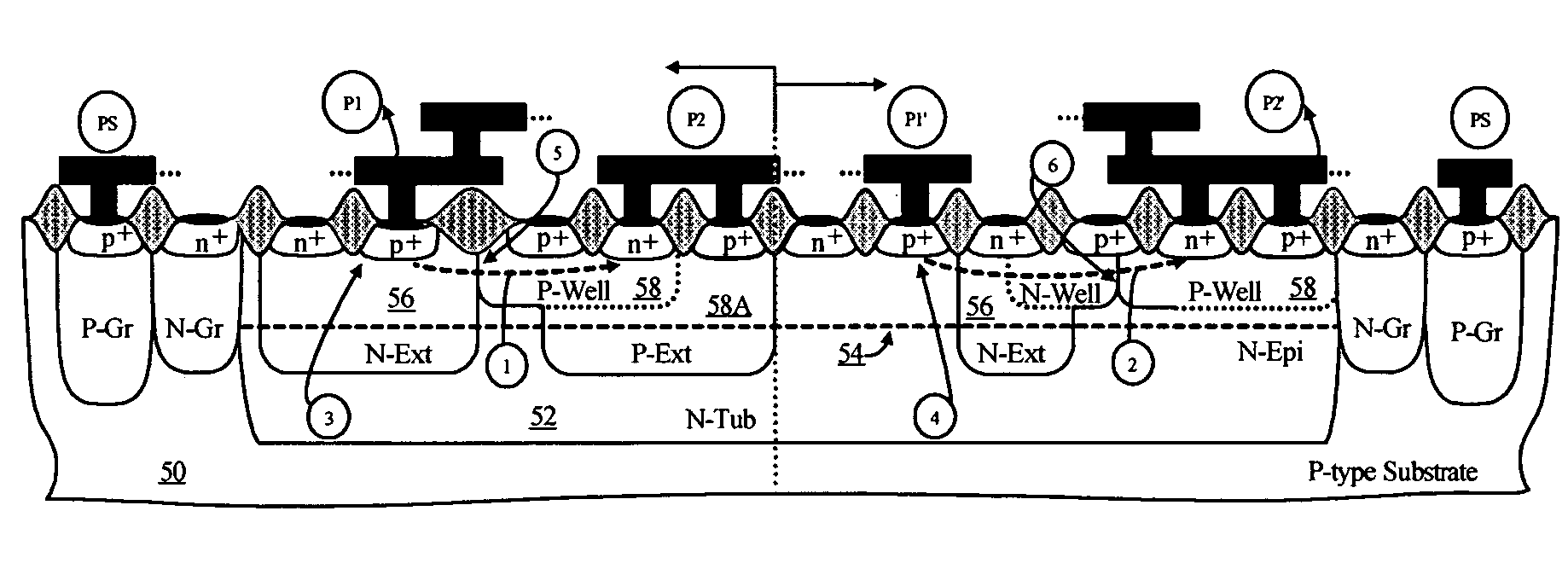

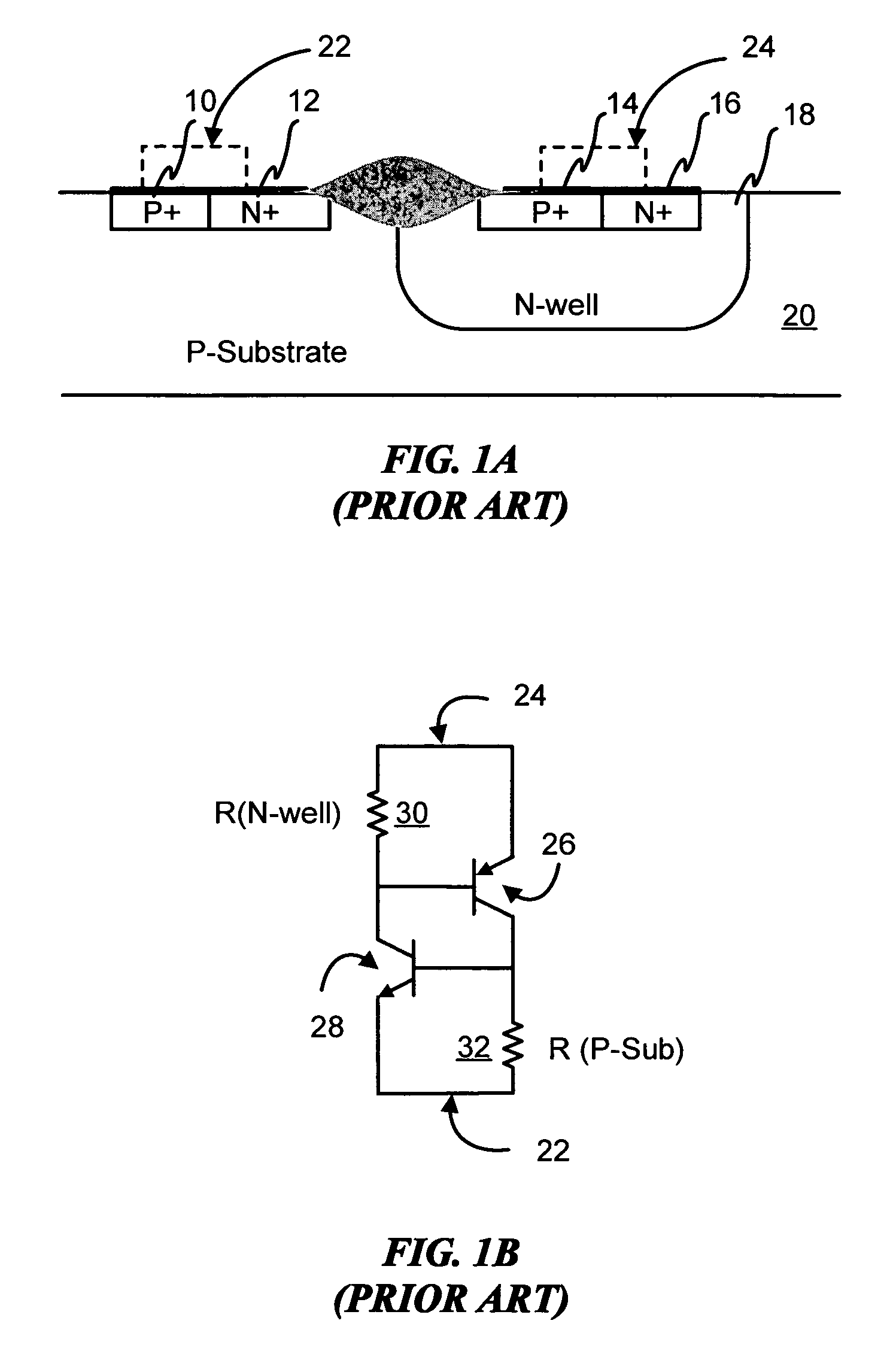

Devices with adjustable dual-polarity trigger- and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal CMOS/BiCMOS integrated circuits

InactiveUS20070007545A1Impaired immunityHigh protection levelTransistorThyristorNon symmetricTransmission-line pulse

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1-N2-P2-N1 / / N1-P3-N3-P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2 standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC +1

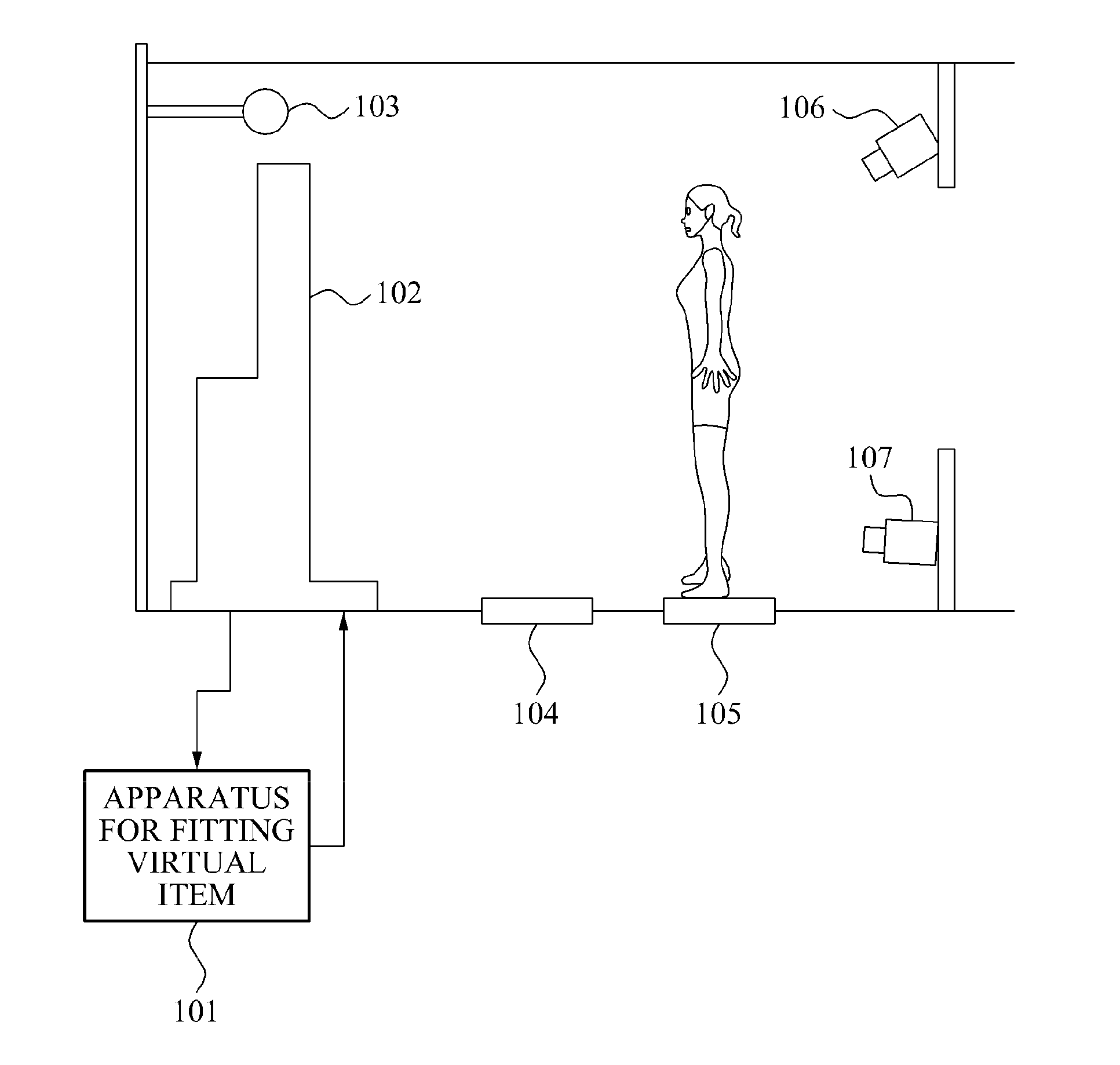

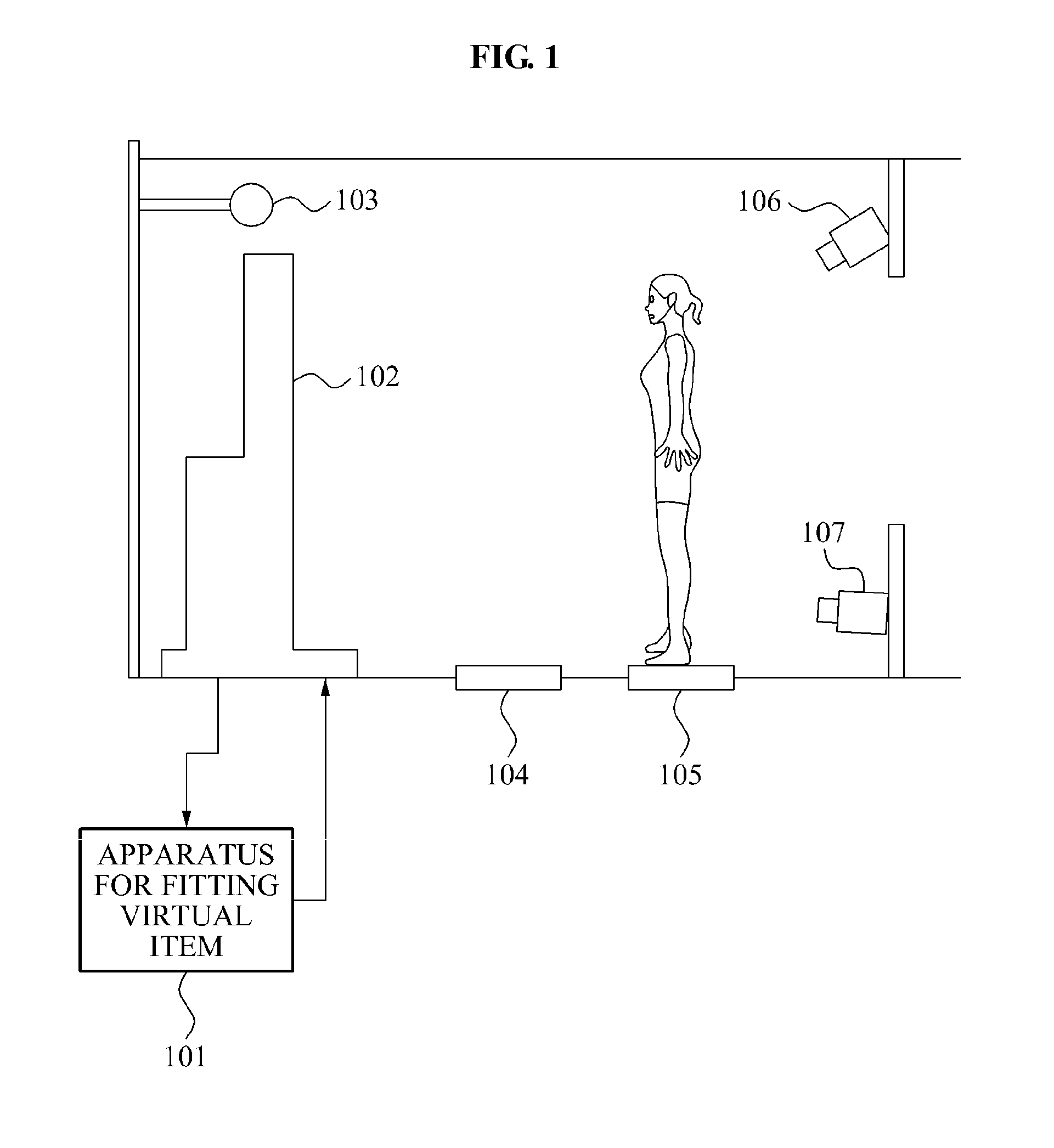

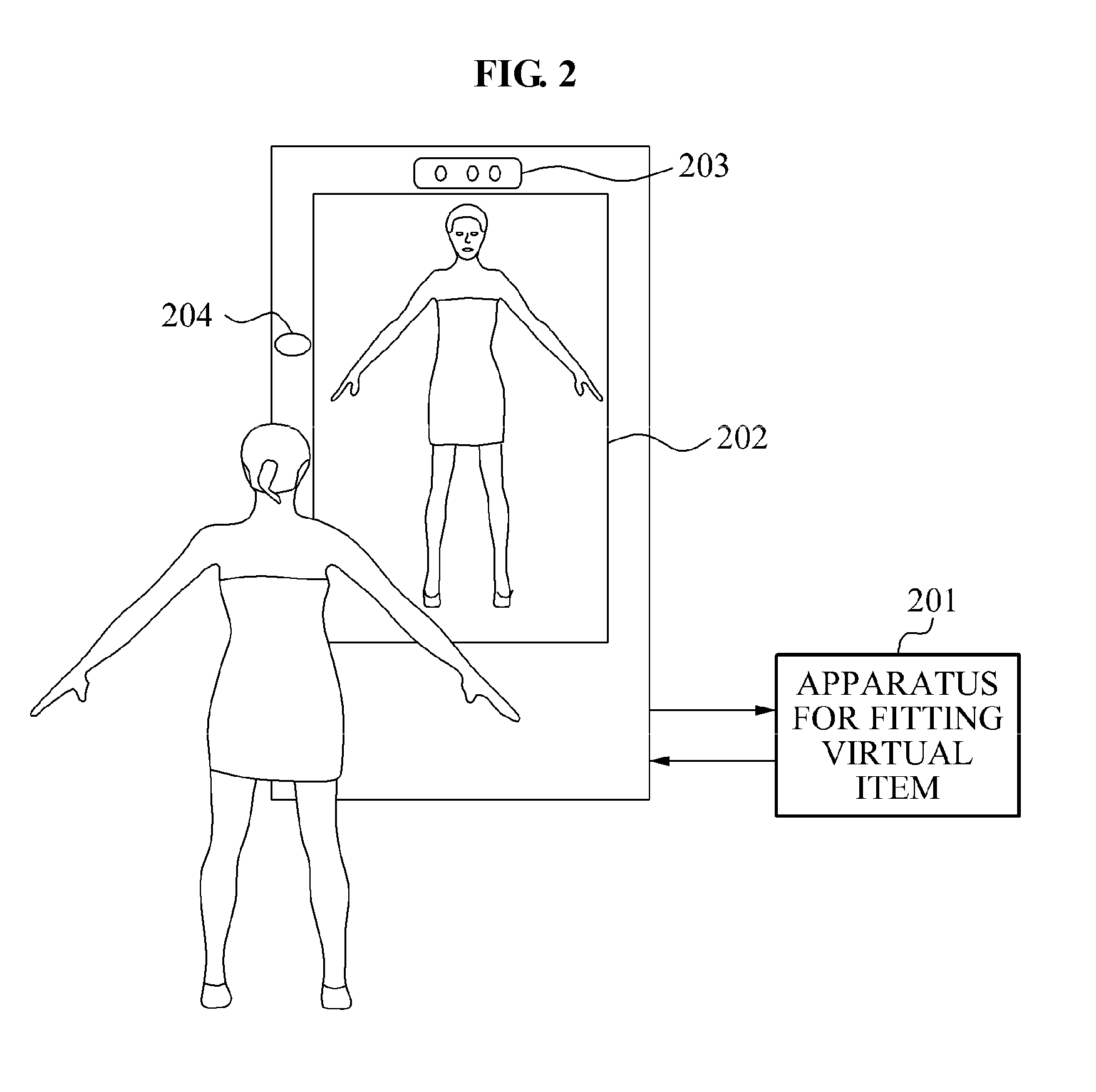

Method of fitting virtual item using human body model and system for providing fitting service of virtual item

A method of fitting a virtual item using a human body model and a system for providing a fitting service of a virtual item are provided, the method including determining whether a user is located in an experience area, loading a three-dimensional (3D) standard avatar corresponding to setting information input by the user when the user is located in the trial area, obtaining a depth image of the user corresponding to a preset posture, transforming the 3D standard avatar into a user avatar reflecting body characteristics of the user, using a depth image of the user, fitting a virtual item selected by the user to the user avatar, and applying a motion of the user changing in real time to the user avatar to which the virtual item is fitted.

Owner:ELECTRONICS & TELECOMM RES INST

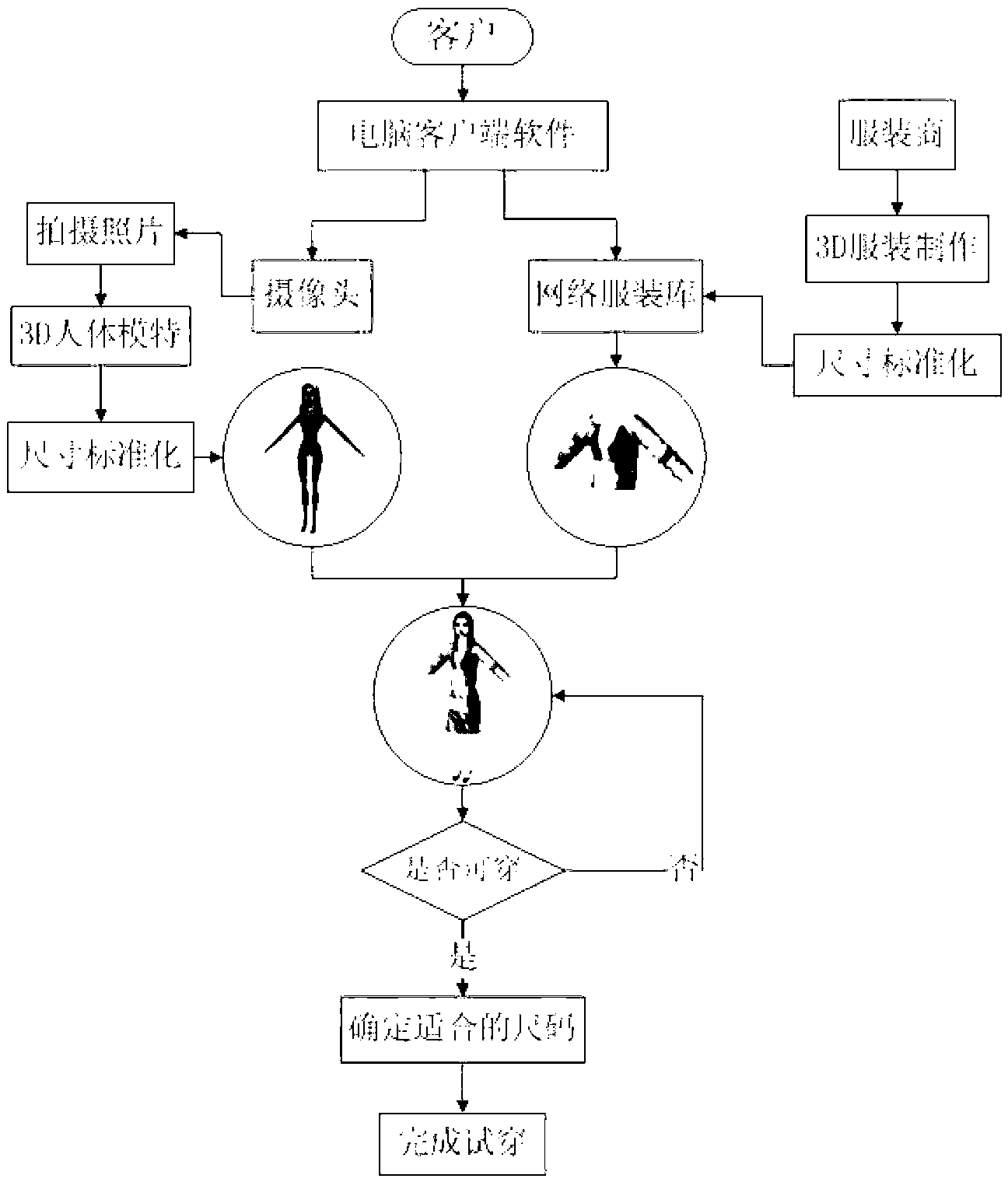

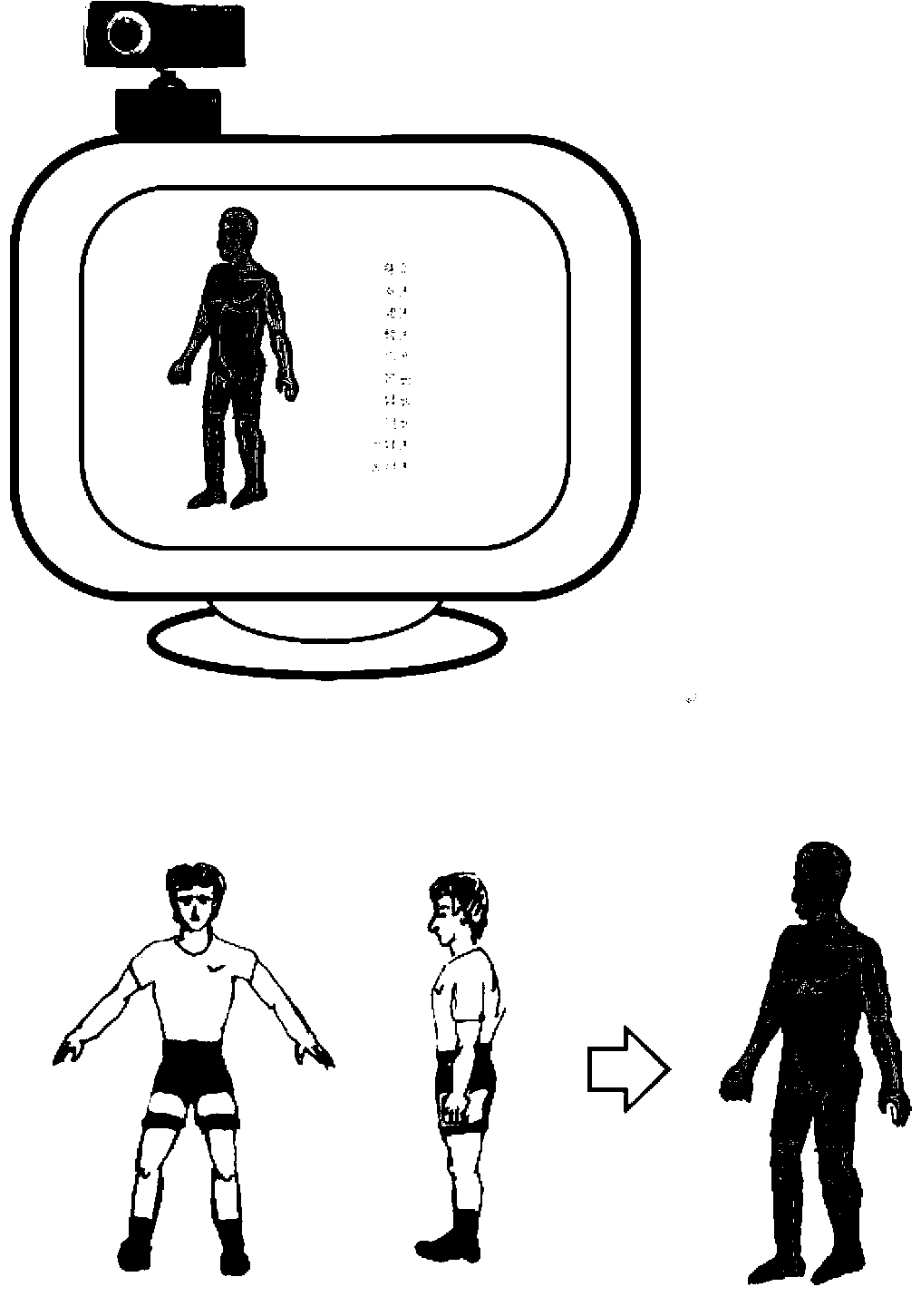

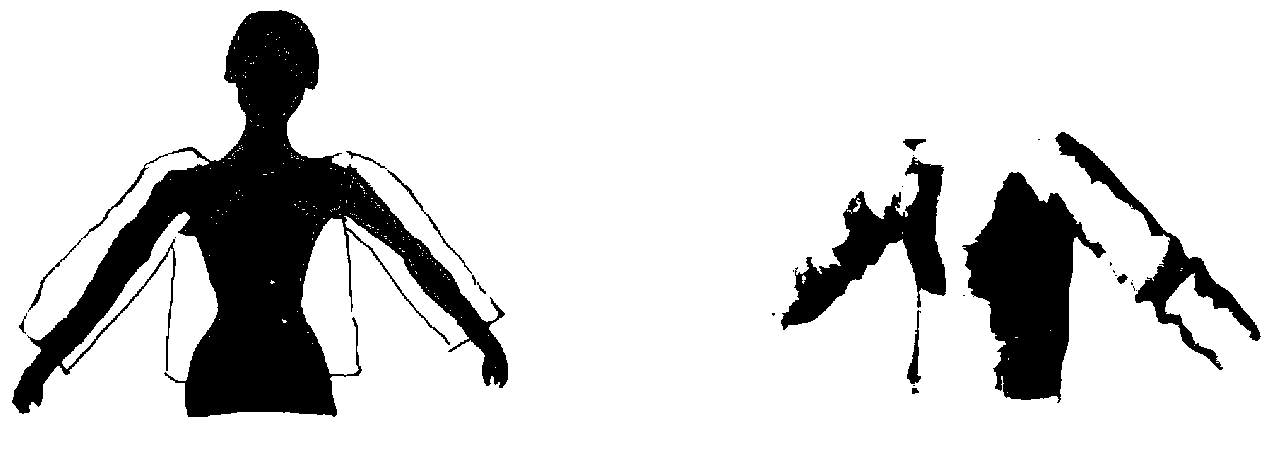

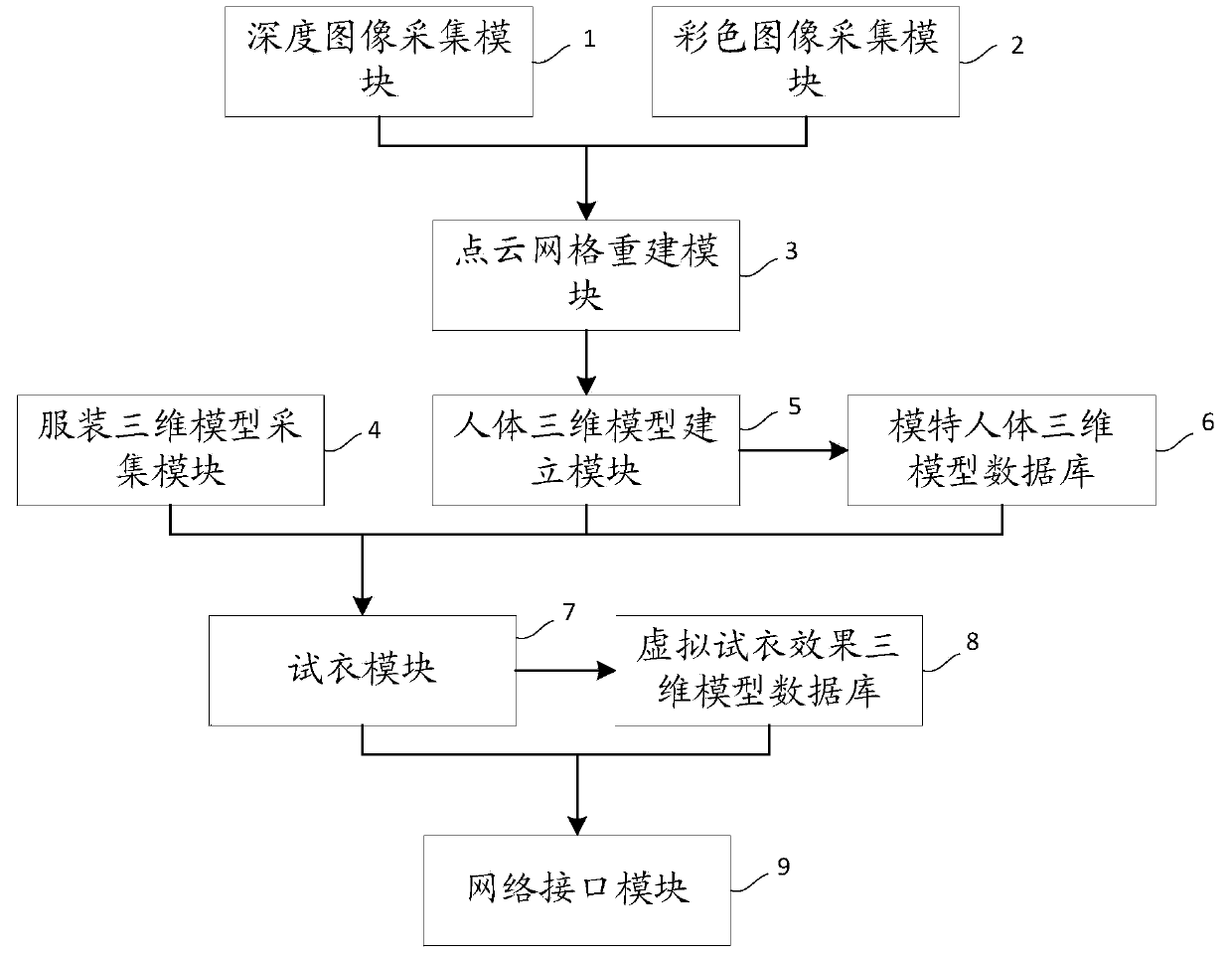

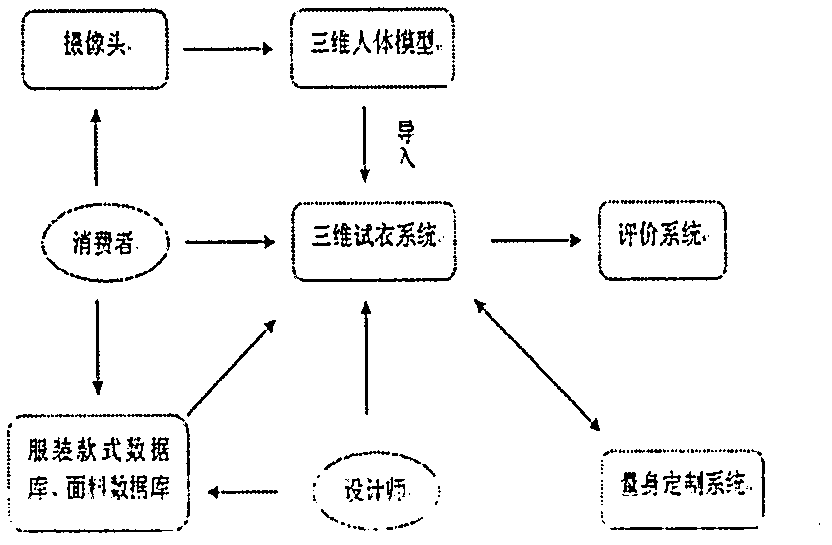

Network virtual fit system based on 3D actual human body model and clothes model

The invention discloses a network virtual fit system based on a 3D actual human body model and a clothes model. A consumer surfs the internet for browsing various brands of 3D virtual clothes, ornaments and the like provided by the network virtual fit system through client end software installed on a computer, so that matching of any clothes is carried out. 3D clothes are provided online, browsed and fitted by the network virtual fit system, and are established according clothes picture, sizes and other standard data provided by a clothes provider; the consumer can shoot a frontal image and a profile image by using a camera, a real person 3D human body model is automatically generated by using the software provided by the network virtual fit system, the network virtual fit system generates data of various figures of consumers according to heights input by the consumers and actual proportions so that fitting of the 3D virtual clothes is prepared; and the fitting of the 3D virtual clothes of the 3D human body model is carried out according to the established data of the figures of the customers and the actual sizes of the clothes under various sizes, thus the effect of various kinds of clothes with various sizes on a model can be seen, and the customers determine the sizes suitable for the customers.

Owner:SHANGHAI JIAO TONG UNIV

Devices with adjustable dual-polarity trigger- and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal CMOS/BiCMOS integrated circuits

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1-N2-P2-N1 / / N1-P3-N3-P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2 standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC +1

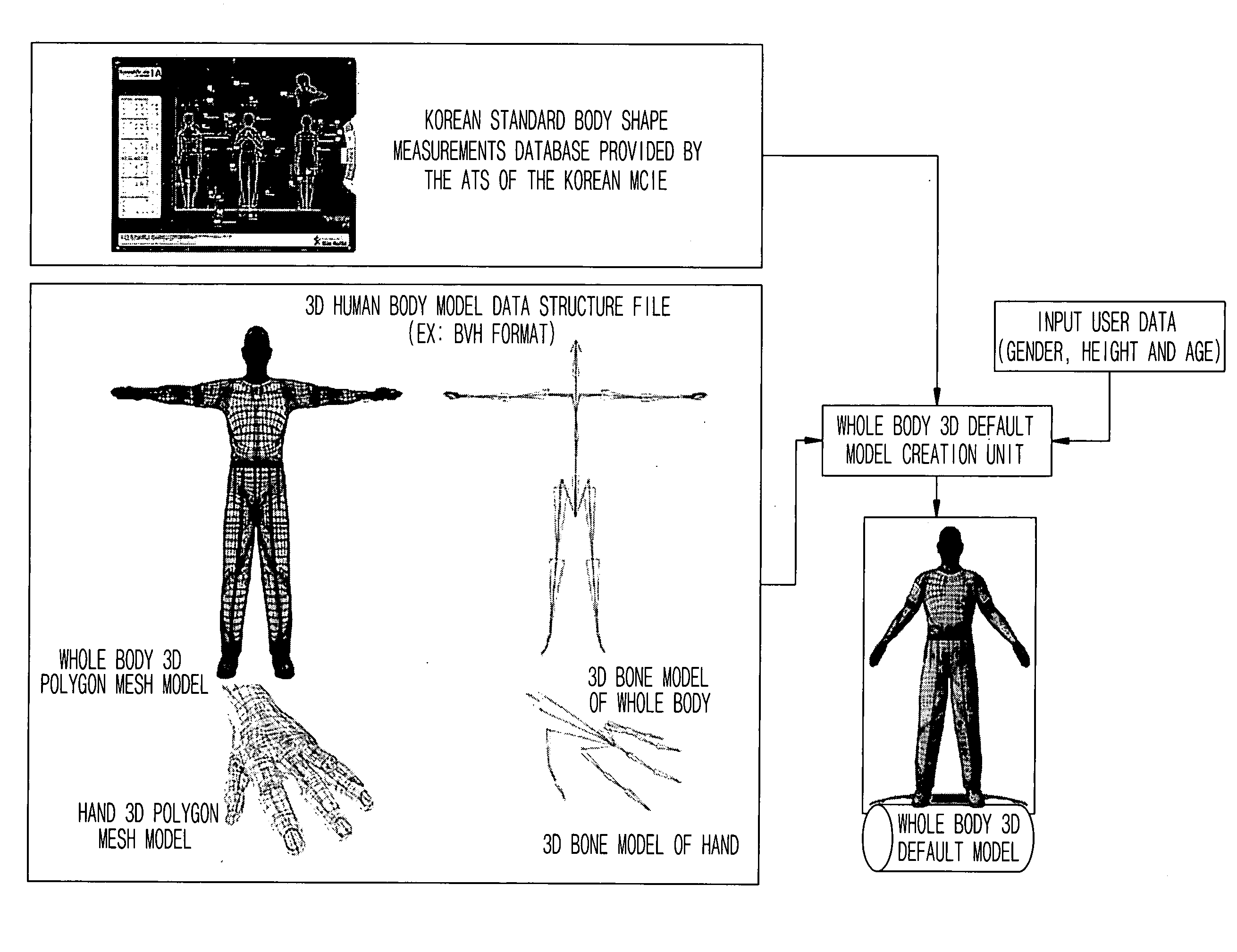

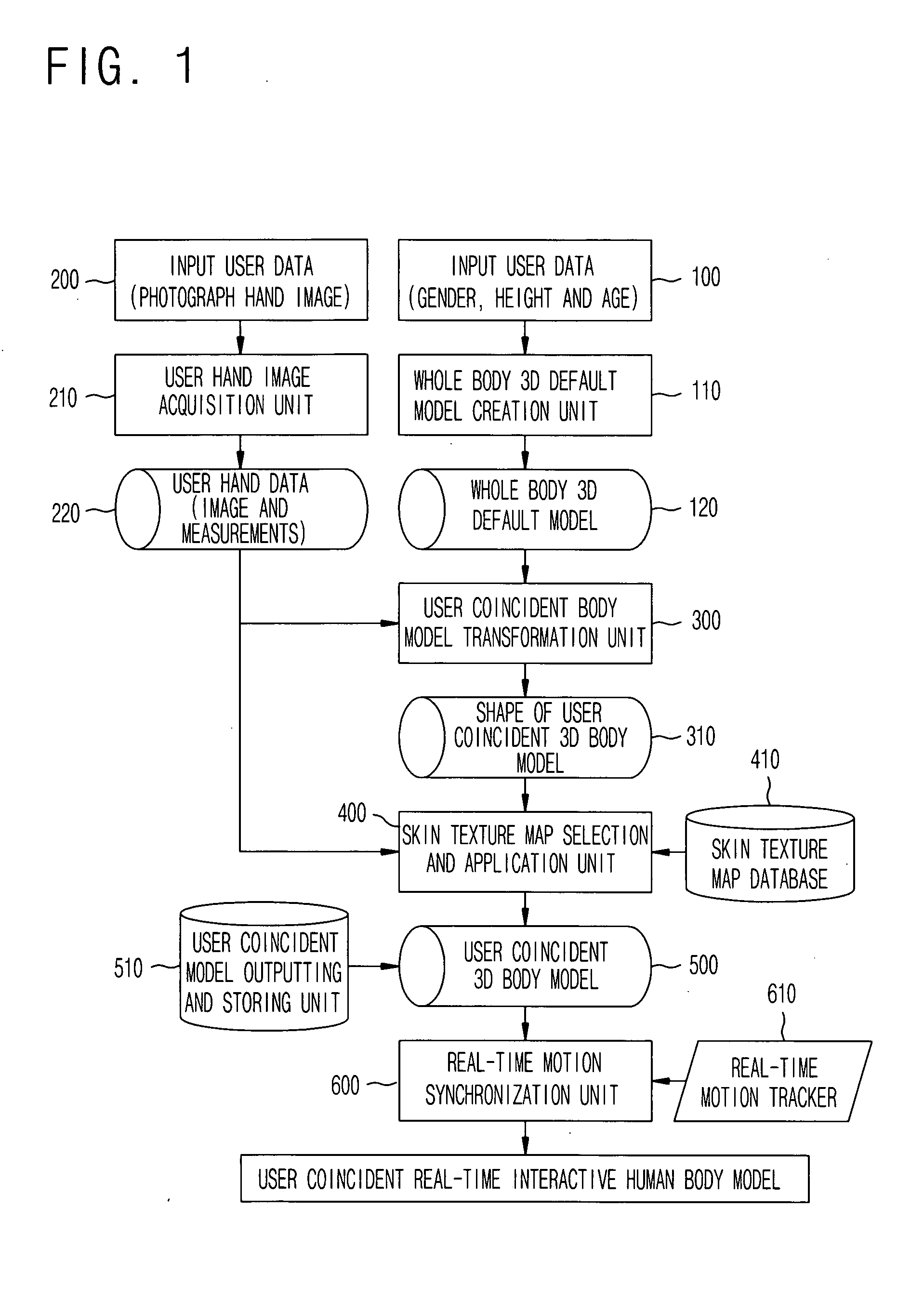

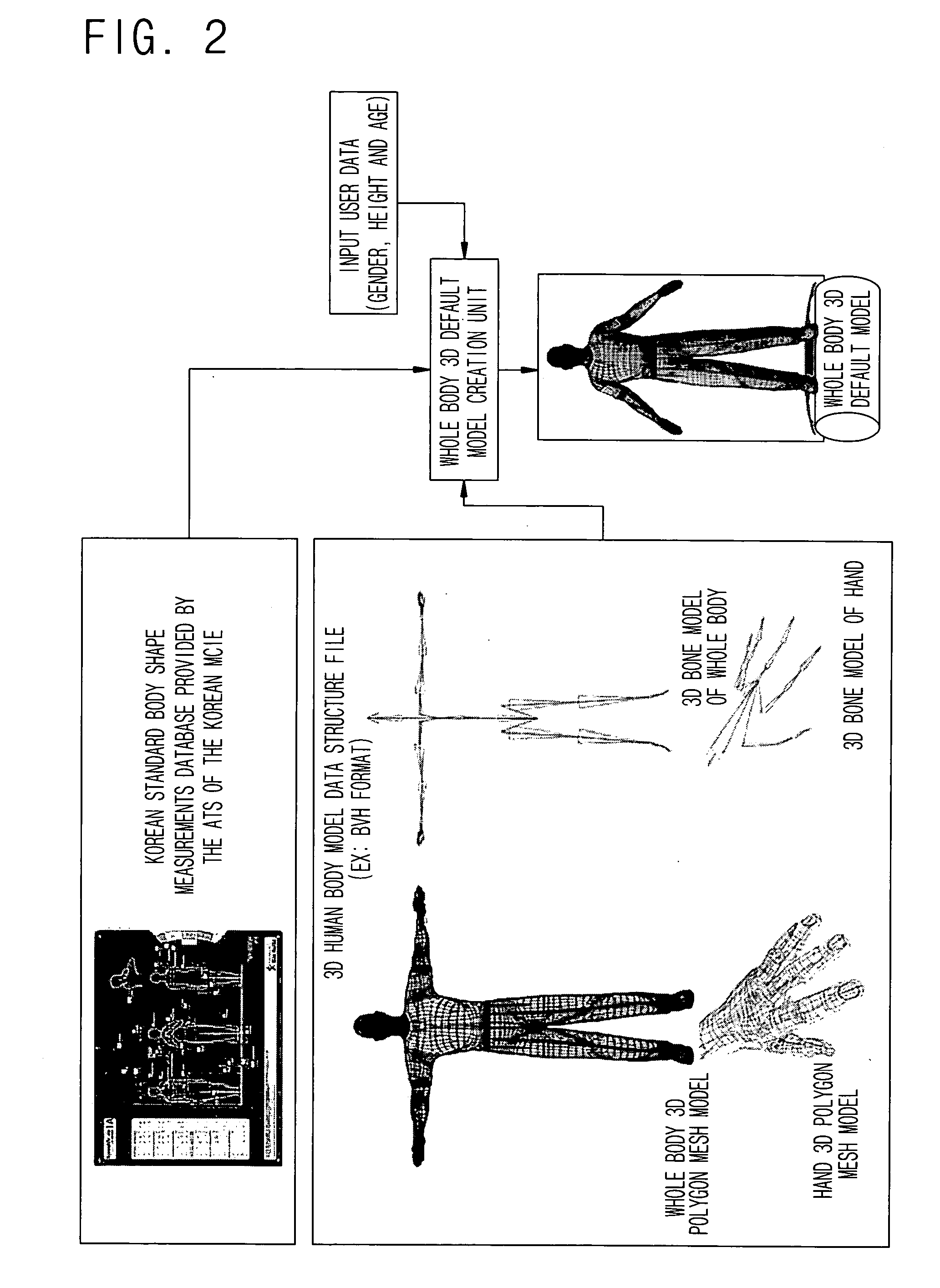

Apparatus and method for immediately creating and controlling virtual reality interactive human body model for user-centric interface

Provided is an apparatus and method for immediately creating and controlling a virtual reality interactive human body model for a user-centric interface. The apparatus and method can transform a whole body three-dimensional (3D) default model into a model close to the body of a user by collecting data from the user's hands, generates a user coincident 3D model by selecting a skin texture map and applying it to the transformed model, and controlling the user coincident 3D model in a deformable polygon mesh structure to naturally visualize the motion of the user coincident 3D model. The apparatus and method can make users participate in a virtual reality system conveniently and work naturally in the same manner as reality, i.e., interaction. The apparatus and method provides ordinary users with an easy access to virtual reality systems and overcomes the shortcomings of existing virtual reality systems which simply provide visual effects.

Owner:ELECTRONICS & TELECOMM RES INST

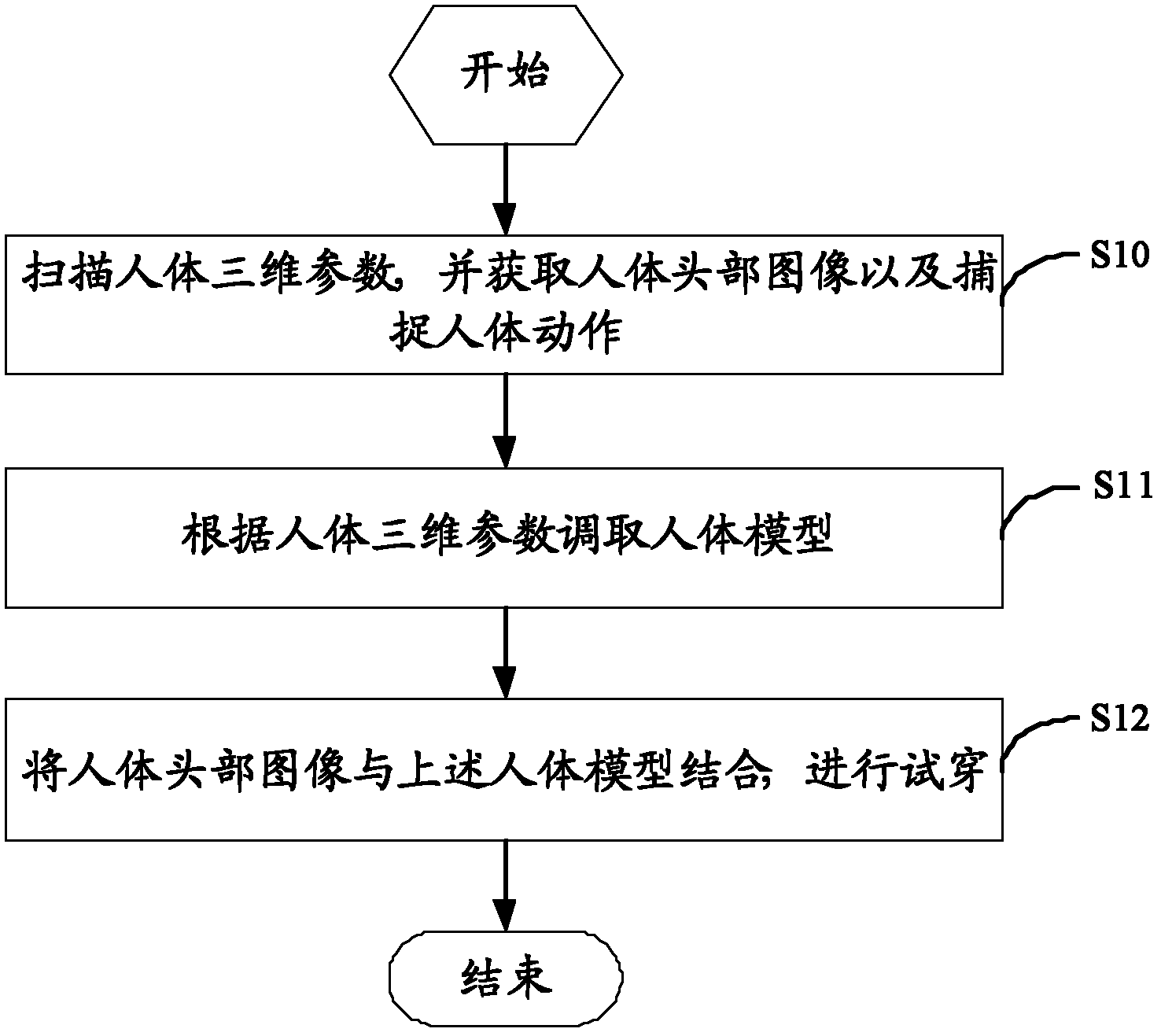

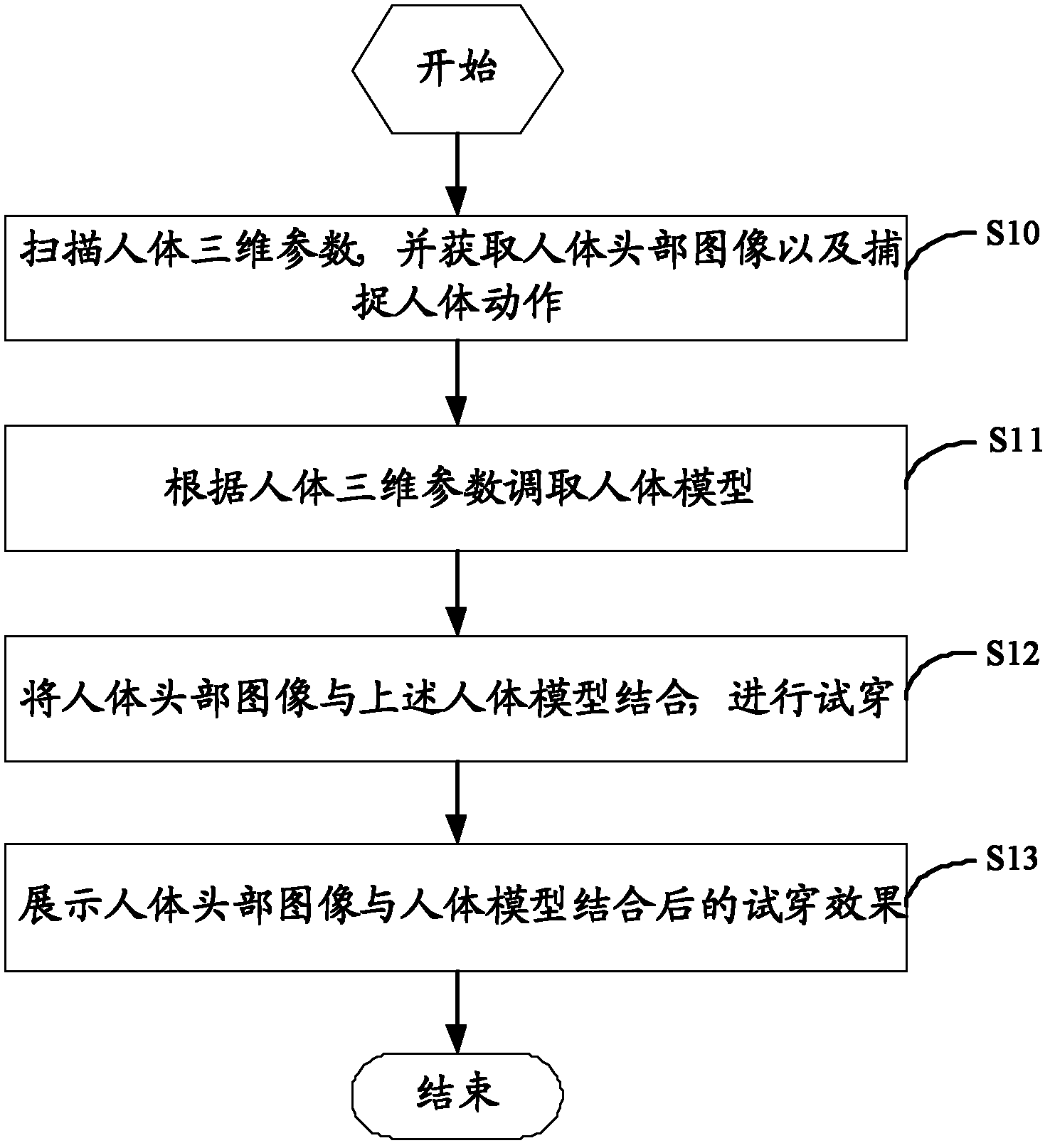

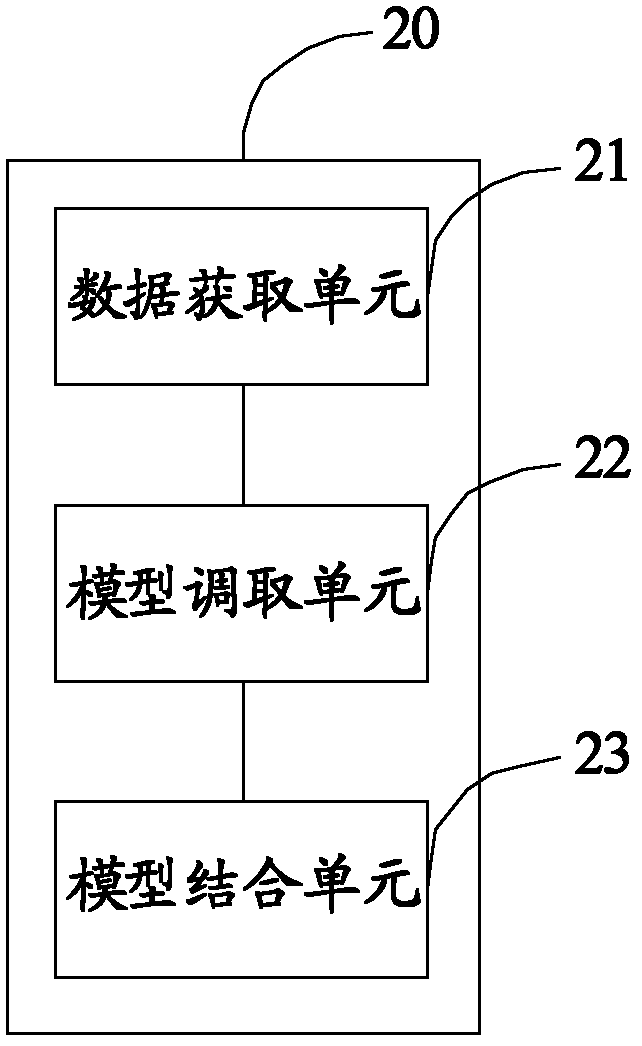

Method, device and system for three-dimensional virtual fitting

InactiveCN102298797ASpecial data processing applications3D modellingThree-dimensional spaceThree dimensional method

The invention discloses a three-dimensional virtual fitting method, device and system. The method may include the steps of: scanning the three-dimensional parameters of the human body, obtaining the head image of the human body and capturing the movement of the human body; obtaining a human body model according to the three-dimensional parameters of the human body; combining the head image of the human body with the human body model to try on. The invention combines the head image of the person trying on clothes with the human body model, so that the person trying on clothes has a more realistic feeling. At the same time, since the above-mentioned human body model is a three-dimensional model, and the human body movement is captured in time by the above-mentioned second camera in the process of the fitting person trying on clothes, it is possible to capture the fitting action and display action of the fitting person in the three-dimensional space in real time, Fully displayed.

Owner:深圳市美丽同盟科技有限公司

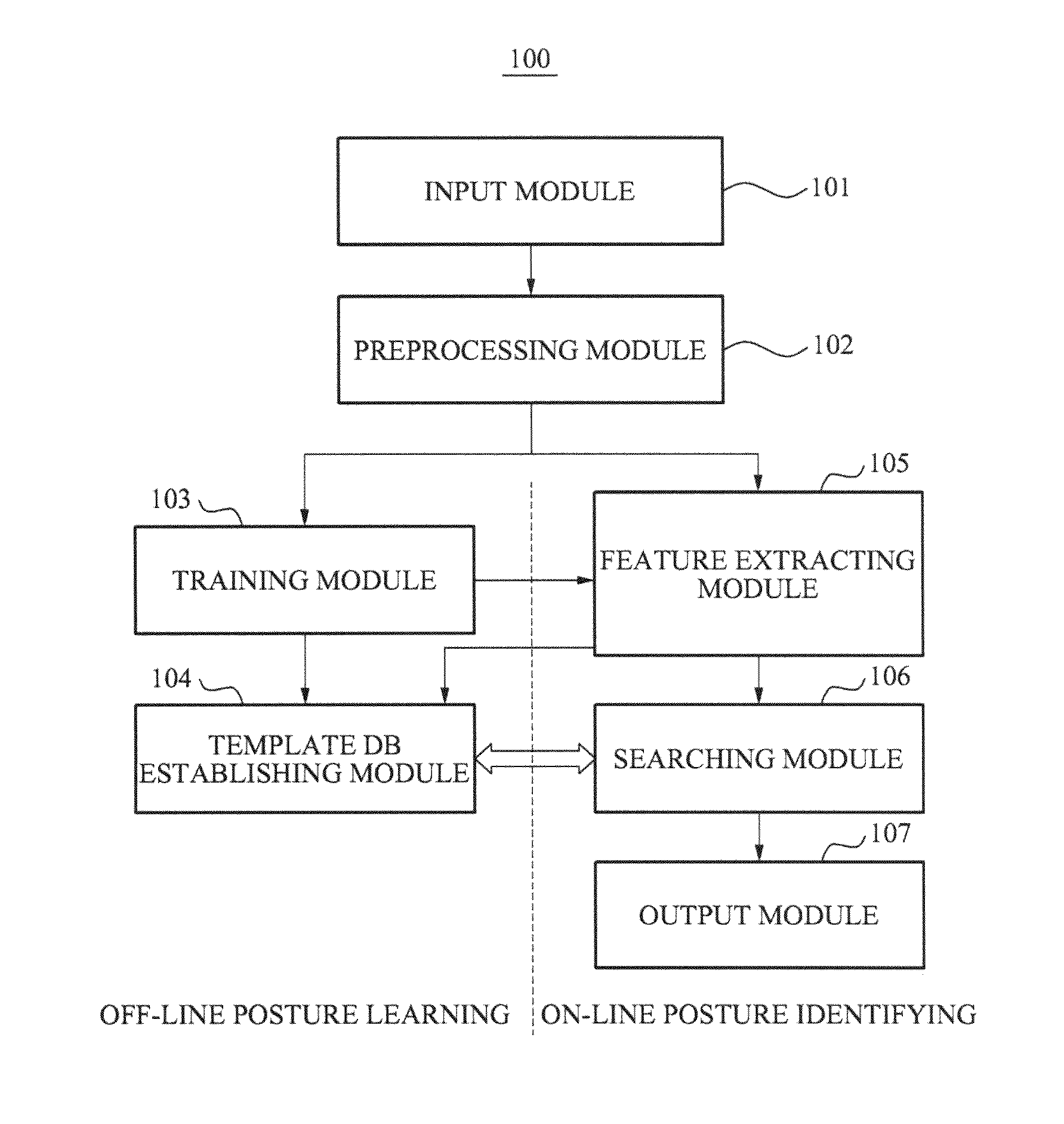

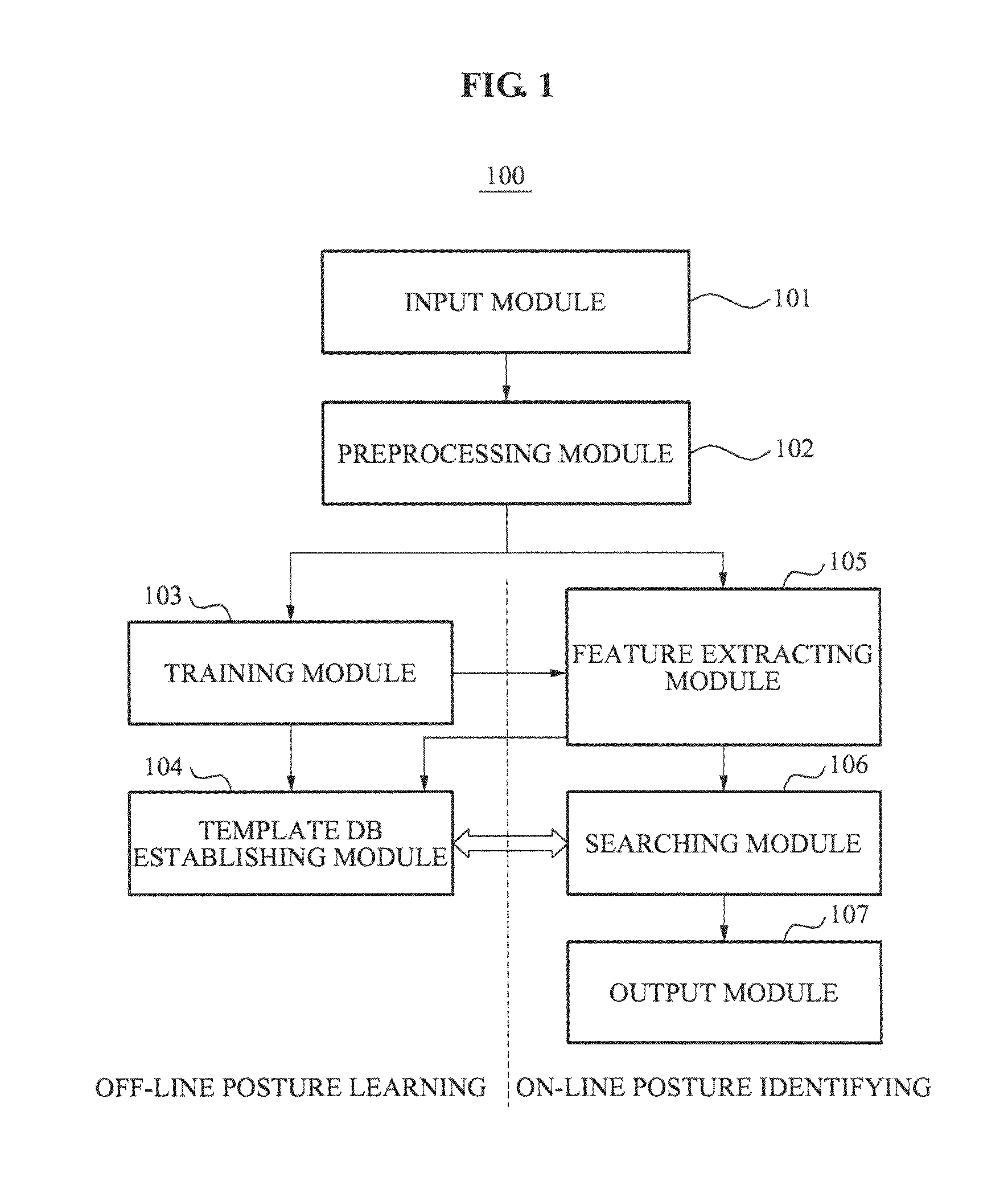

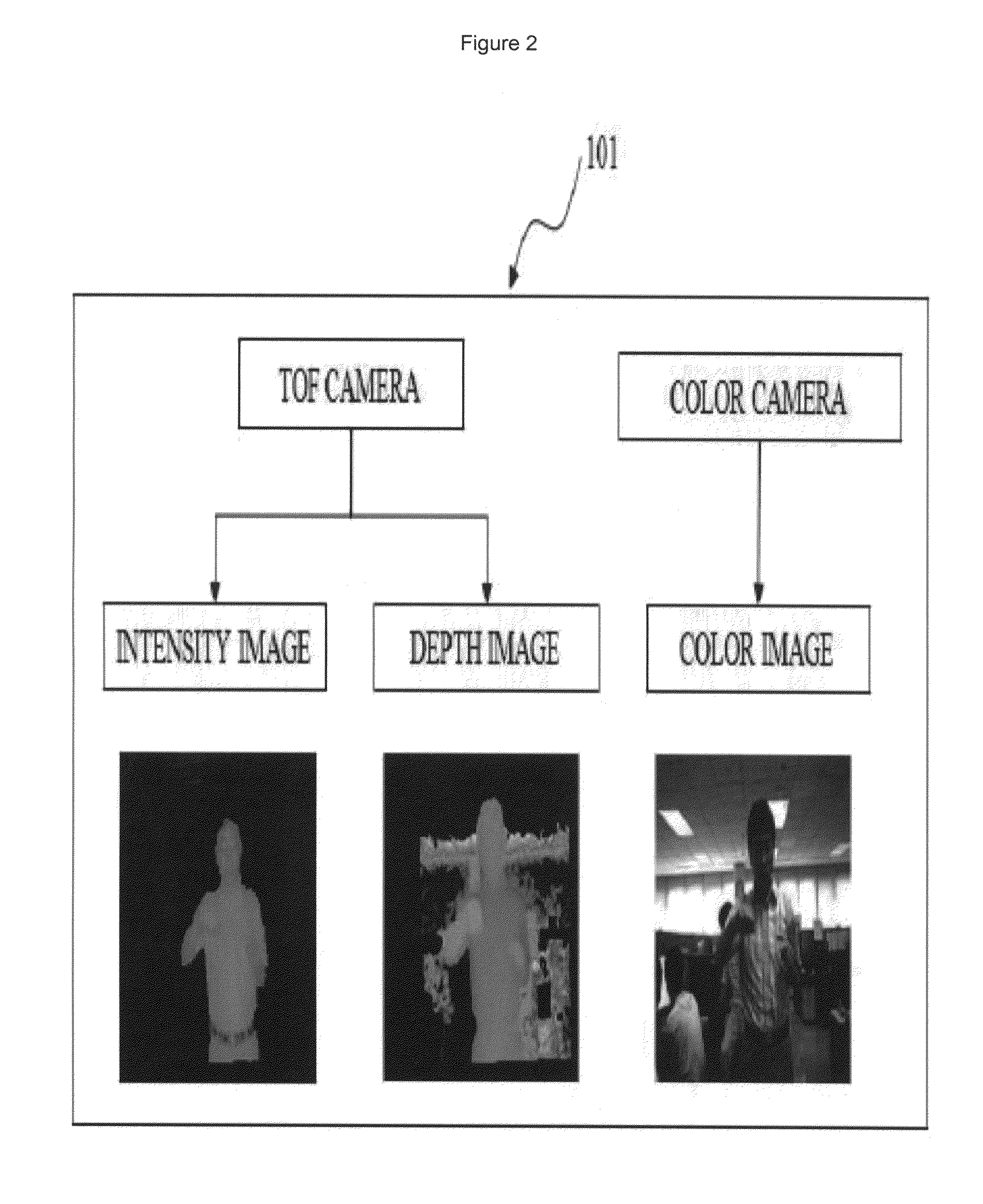

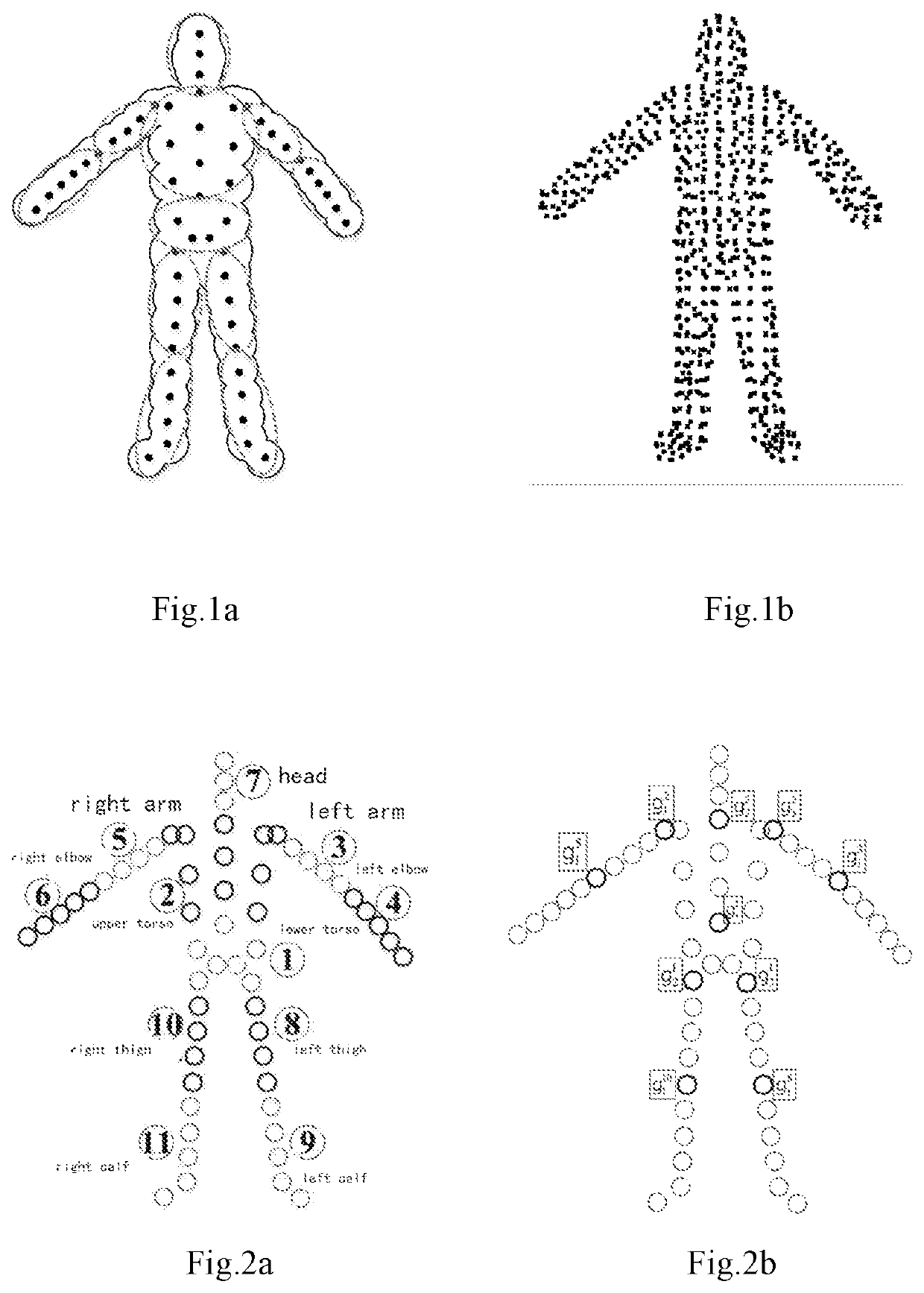

Method and apparatus of identifying human body posture

InactiveUS20110025834A1Efficient identificationImage enhancementImage analysisHuman bodyFeature extraction

Disclosed is a human body posture identifying method and apparatus. The apparatus may include an input module including a depth camera and a color camera, a preprocessing module to perform a preprocess and to generate a posture sample, a training module to calculate a projective transformation matrix, and to establish a NNC, a feature extracting module to extract a distinguishing posture feature, a template database establishing module to establish a posture template database, a searching module to perform a human body posture matching, and an output module to output a best match posture, and to relocate a location of a virtual human body model.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and system for markerless motion capture using multiple cameras

InactiveUS8023726B2Accurate estimateAccurate presentationImage enhancementDetails involving processing stepsPattern recognitionVoxel

Completely automated end-to-end method and system for markerless motion capture performs segmentation of articulating objects in Laplacian Eigenspace and is applicable to handling of the poses of some complexity. 3D voxel representation of acquired images are mapped to a higher dimensional space (k), where k depends on the number of articulated chains of the subject body, so as to extract the 1-D representations of the articulating chains. A bottom-up approach is suggested in order to build a parametric (spline-based) representation of a general articulated body in the high dimensional space followed by a top-down probabilistic approach that registers the segments to an average human body model. The parameters of the model are further optimized using the segmented and registered voxels.

Owner:UNIV OF MARYLAND

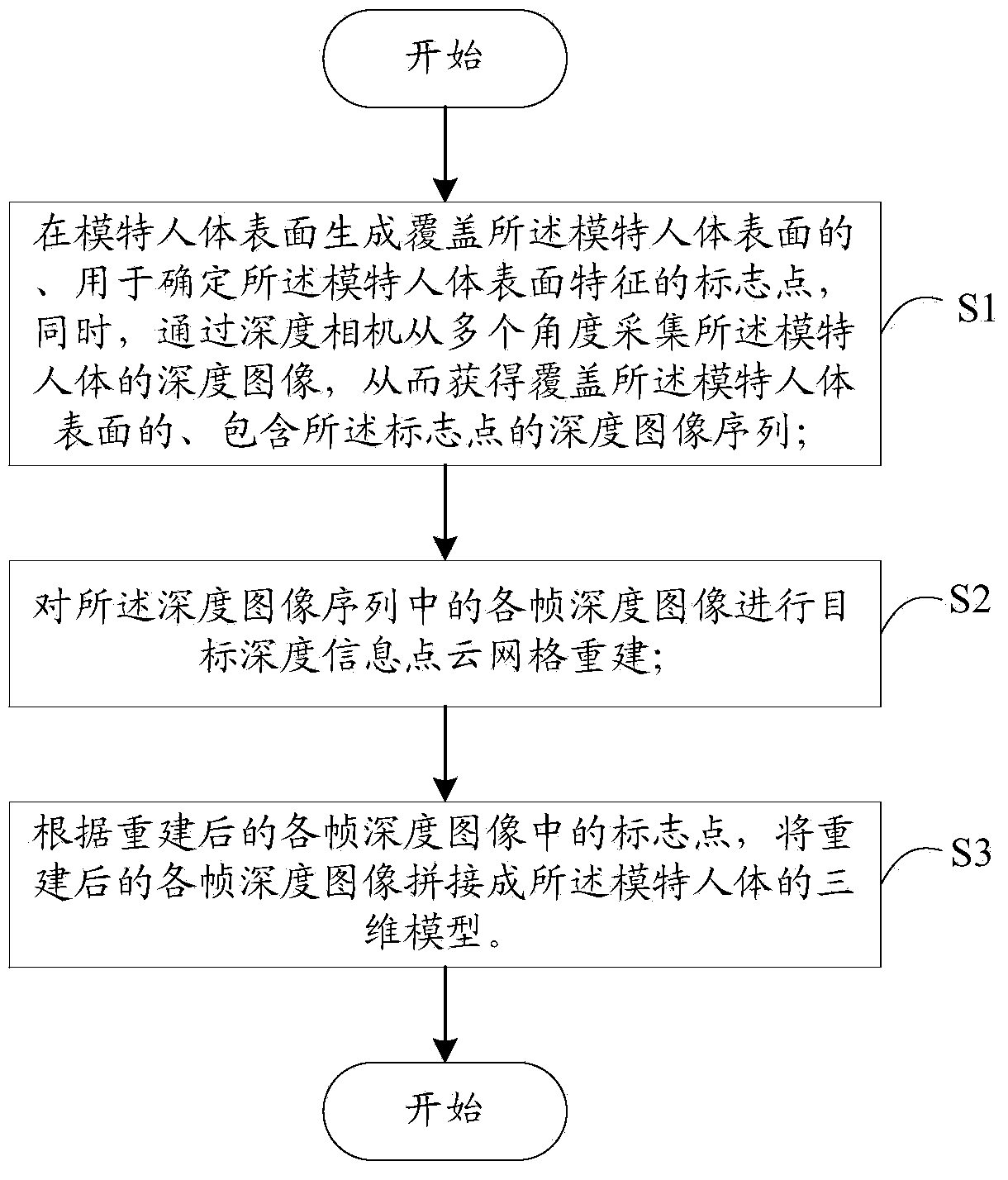

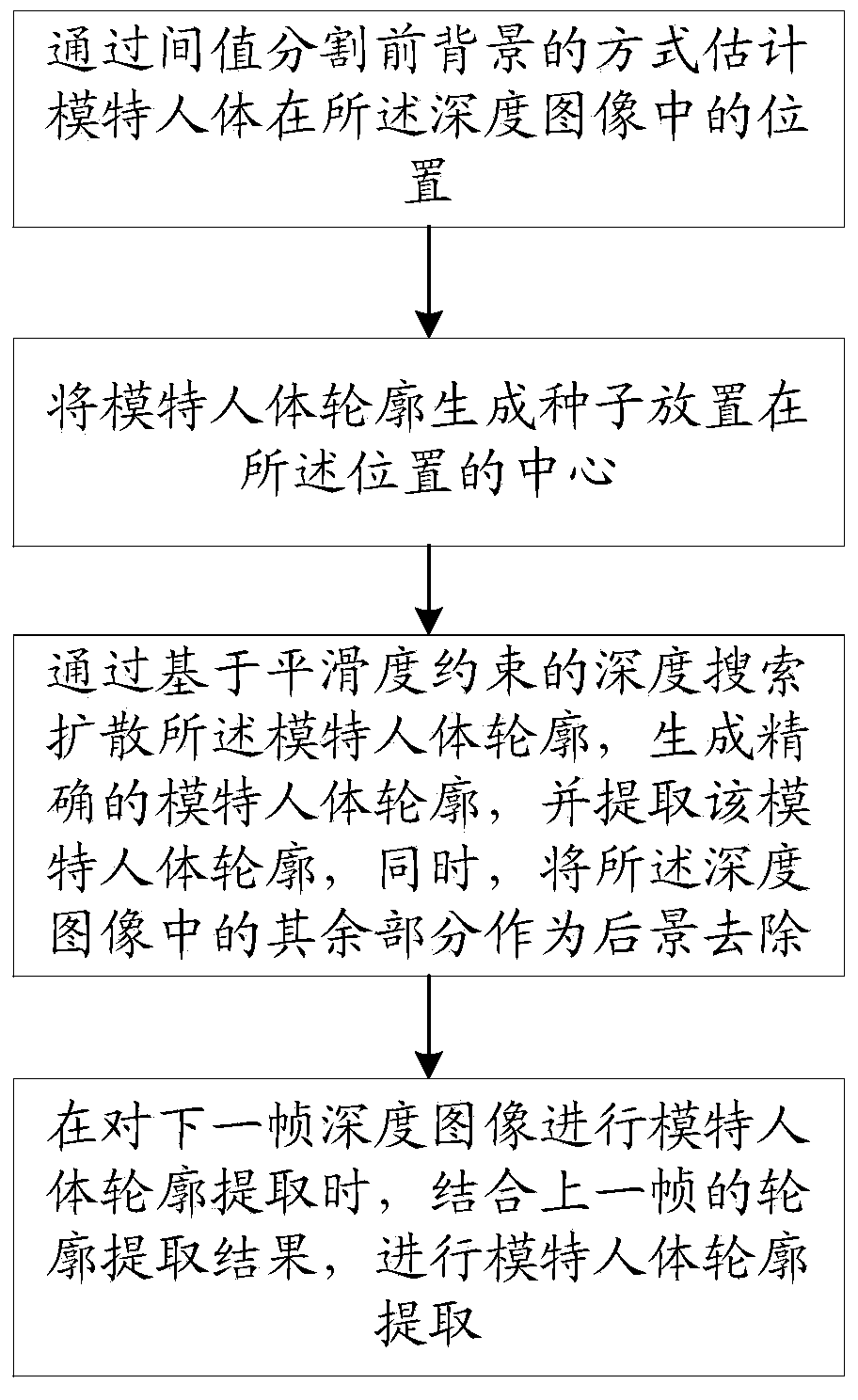

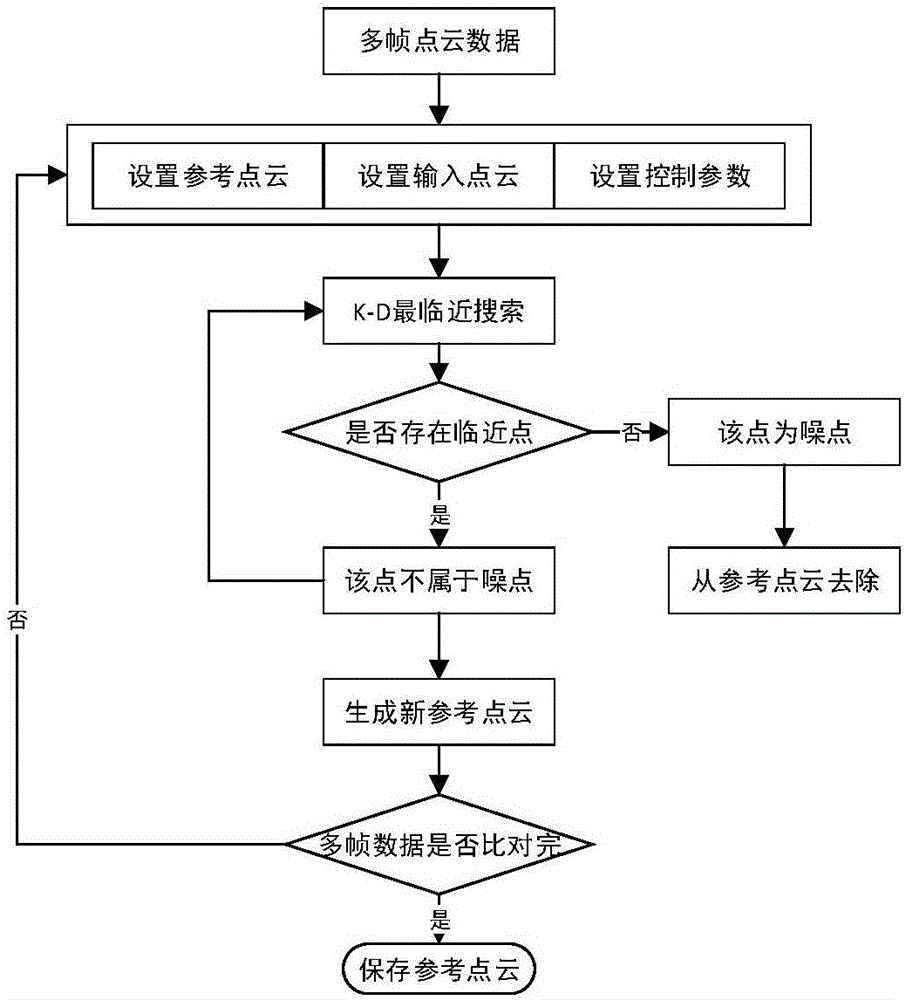

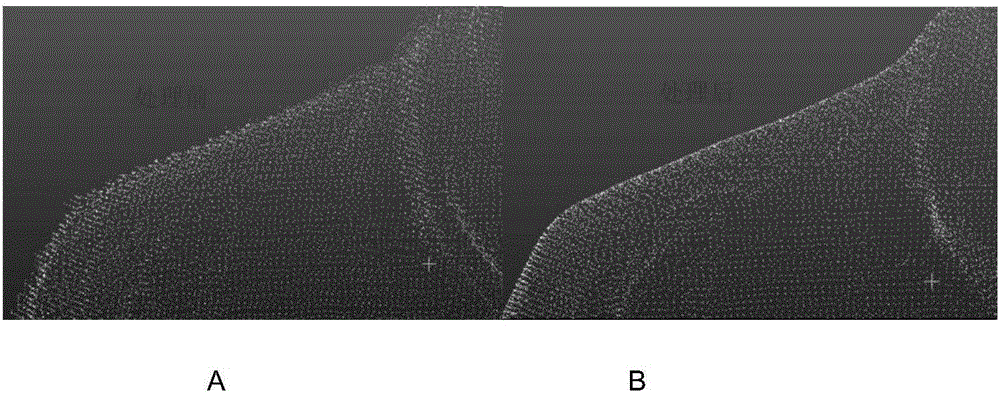

Human body model obtaining method and network virtual fitting system based on depth camera

ActiveCN104008571AReal try-on effectDetails involving processing stepsImage enhancementHuman bodyPoint cloud

The invention relates to a human body model obtaining method and a network virtual fitting system based on a depth camera. The method comprises the steps of 1, generating mark points on the surface of a model human body, meanwhile, collecting depth images of the model human body from multiple angles through the depth camera, and therefore obtaining depth image sequences covering the surface of the model human body and comprising the mark points, wherein the mark points cover the surface of the model human body and are used for determining characteristics of the surface of the model human body; 2, performing target depth information point cloud network reconstruction on each frame of depth images in the depth image sequences; 3, splicing the reconstructed depth images into a three-dimensional model of the model human body according to the reconstructed mark points in the depth images. Compared with the prior art, the human body model obtaining method and the network virtual fitting system based on the depth camera can obtain the accurate human body three-dimensional model and the garment three-dimensional model, virtual fitting is achieved according to the models, and the real fitting effect can be obtained.

Owner:SHENZHEN ORBBEC CO LTD

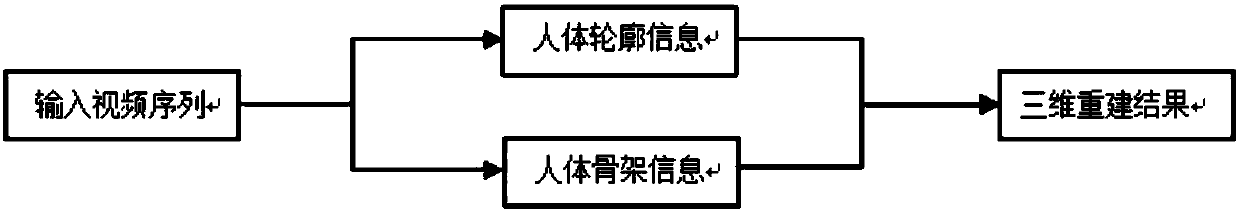

Human body 3D reconstruction method and device for complex dynamic scene under multi-view camera

The invention discloses a human body 3D reconstruction method and device for a complex dynamic scene under a multi-view camera. The method comprises the following steps: photographing a target human body object at multiple views to obtain 2D images at multiple views under the same moment; predicting all the parts of the human body in the video sequence through a model after deep network learning to obtain the human body skeleton information of the human body; matching the movement and rough contour of the character in the images through a virtual 3D human body model according to the skeleton information to obtain the human body contour information of the human body; and carrying out human body 3D modeling through a Virtual Hull method according to the calibrated internal and external parameter information of the camera at multiple views as well as the human body skeleton information and the human body contour information. Through the method, 3D reconstruction of a human body object ina video sequence can be realized through camera calibration and other processes, and therefore, accurate character object segmentation is realized, and the accuracy and reliability of reconstruction are improved.

Owner:TSINGHUA UNIV

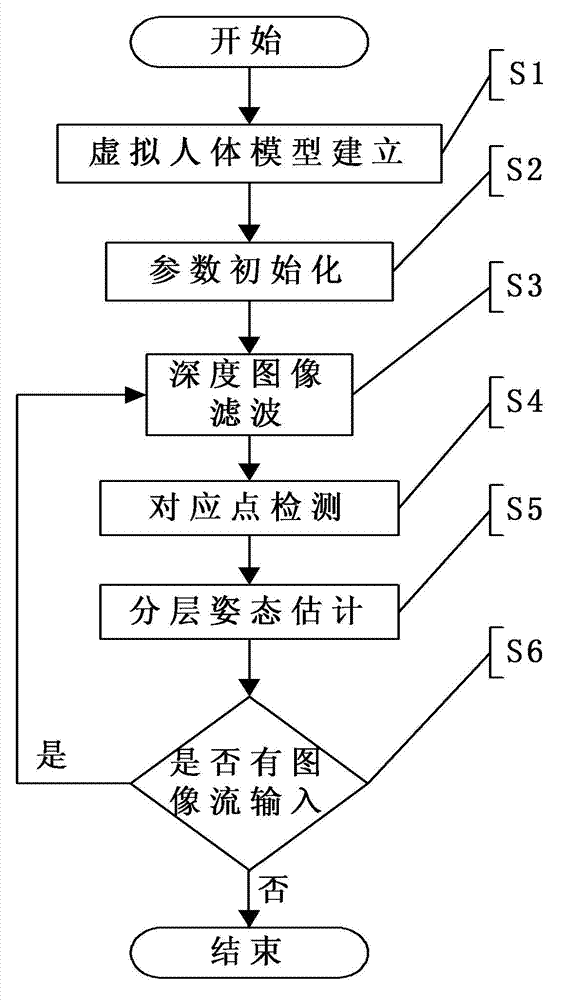

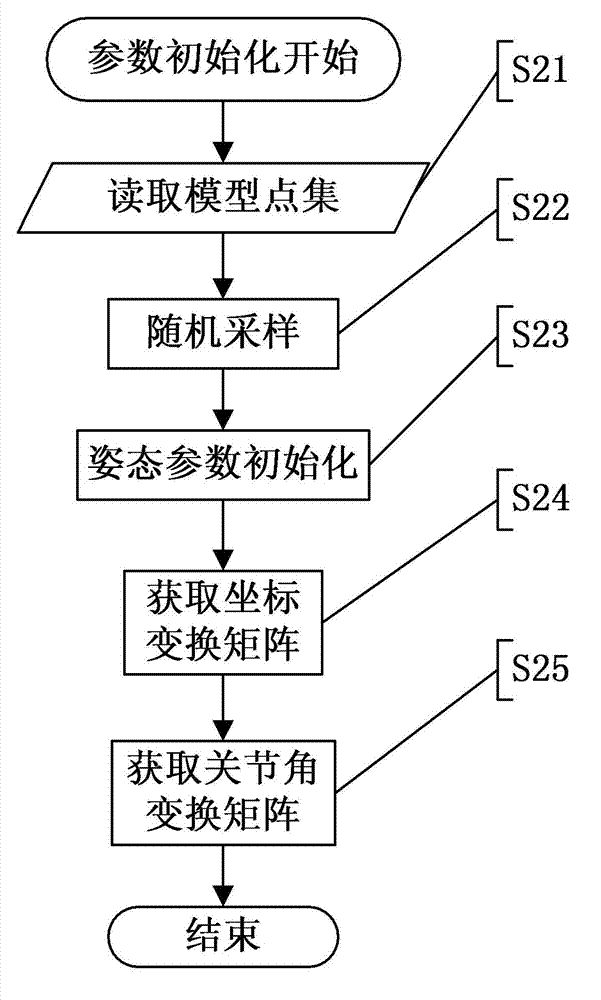

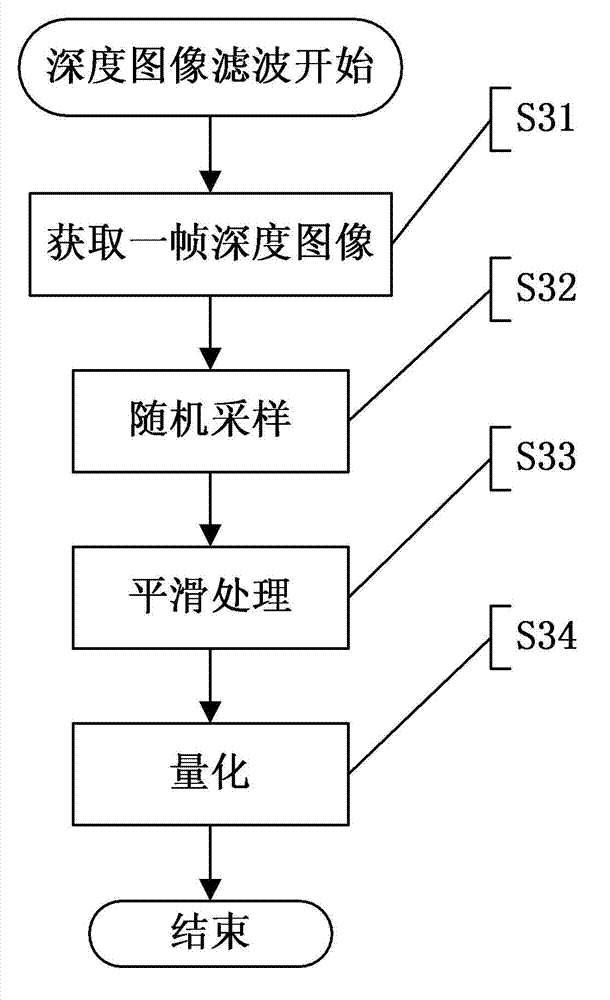

Estimation method of human posture based on depth image

ActiveCN102855470AIncrease freedomPose estimation converges fastCharacter and pattern recognitionHuman bodyDeformation effect

The invention discloses an estimation method of a human posture based on a depth image. The method estimates the human posture according to the depth image of a human body and simulates the human body in the image through a virtual human body model. The depth image includes a plurality of frames. The method includes the steps of building the virtual human body model composed of a skeleton model and a skin model; initializing parameters of the virtual human body model; filtering a current frame of the depth image; performing corresponding point detection on the virtual human body model and the depth image; and building and optimizing an objective function for the current frame of the depth image according to results of the corresponding point detection, and updating a current posture of the virtual human body model through the value of a minimized objective function, wherein the objective function is used for describing the posture difference between the virtual human body model and the depth image. The virtual human body model built in the estimation method is high in degree of freedom and good in skin deformation effect, the convergence rate of posture estimation is high, errors are small, simultaneously, a depth camera is used for obtaining depth images, so that devices of a human motion posture estimation system are simple, and popularization and application are facilitated.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

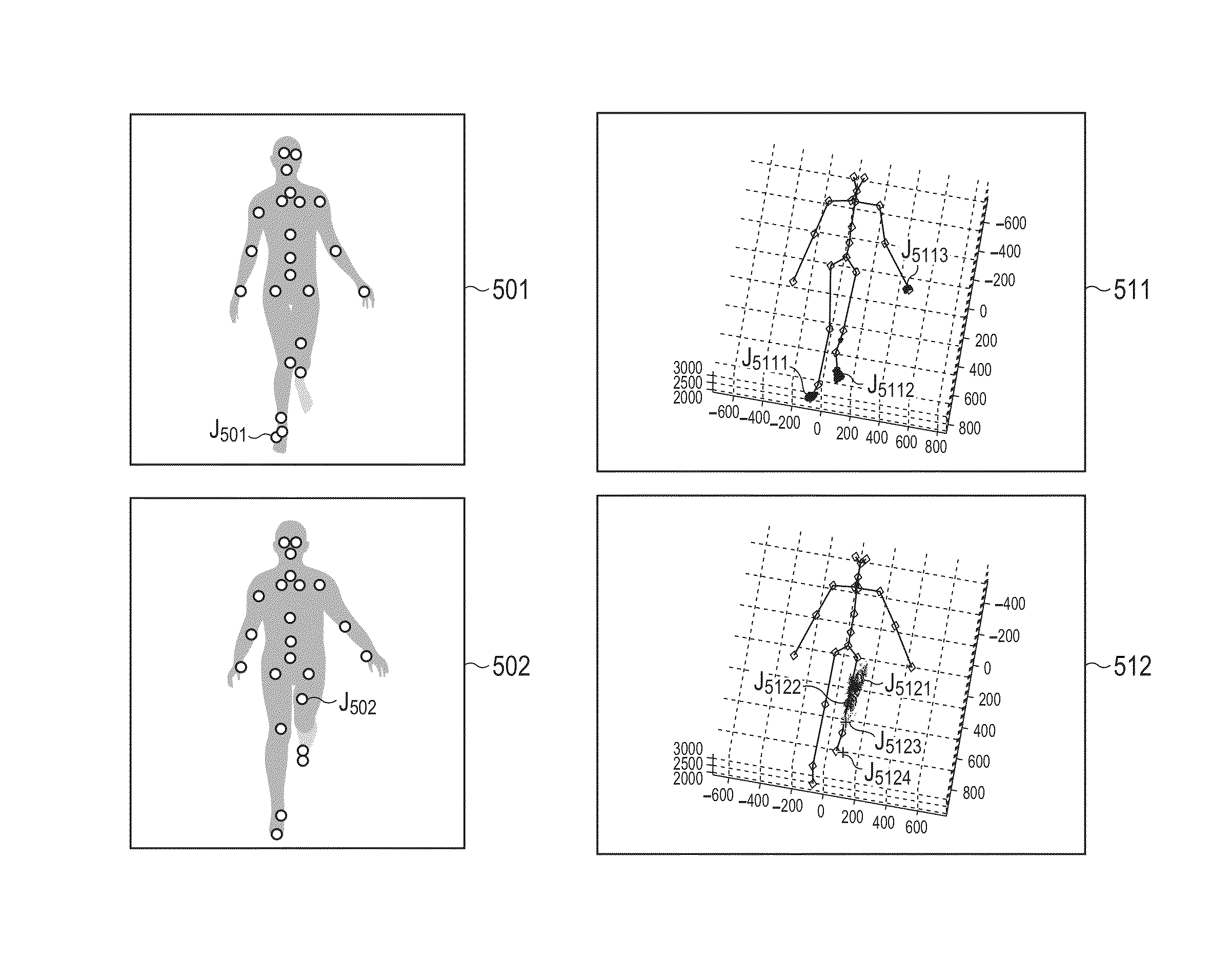

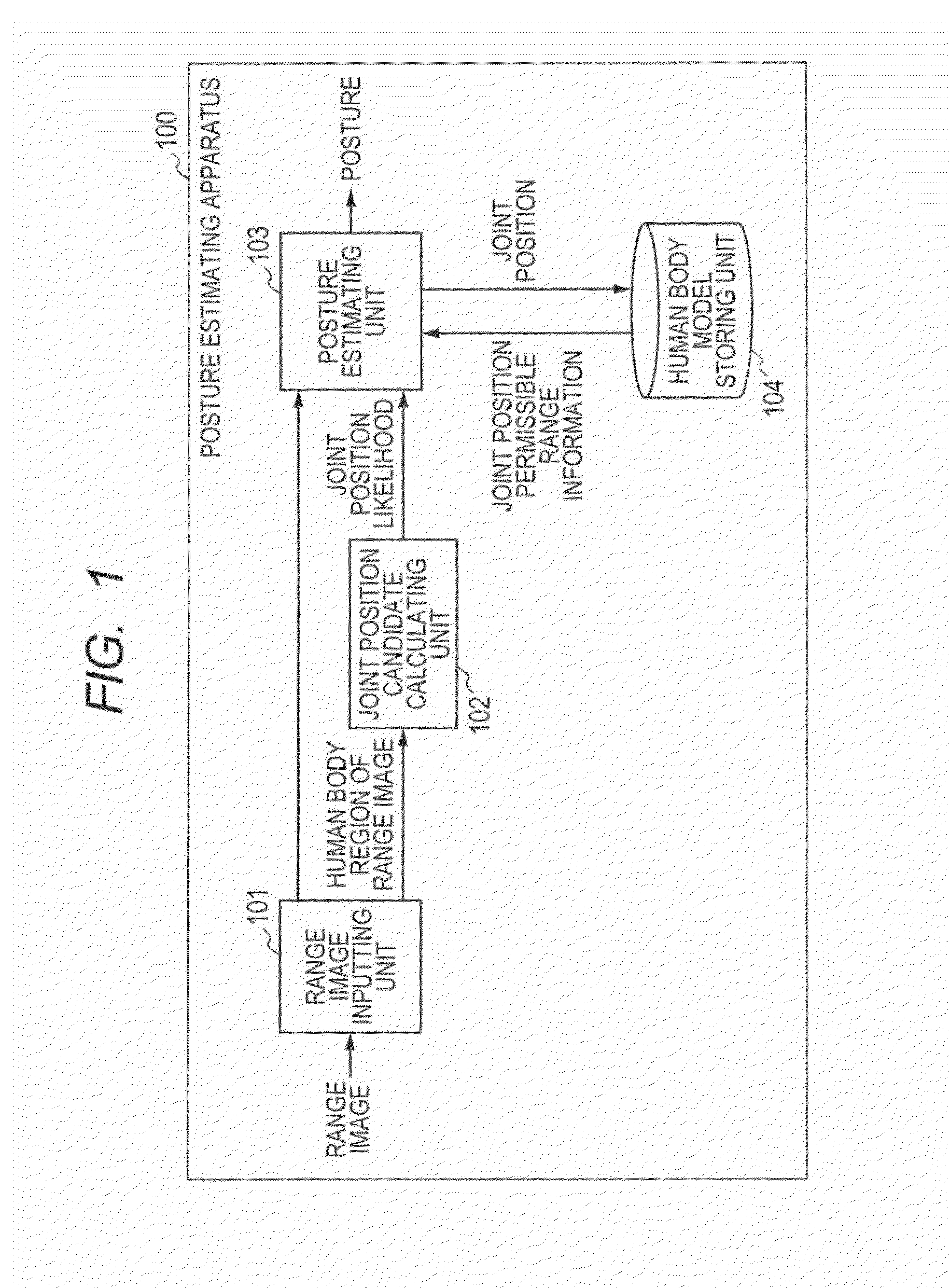

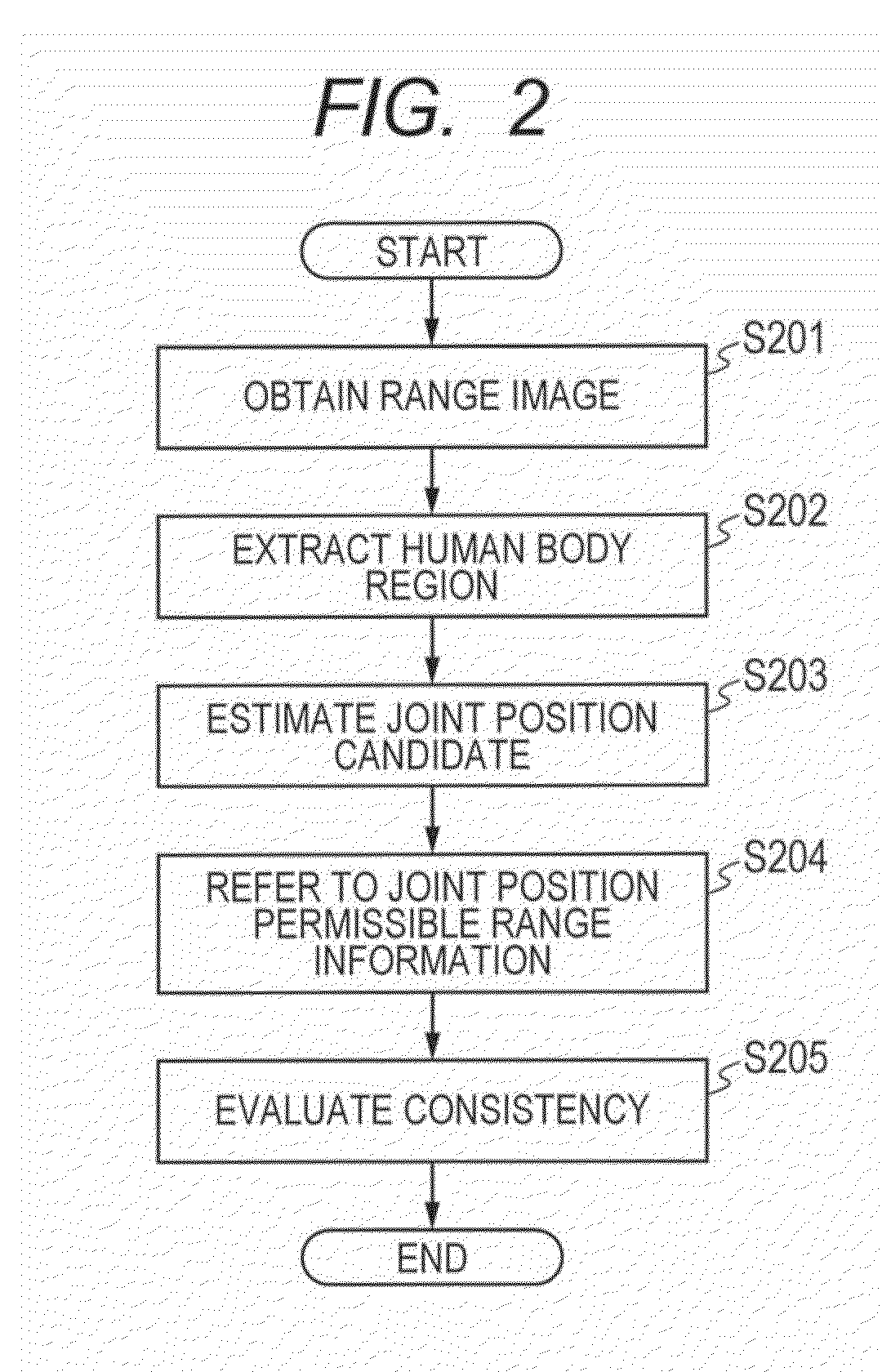

Posture estimating apparatus, posture estimating method and storing medium

The present invention aims to estimate a more consistent posture in regard to a multi-joint object. A target range image is first input, a human body region is extracted from the input range image, a target joint position candidate is calculated from the input range image, and a joint position is finally determined based on the calculated joint position candidate and a likelihood of each joint to estimate the posture. At this time, joint position permissible range information concerning inter-joint distance and angle of a human body model previously set by learning is obtained from a human body model storing unit, consistency is evaluated for a relation between the joint position candidates of a certain joint and other joint based on the obtained information, and thus the posture corresponding to the best combination of the joint positions is determined.

Owner:CANON KK

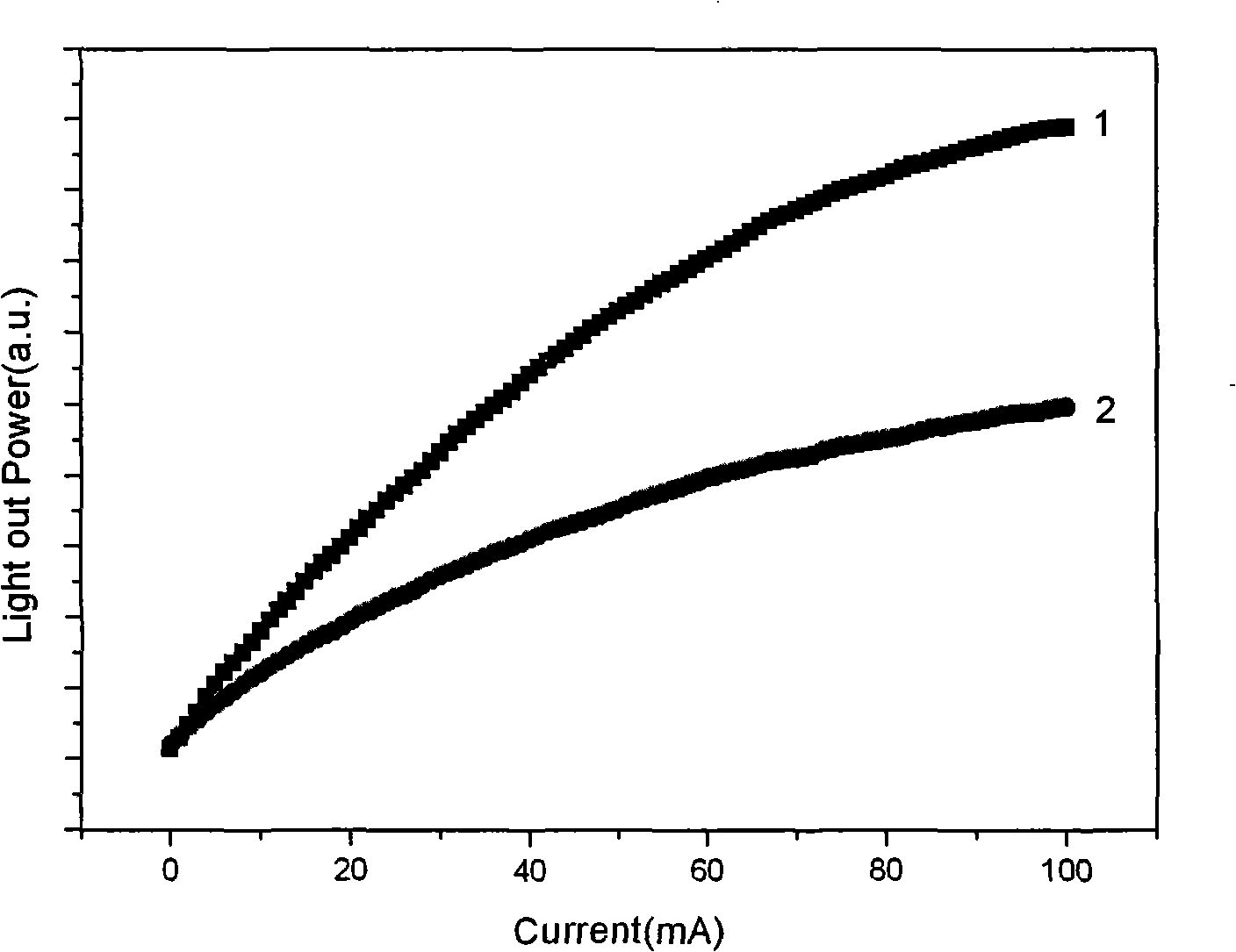

Manufacturing method of green light LED

ActiveCN101359710AReduce V-shaped defectsReduce precipitationSemiconductor devicesGreen-lightGreen led

The invention relates to a method for fabricating a green LED, which is mainly characterized in that through the introduction of an insert layer into an epitaxial growth InGaN / GaN quanta well, V type defects between the InGaN and the GaN is reduced and In precipitation is reduced; thus, the green LED with high brightness and strong antistatic ability can be obtained. With the introduction of the insert layer, the brightness of a 300micronx300micron green LED chip at 520nm under 20mA is improved from 100mcd to 250mcd and the antistatic ability of the chip is increased from HBM 500V (human-body model) to HBM 4000V.

Owner:EPILIGHT TECH +2

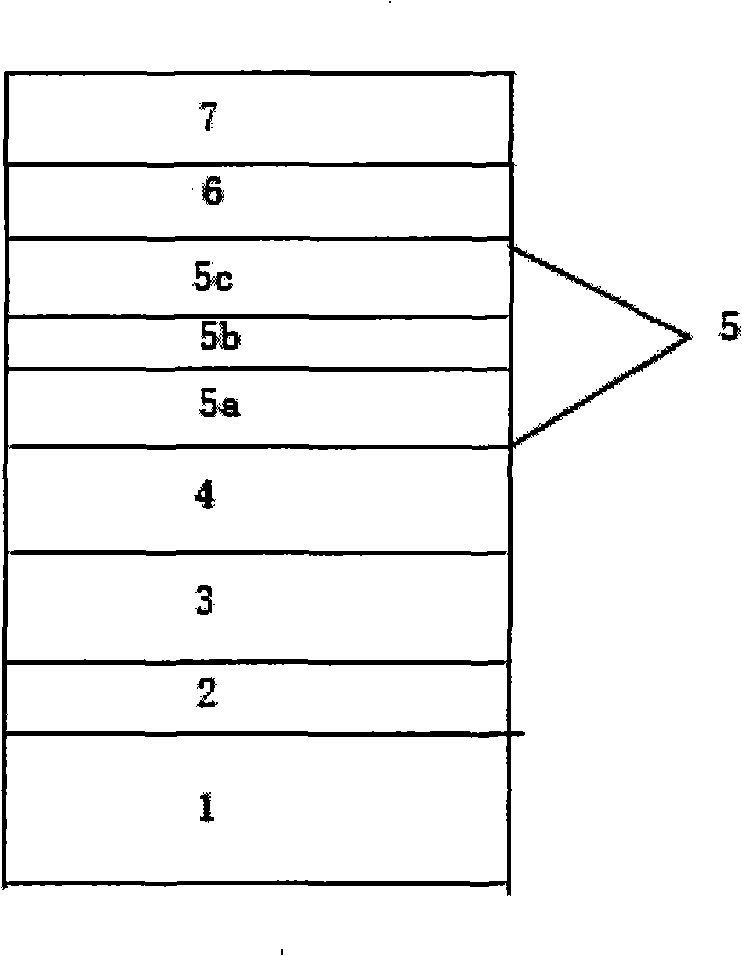

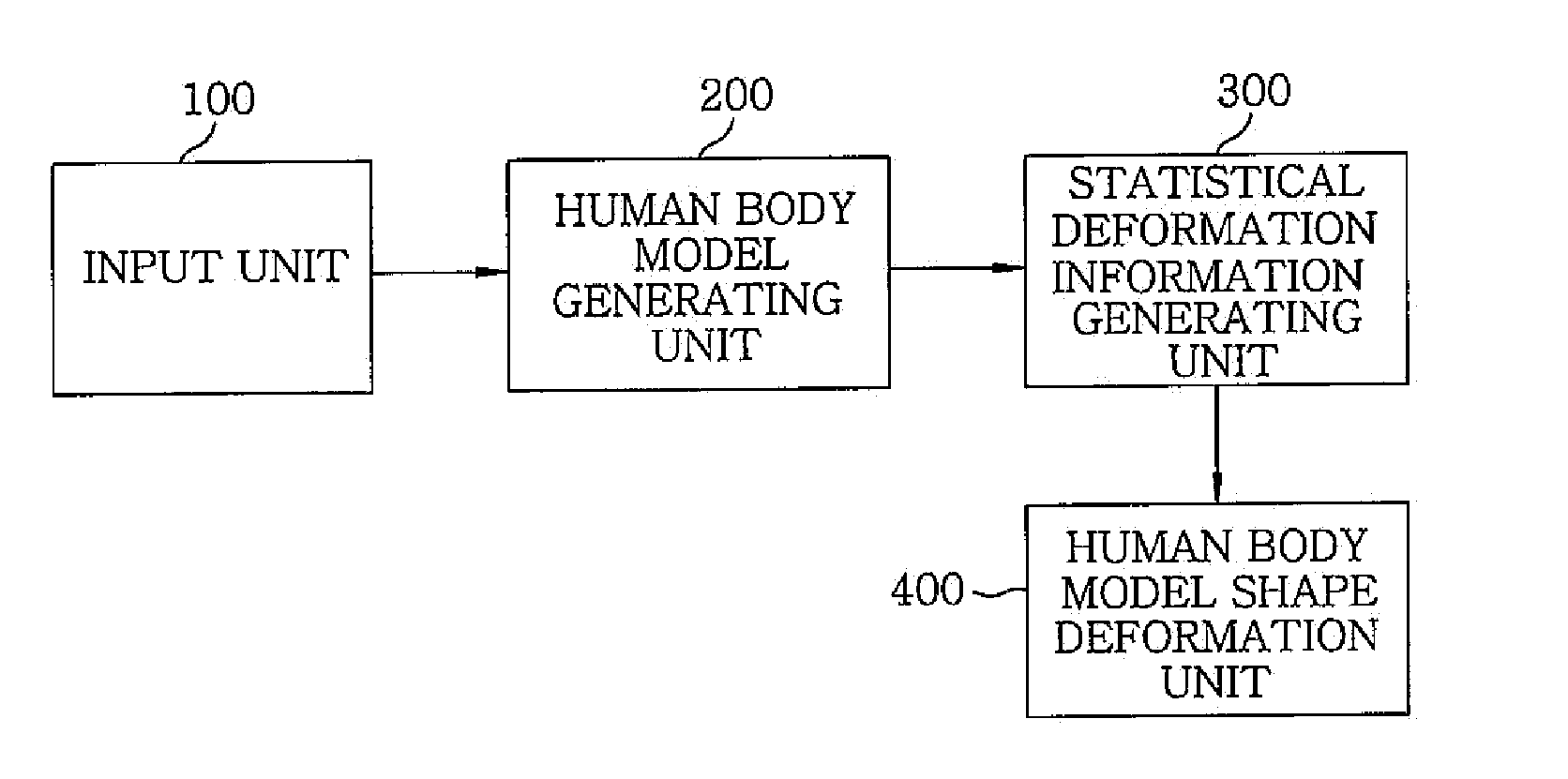

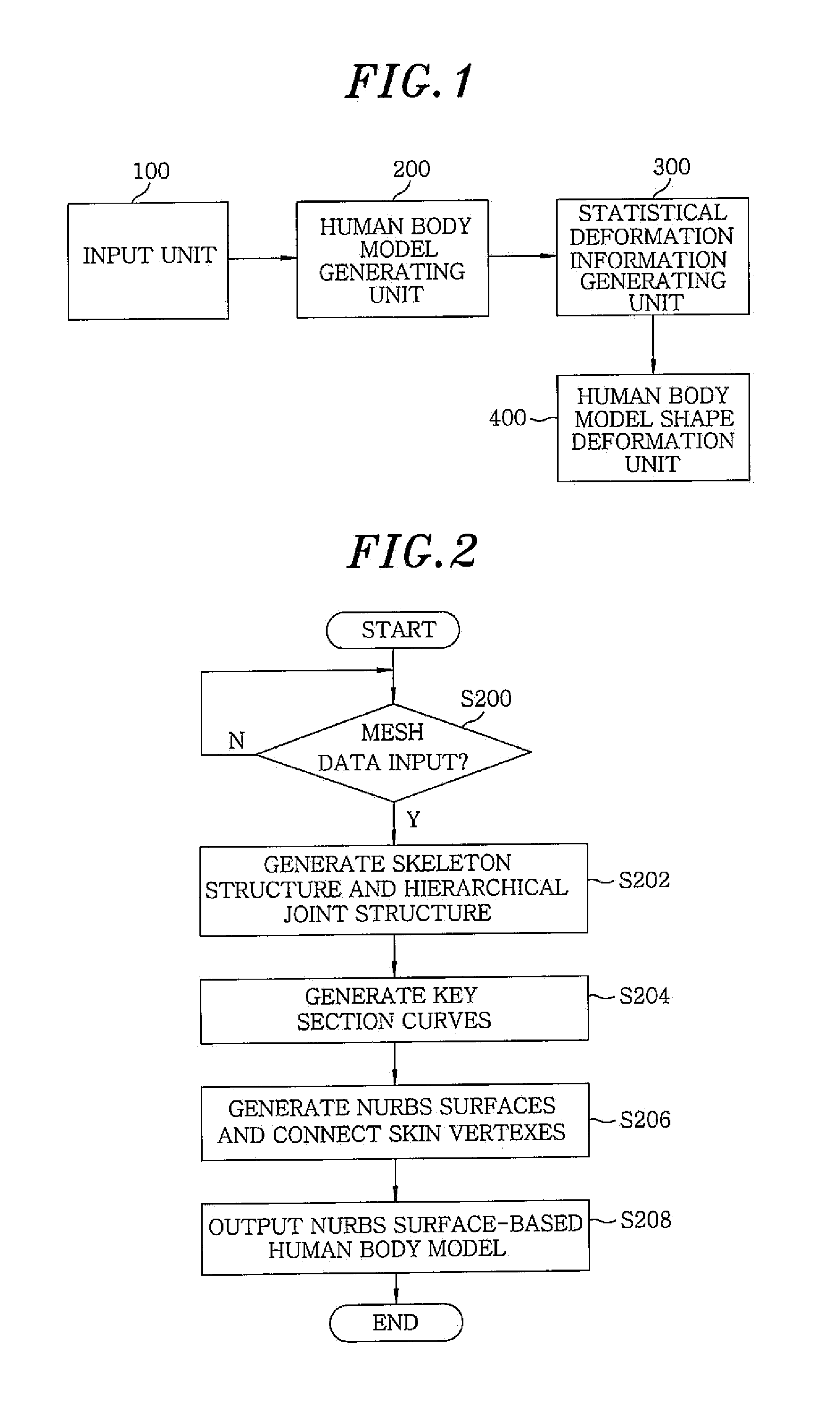

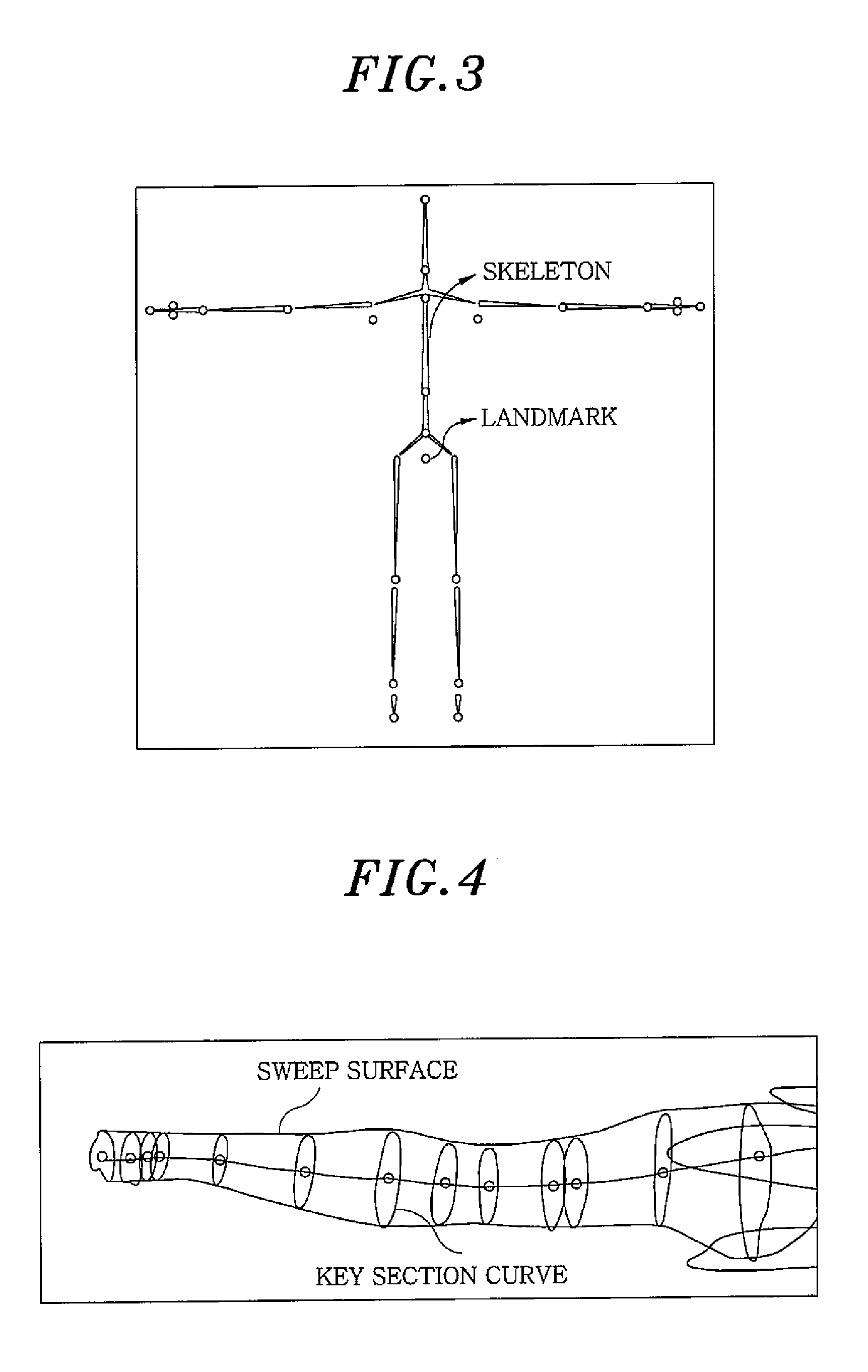

Method and apparatus for deforming shape of three dimensional human body model

A method of deforming a shape of a human body model includes the steps of reorganizing human body model data into a joint-skeleton structure-based Non-Uniform Rational B-spline (NURBS) surface model, generating statistical deformation information about control parameters of the NURBS surface model based on parameters of joints and key section curves for specific motions, and deforming the shape of the human body model based on the NURBS surface model and the statistical deformation information. The human body model data includes three-dimensional (3D) human body scan data and a 3D polygon mesh.

Owner:ELECTRONICS & TELECOMM RES INST

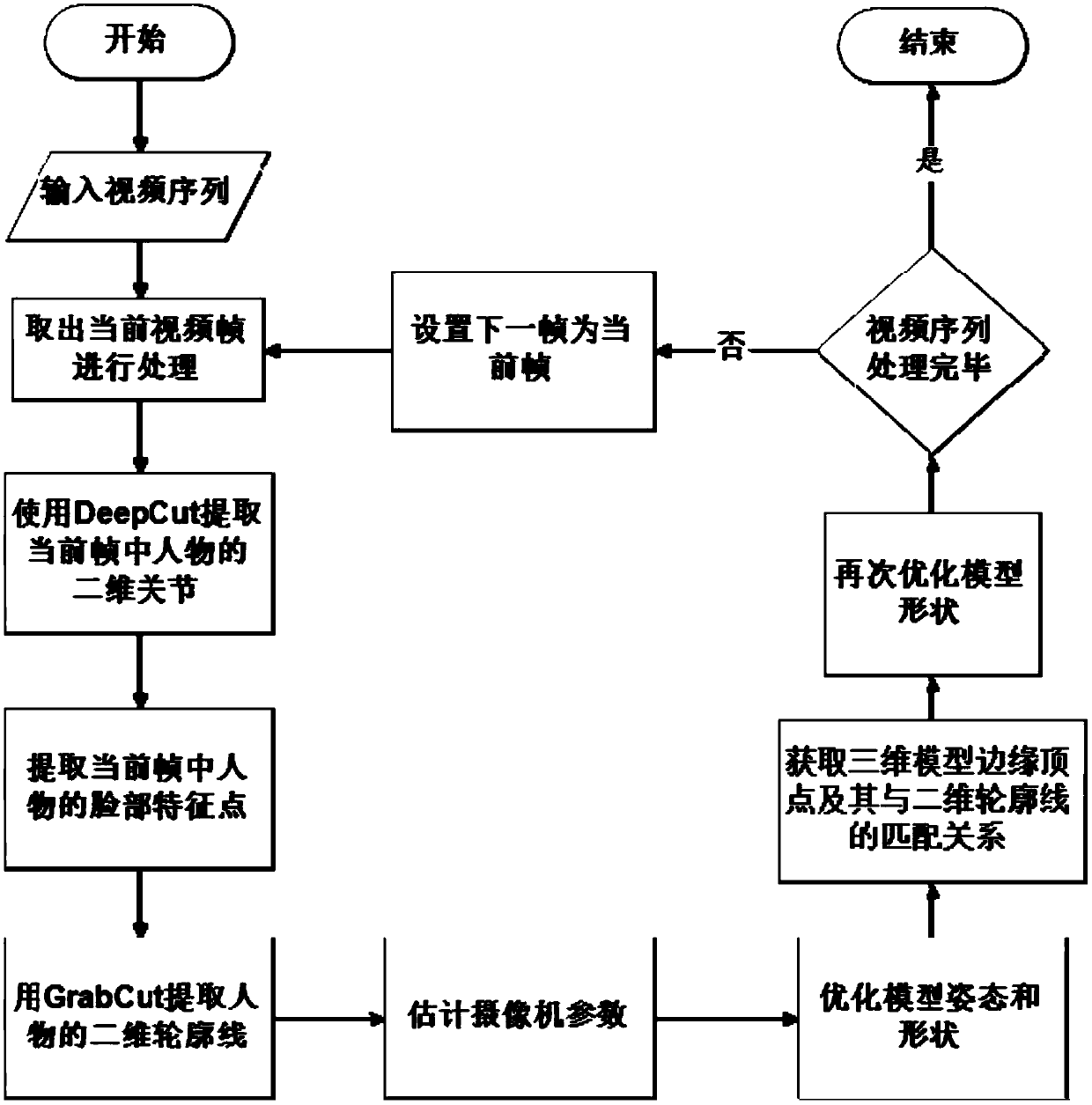

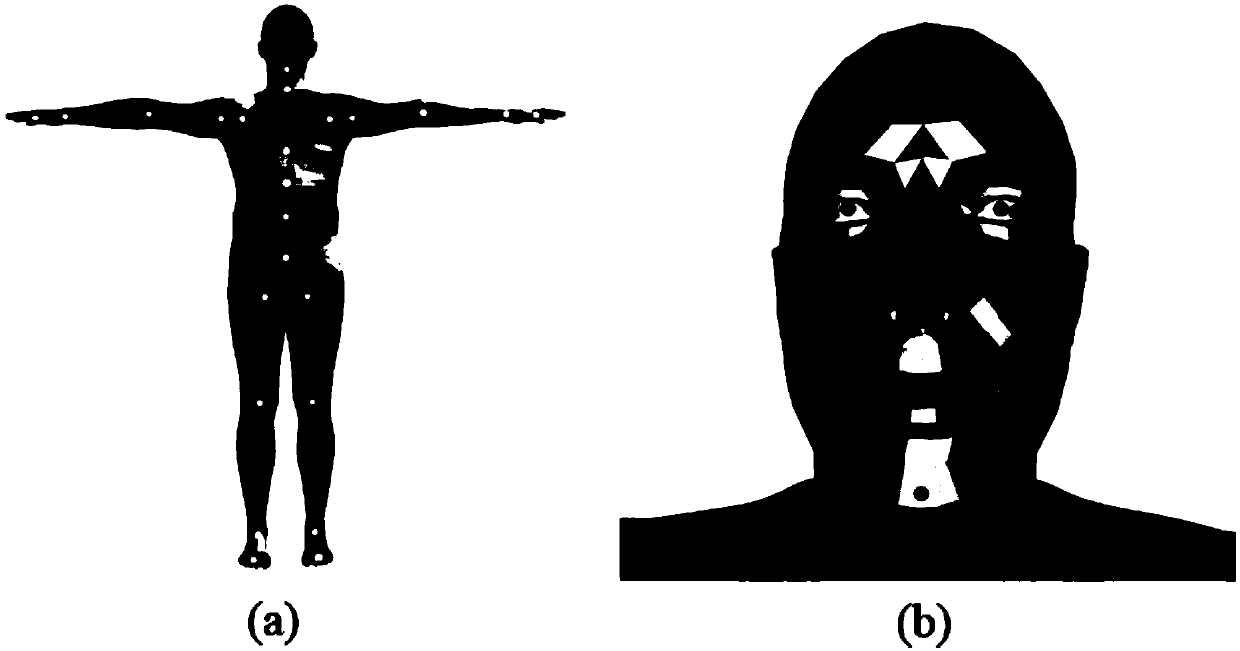

Three-dimensional human body model attitude and shape reconstruction method through video sequence

ActiveCN108629801AAvoid the problem of attitude flipImprove accuracyImage enhancementImage analysisPattern recognitionVideo sequence

The invention discloses a three-dimensional human body model attitude and shape reconstruction method through a video sequence, and the method comprises the steps: 1), extracting two-dimensional jointpoints of a person in a video frame; 2), extracting facial feature points of the person in the video frame; 3), extracting a two-dimensional contour line of the person in the video frame; 4), estimating camera parameters, and generating a perspective matrix according to the camera parameters; 5), carrying out the optimization of the model posture and shape through an optimization method; 6), obtaining the edge points of the 3D human body model at the camera angle and the matching relationship between the edge point and the 2D contour line; 7), carrying out the re-optimization of the shape ofthe model through the optimization method so that the sum of the differences between the distances from the positions of the edge points of the three-dimensional model at the camera angle after projection to the positions of the two-dimensional contour points in the video frame is minimized. The method can avoid the posture turnover in the reconstruction process, and also can accurately reconstruct the posture of a head under the condition that the overall similarity of the model is guaranteed.

Owner:SOUTH CHINA UNIV OF TECH

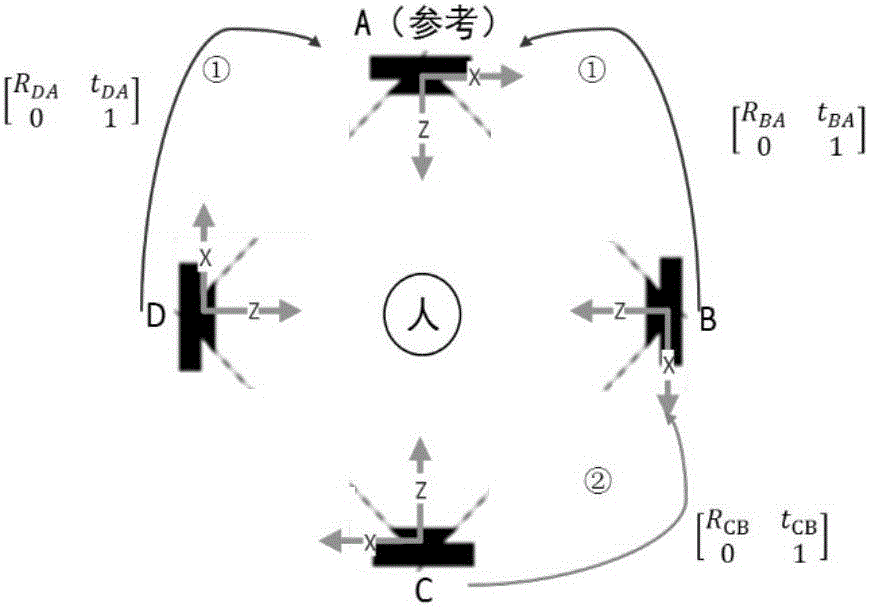

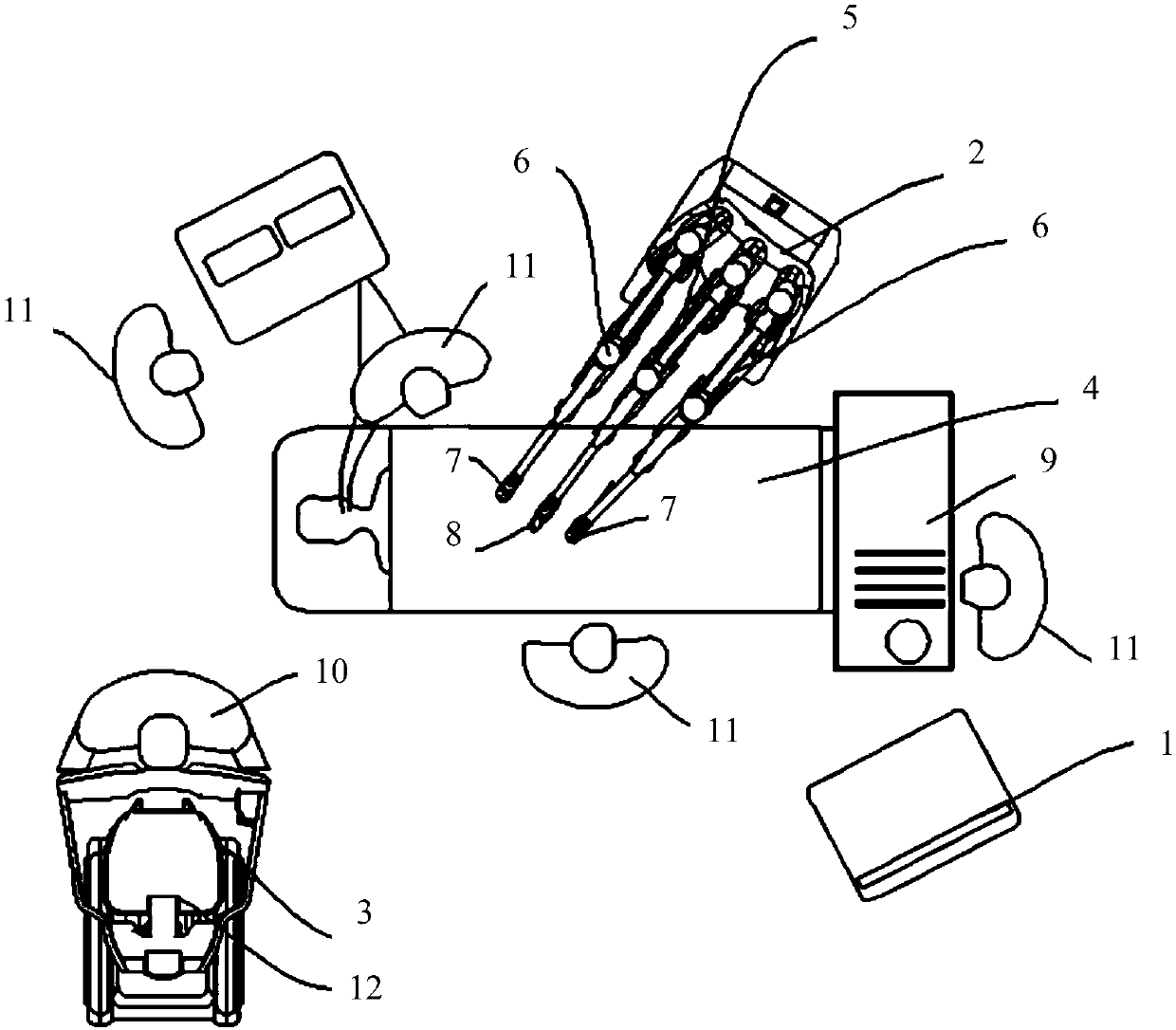

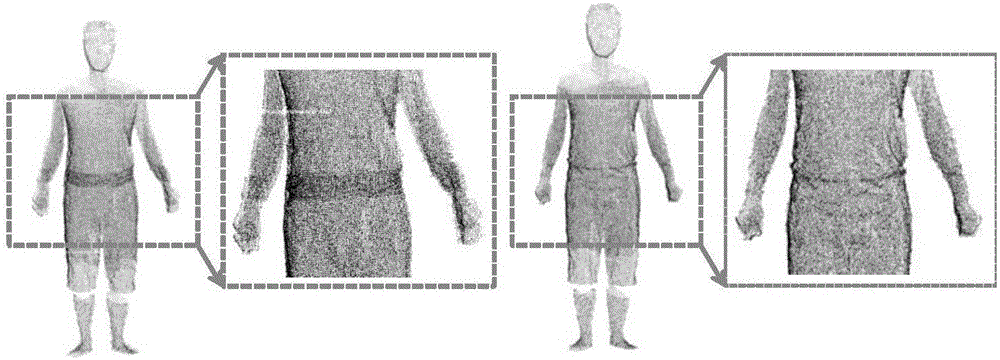

RGBD camera-based three-dimensional human body rapid modeling system

ActiveCN106709947AFast automatic calibrationImprove robustnessImage enhancementImage analysisColor mappingPoint cloud

The invention discloses an RGBD camera-based three-dimensional human body rapid modeling system. The system is executed through the following steps of: establishing a scanning array by utilizing a plurality of RGB-D cameras; calibrating the scanning array by using an automatic calibration technology, so as to obtain a calibrated matrix and automatically guide the calibrated matrix into a scanning system; enabling the RGB-D cameras in the array to independently scan a target object after the scanning is started, so as to obtain point cloud data of corresponding poses; processing the acquired point cloud data by utilizing a point cloud optimization technology, so as to obtain high-quality point clouds which can be used for triangular meshing; realizing reconstruction from the point clouds to a triangular patch model by utilizing a rapid triangular meshing algorithm; and obtaining a colored three-dimensional human body model by utilizing a color mapping technology. According to the system disclosed by the invention, a technology which is used for constructing the scanning matrix on the basis of the plurality of RGB-D cameras, rapidly acquiring human body feature data and realizing the construction of the human body three-dimensional model with high precision and refined color texture is provided.

Owner:XI AN JIAOTONG UNIV

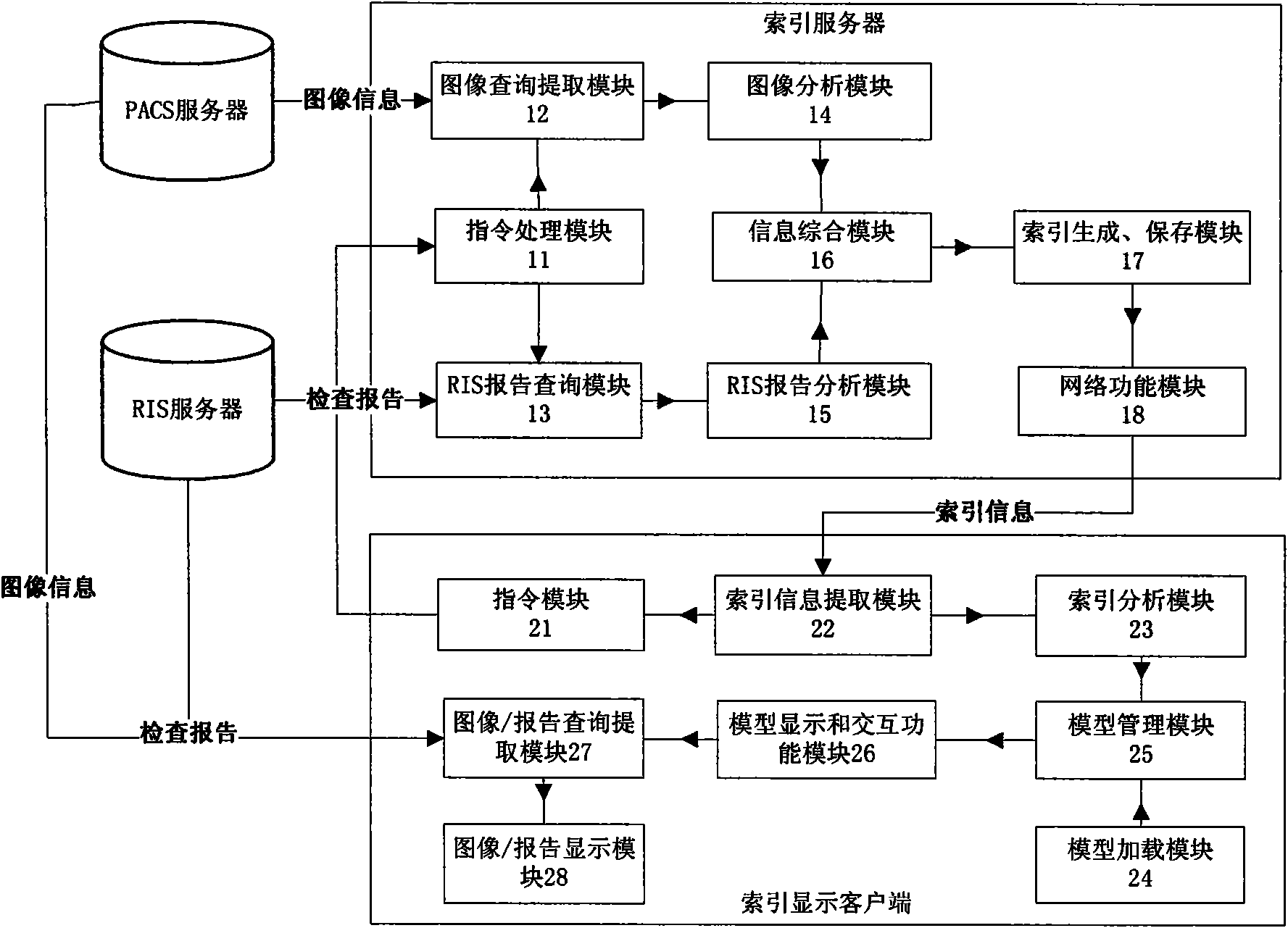

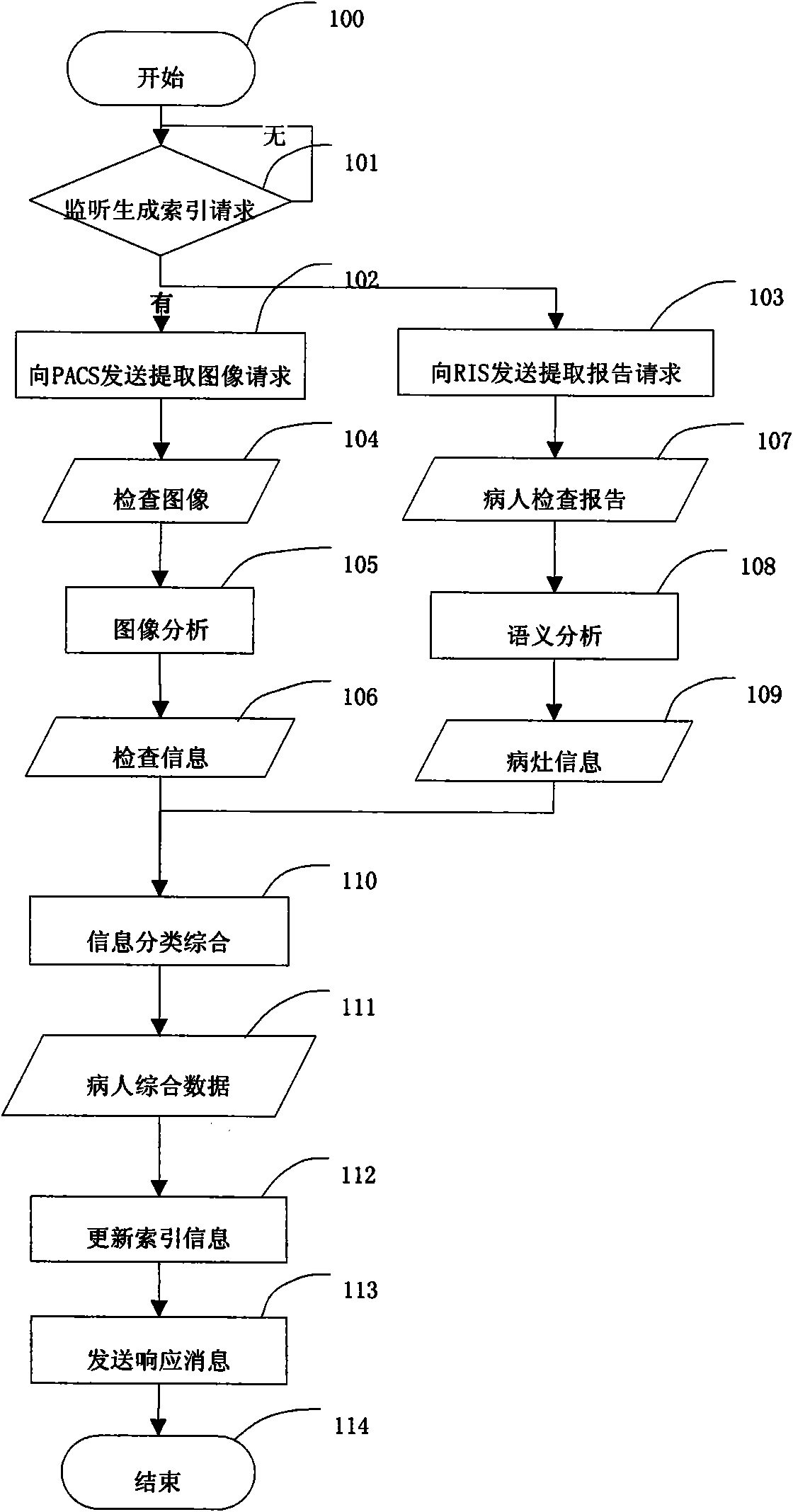

Visual indexing system for medical information system

InactiveCN102194059AImprove extractionRadiation diagnosis data transmissionImage analysisMedical recordIndexing Service

The invention discloses a visual indexing system for a medical information system. The system can be divided into an indexing server and an indexing display client, wherein the indexing server not only can inquire and extract patient medical information stored in each information system, but also can obtain the medical characteristic information of the medical information, such as negative and positive information and the like in focus diagnosis, by the artificial intelligent processing technology, and generate visual indexes of the medical information classified and stored by organs and parts according to the medical and focus information of patients. The indexing display client expresses and displays medical records and focus information stored in a patient indexing object by using a 3D (three-dimensional) human body model; and a doctor can make accurate judgment on the health conditions of each part of a patient body according to the information displayed by the human body model and quickly find out medical information with reference value for diagnosis by the human body model, thereby greatly increasing the speed of searching for the medical information of patients and knowing the health conditions of patients by doctors.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

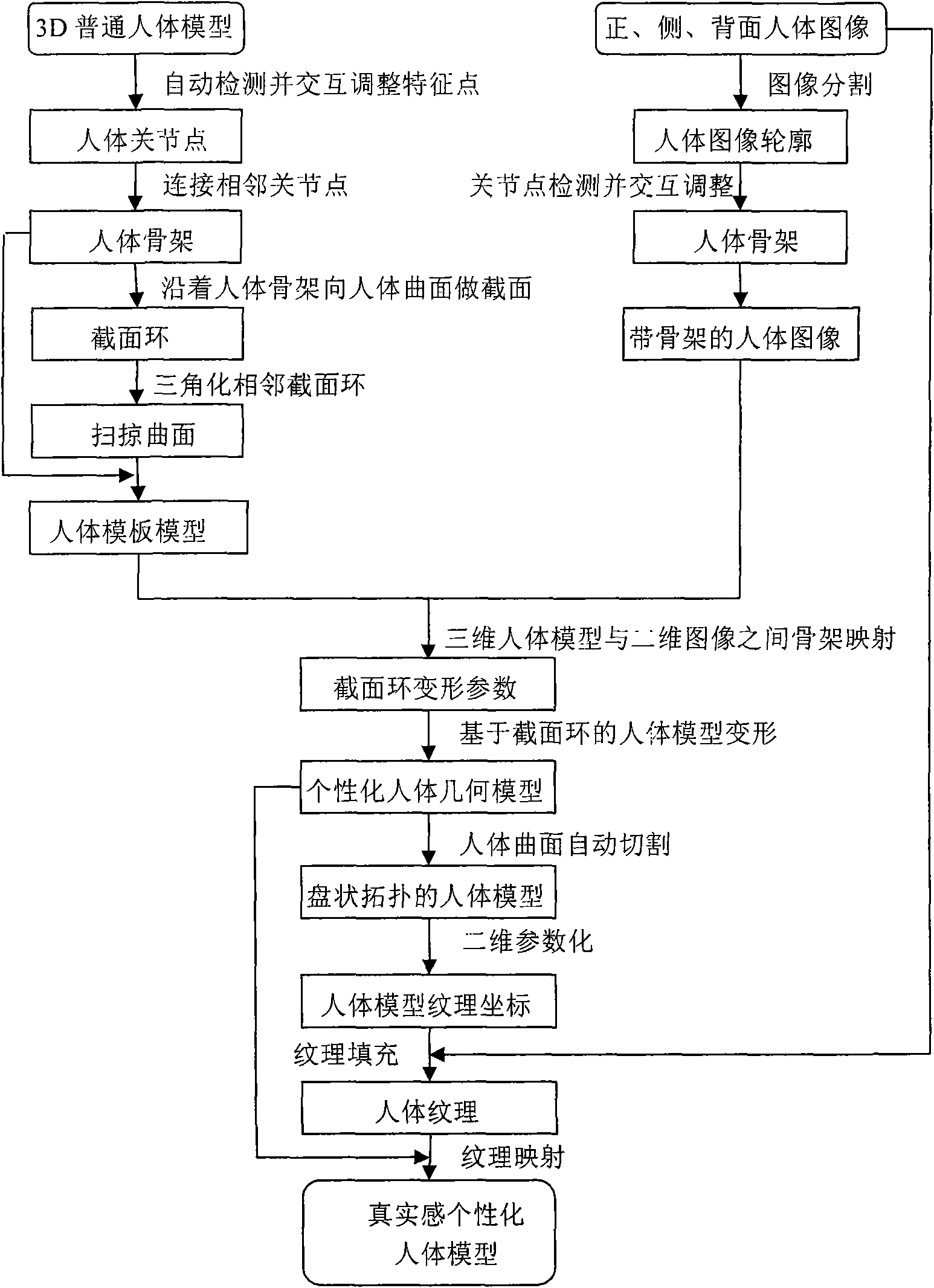

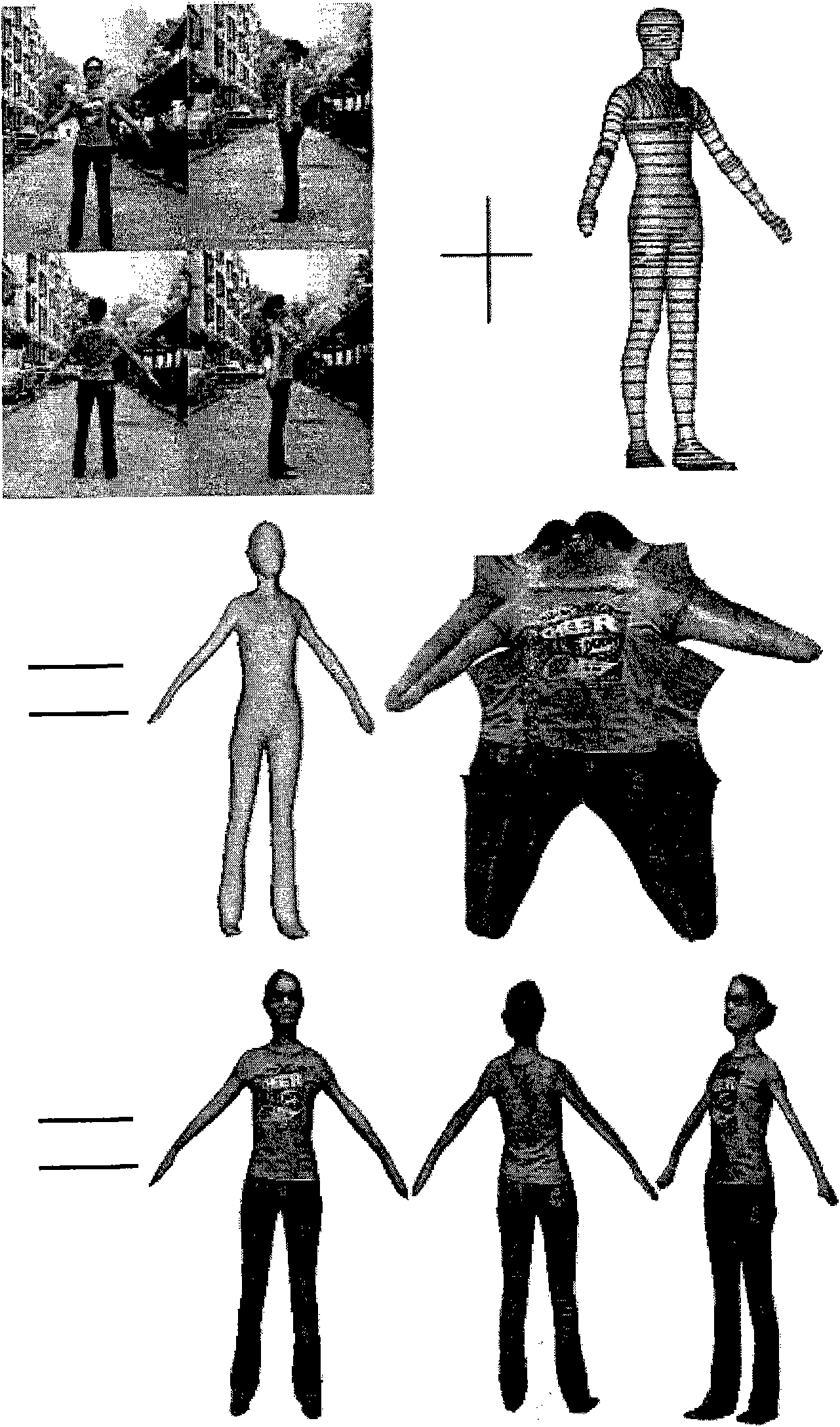

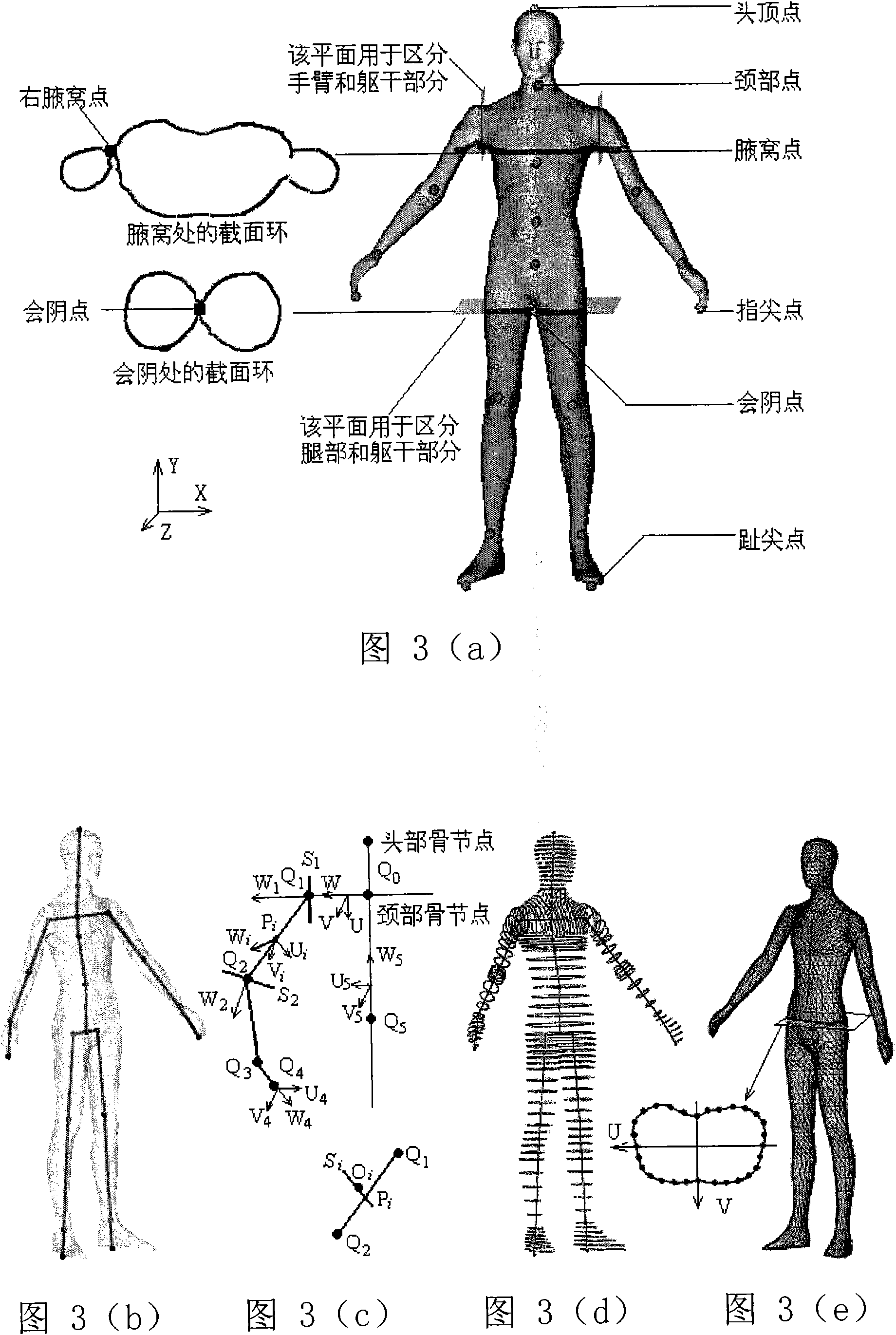

Individualized realistic virtual character modeling method based on images

The invention provides an individualized realistic virtual character modeling method based on images. Four human body images on the facade, lateral surfaces and back quickly generate an individualized three-dimensional human body model with realistic appearance. The method comprises the following steps: using a human body model based on a swept surface as a human body template model; extracting human body characteristic information from the images, establishing a corresponding relation between the human body template model and the human body images, and deforming the human body template model to generate an individualized human body geometric model; and on the two-dimensional parameterized results of the human body model, generating vivid human body textures by the human body images, and seamlessly mapping the human body textures to the three-dimensional individualized human body model to obtain the individualized human body model with realistic visual effect. The human body images are from a camera, a video camera and the like. The method provides a new low-cost and efficient human body modeling path for the field of virtual reality and digital entertainment.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

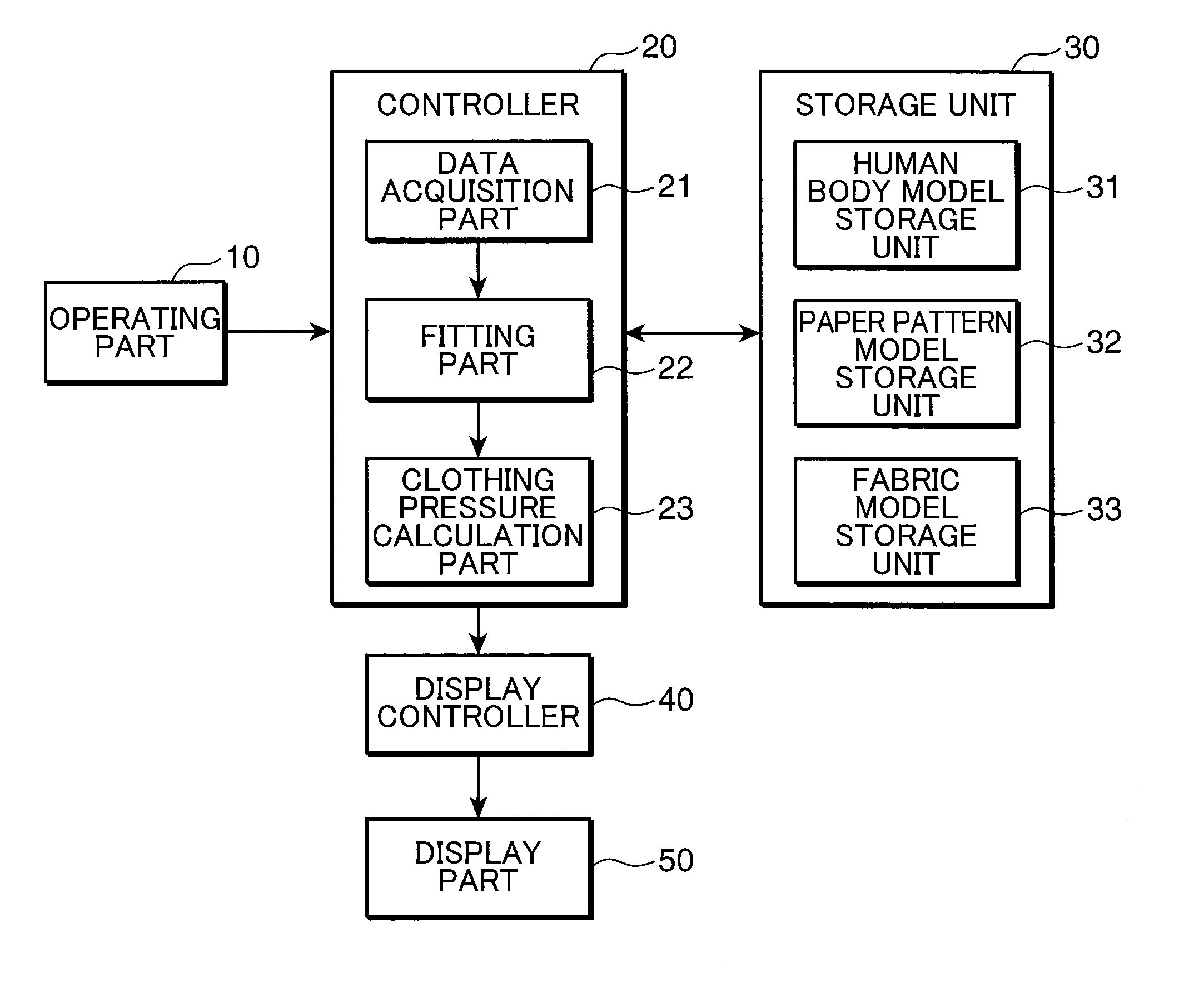

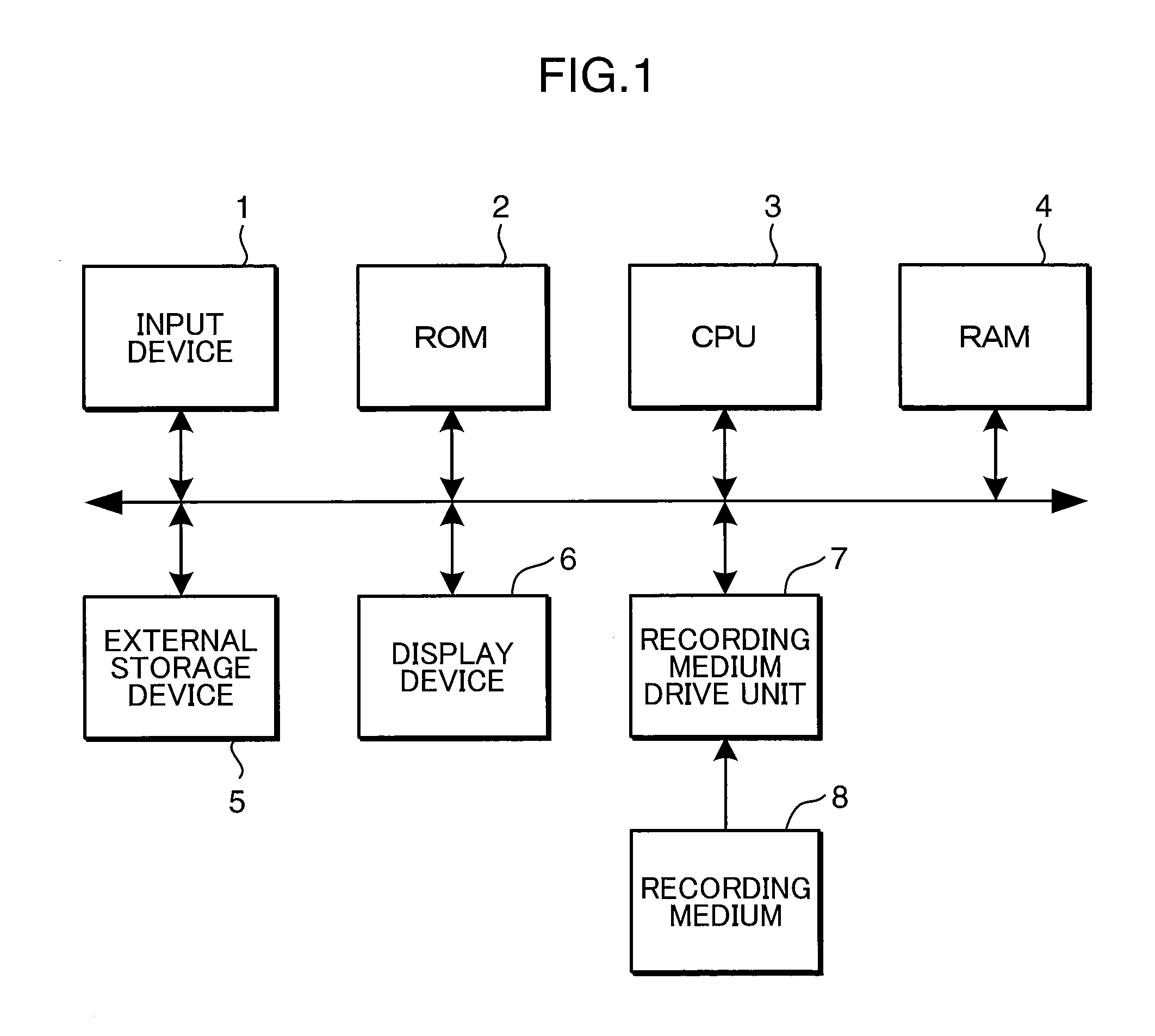

Clothing simulation apparatus, clothing simulation program, and clothing simulation method

InactiveUS20110022372A1Accurate acquisitionClothing pressureAnalogue computers for chemical processesDesign optimisation/simulationHuman bodyFinite element method

A clothing simulation apparatus precisely determines clothing pressure for bringing a clothing into tight contact with a human body. A fitting part 22 divides a paper pattern model into a plurality of elements, imparts dynamic characteristics shown by a fabric model to each element, deforms the paper pattern model by solving the motion equation of each element using a finite element method, and then fits the clothing virtually to a human body model. The fitting part 22 sets a temporary model to cover a predetermined section of the human body model, deforms the paper pattern model to bring the paper pattern model into contact with the temporary model, and thereafter deforms the paper pattern model to bring the paper pattern model into contact with the human body model.

Owner:TOYO TOYOBO CO LTD

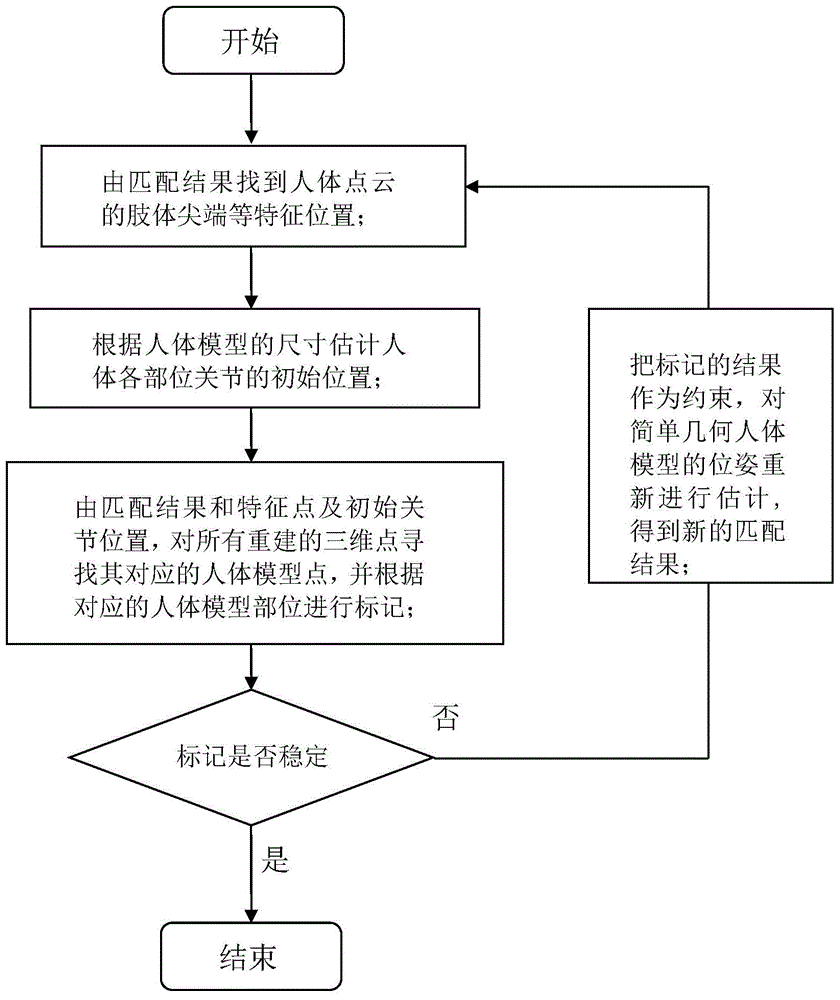

Method for three-dimensional human pose estimation

The invention discloses a method for three-dimensional human pose estimation, which can realize the real-time and high-precision 3D human pose estimation without high configuration hardware support and precise human body model. In this method for three-dimensional human pose estimation, including the following steps: (1) establishing a three-dimensional human body model matching the object, which is a cloud point human body model of visible spherical distribution constraint. (2) Matching and optimizing between human body model for human body pose tracking and depth point cloud. (3) Recovering for pose tracking error based on dynamic database retrieval.

Owner:BEIJING UNIV OF TECH

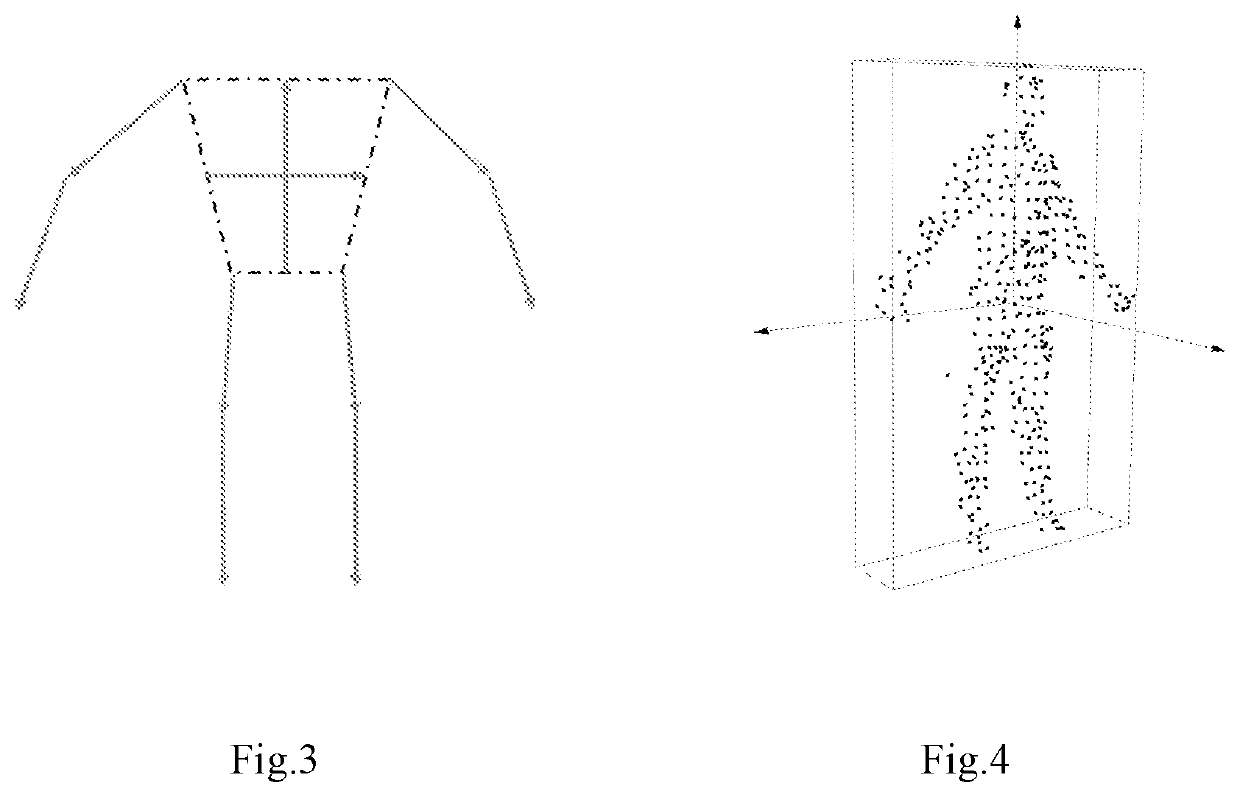

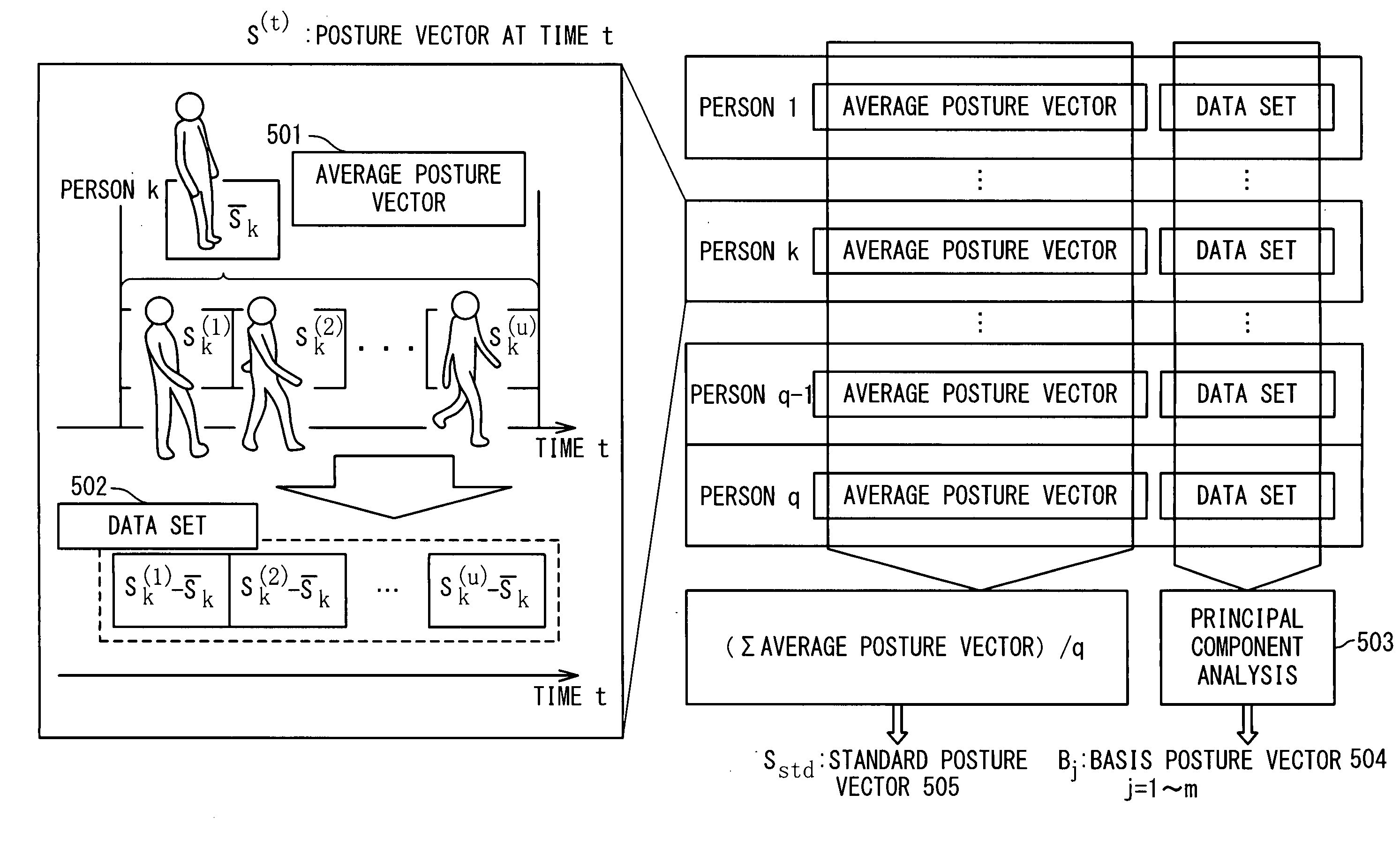

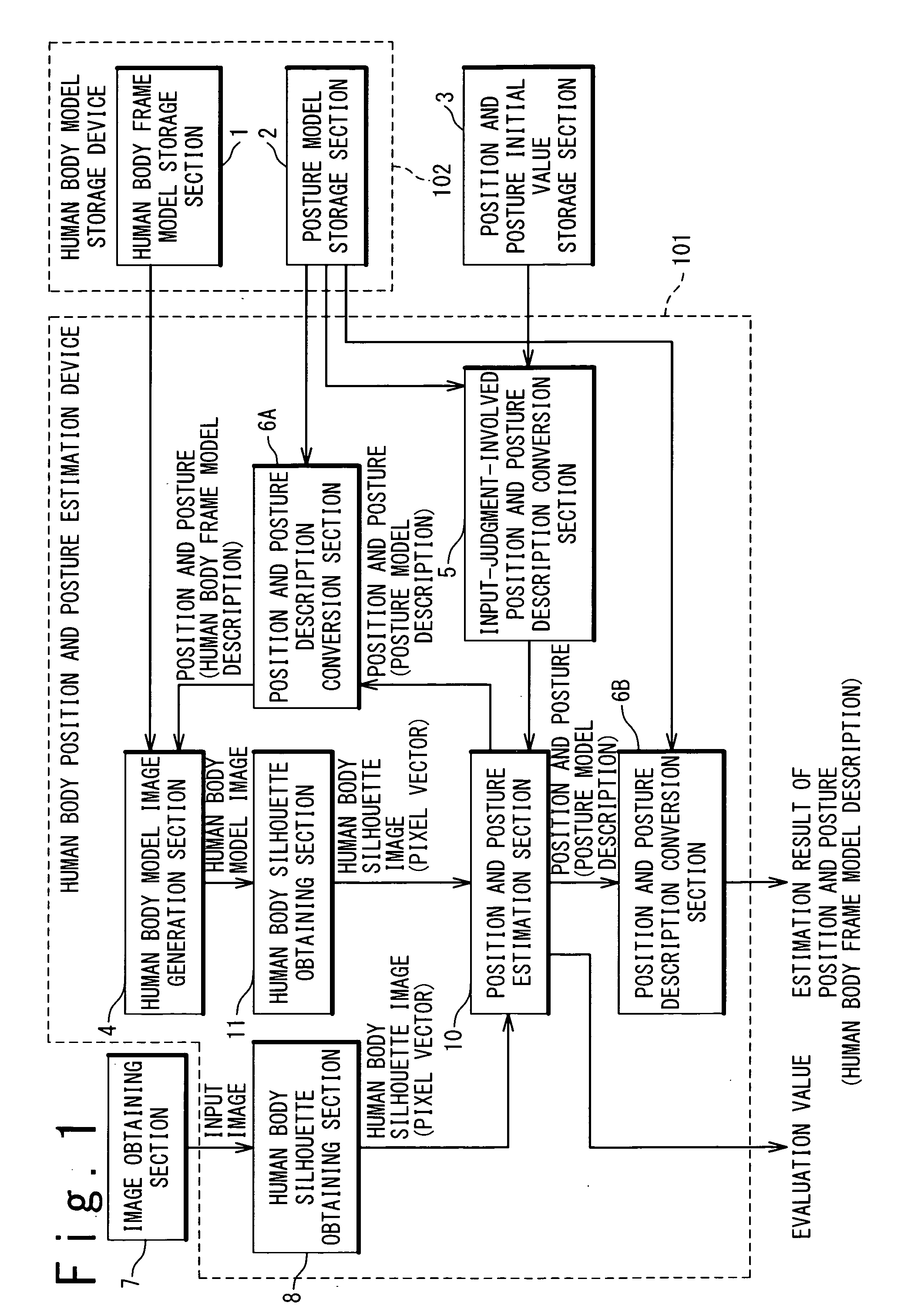

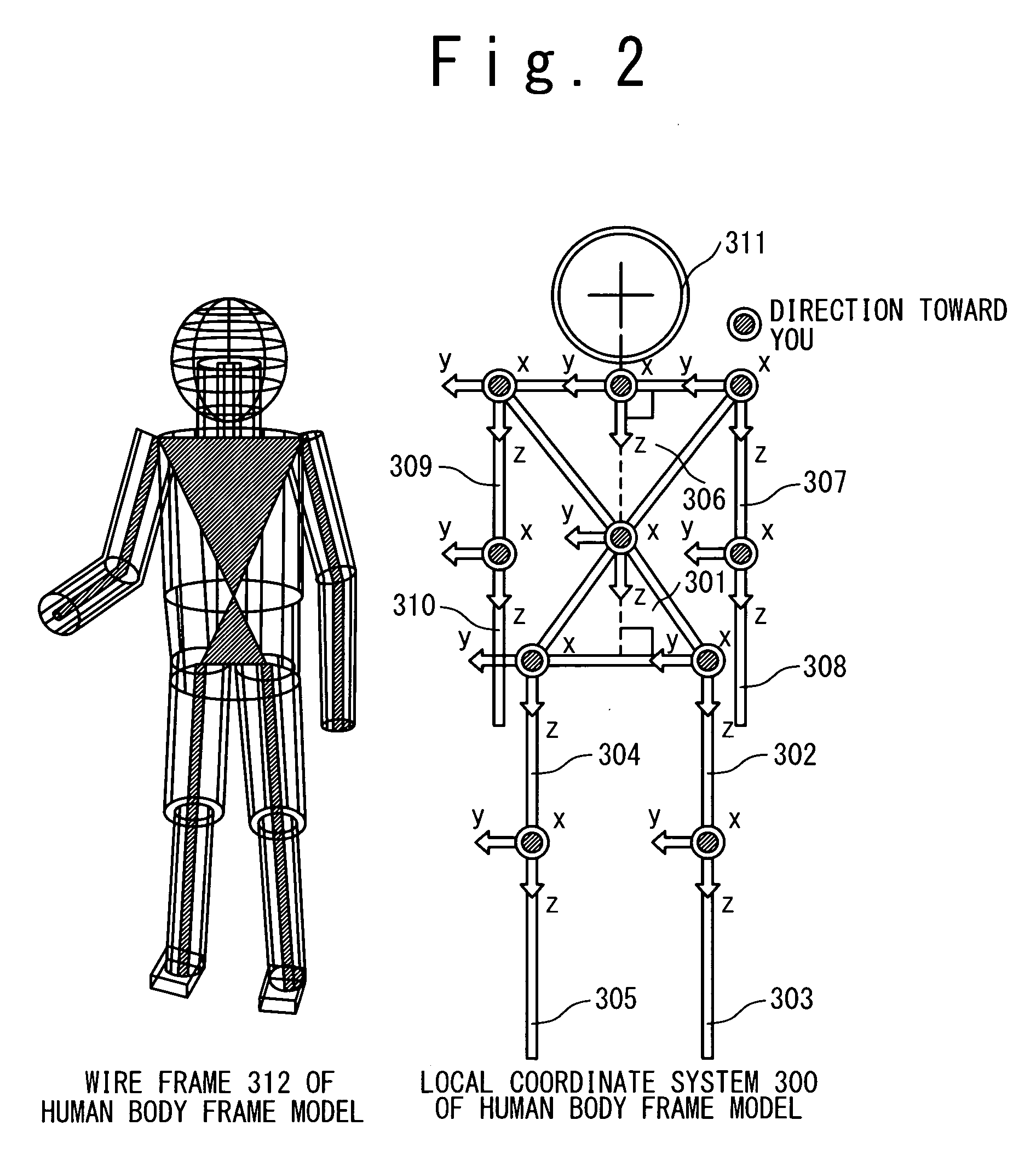

Articulated Object Position and Posture Estimation Device, Method and Program

ActiveUS20090080780A1Cost involvedEstimation speed can be improvedImage analysisCharacter and pattern recognitionHuman bodyPrincipal component analysis

An object is to provide an articulated object position and posture estimation device with reduced calculation cost of model fitting for estimating position and posture and with improved estimation speed. A posture model storage section 2 stores data concerning to a posture model with low-dimensional parameters under movement restraint. The low-dimensional parameters are obtained by performing a principal component analysis on time-series postures of an articulated object frame model corresponding to a predetermined limited movement of an articulated object such as human body. A human body position and posture estimation device 101 generates a image of each posture of the articulated object frame model within postures which can be taken by the posture model in a human body model image generating section 4, performs a matching with an estimation target articulated object image in a position and posture estimation section 10, and thus, estimates a posture.

Owner:NEC CORP

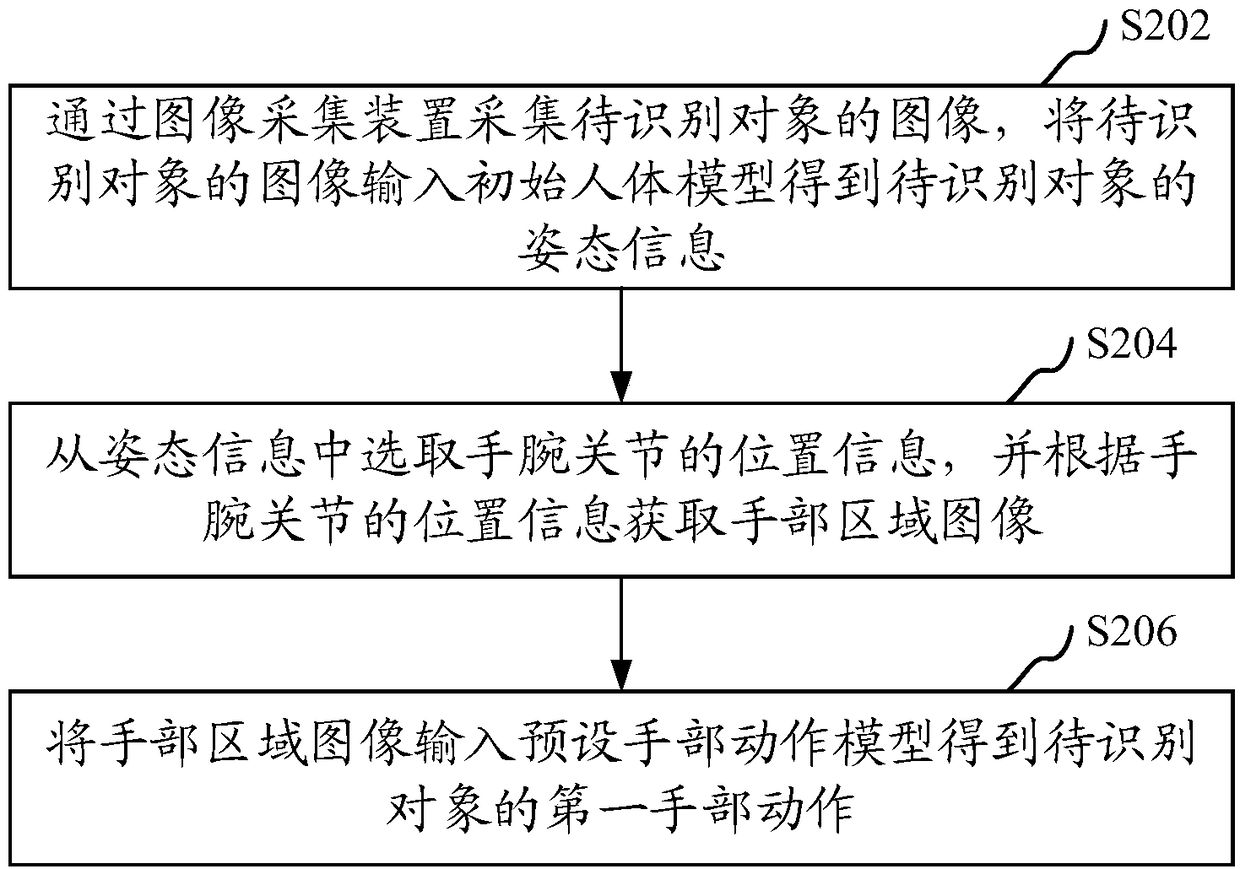

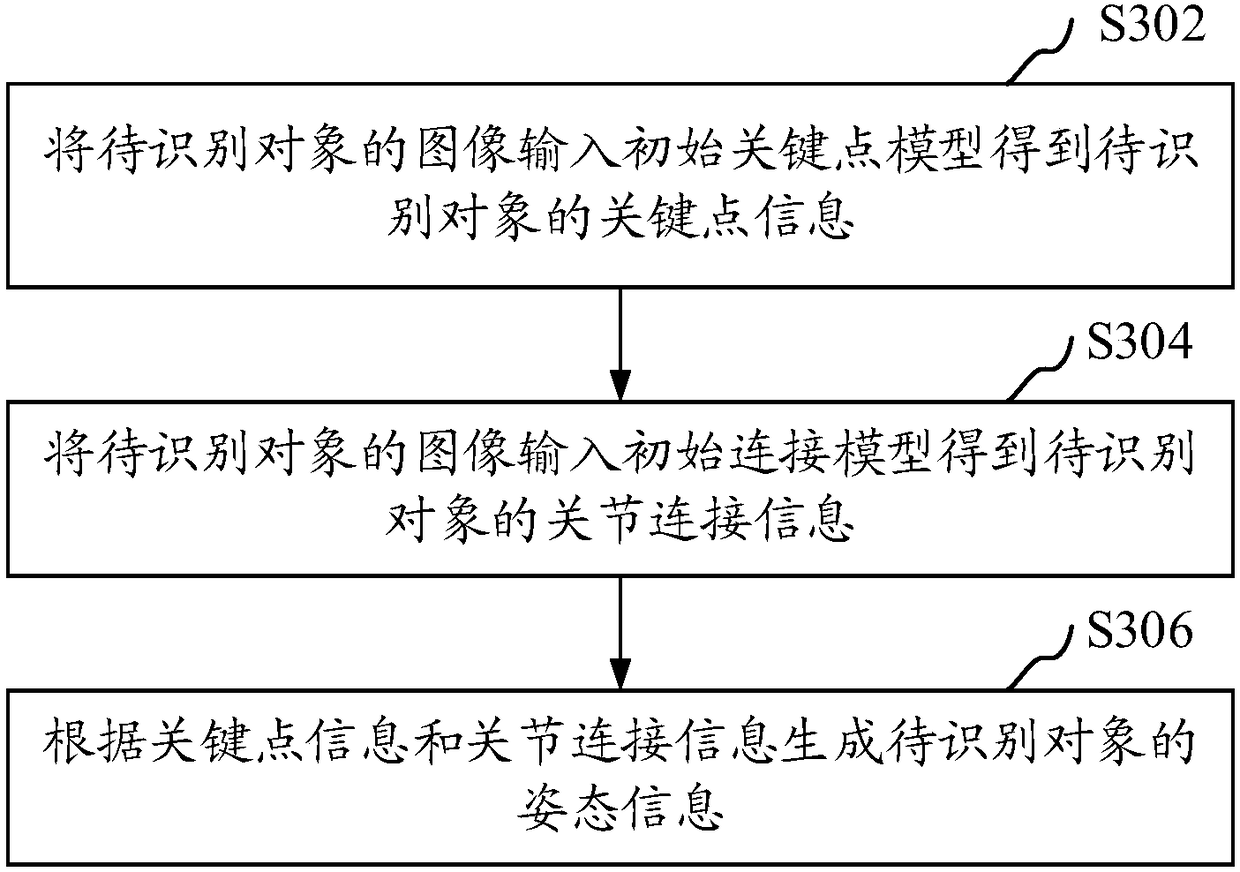

Hand action identification method and apparatus, computer device and readable storage medium

InactiveCN108399367AImprove accuracyInput/output for user-computer interactionCharacter and pattern recognitionPattern recognitionHand parts

The invention relates to a hand action identification method and apparatus, a computer device and a readable storage medium. The hand action identification method comprises the following steps of collecting an image of a to-be-identified object through an image collection apparatus, and inputting the image of the to-be-identified object to an initial human body model to obtain pose information ofthe to-be-identified object; selecting position information of wrist joints from the pose information, and according to the position information of the wrist joints, obtaining a hand region image; andinputting the hand region image to a preset hand action model to obtain a first hand action of the to-be-identified object. According to the method, an overall pose of an identified person is identified firstly and then a hand is located; and when multiple to-be-identified objects exist in an identification region and are mutually shielded, the hand positions can be judged according to the posesof the to-be-identified objects, so that the hand action identification accuracy is improved.

Owner:深圳市阿西莫夫科技有限公司

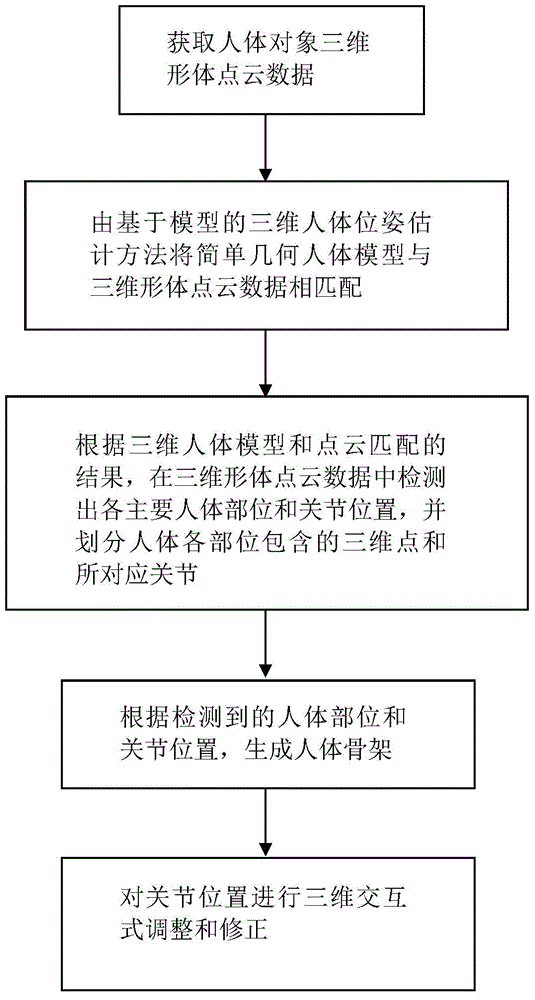

Method for creating object-oriented customized three-dimensional human body model

The invention discloses a method for creating an object-oriented customized three-dimensional human body model. The method comprises the following steps: acquiring images of a human body object at the same moment at different angles by a plurality of synchronization cameras and rebuilding a three-dimensional feature point cloud of a human body from the images by adopting a three-dimensional rebuilding method; matching a simple three-dimensional human body model onto the three-dimensional feature point cloud by adopting a pose estimation method on the basis of a model; according to a matching result of the three-dimensional human body model and the point cloud, detecting all main human body positions and joint positions and dividing the human body to form all of the part; according to the detected human body positions and joint positions, generating a human body skeleton for driving the human body model; regulating and amending the joint positions. The method for creating the object-oriented customized three-dimensional human body model, disclosed by the invention, solves the problems of shortage of matching degree and adaptability of an existing three-dimensional human body model on the specific human body object and can create the three-dimensional human body model completely coincided with the feature dimension of the human body object.

Owner:NAT UNIV OF DEFENSE TECH

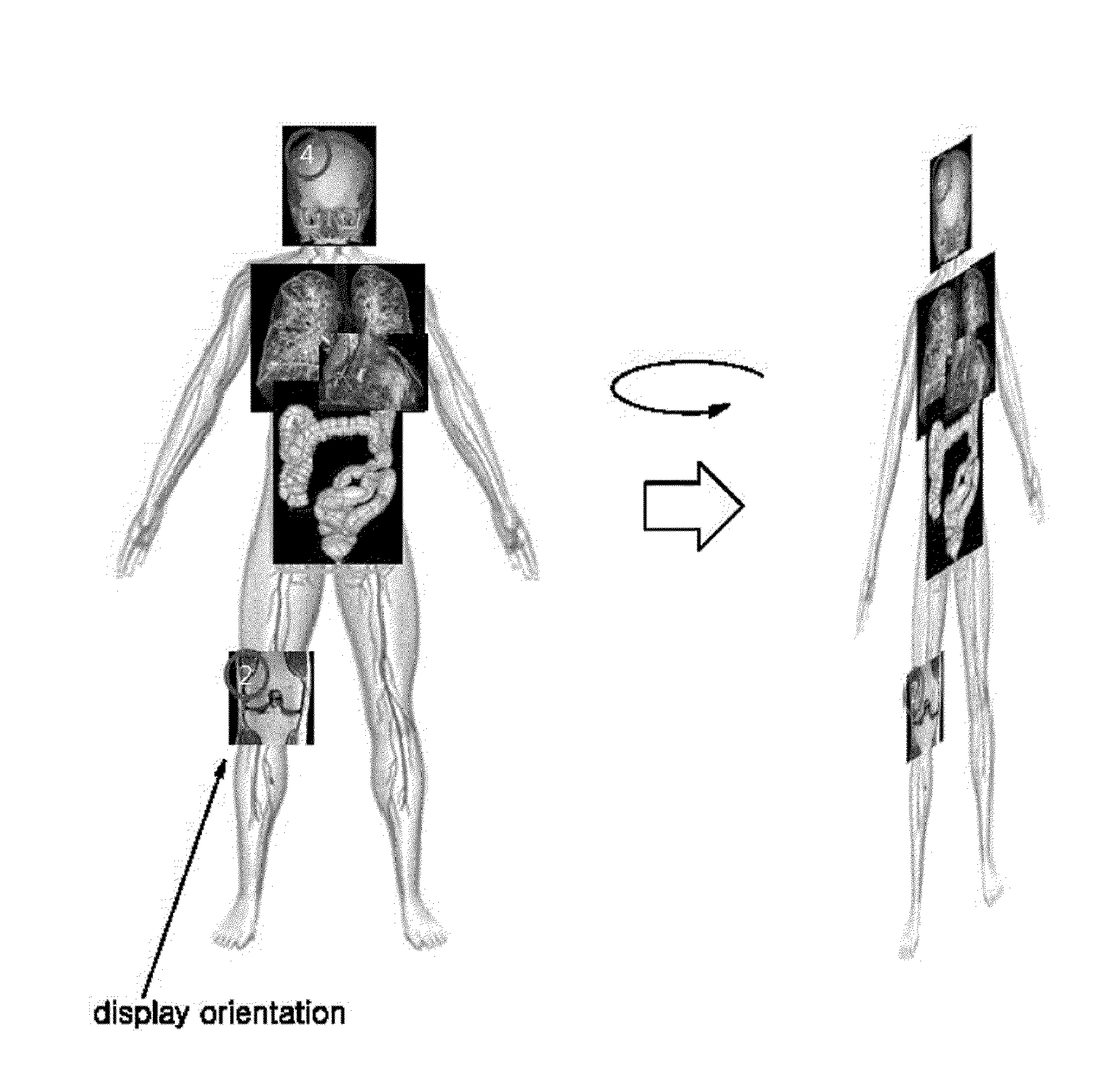

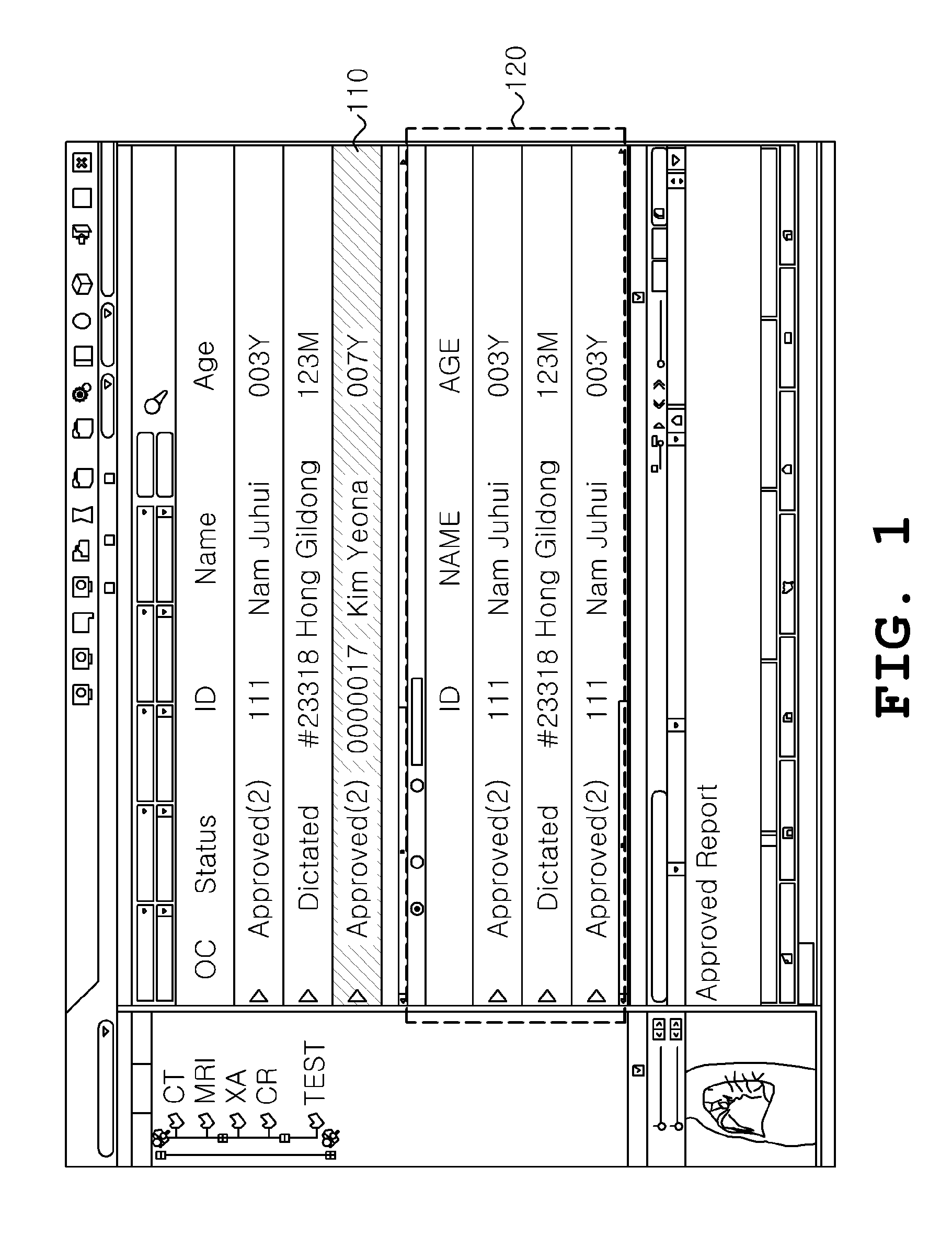

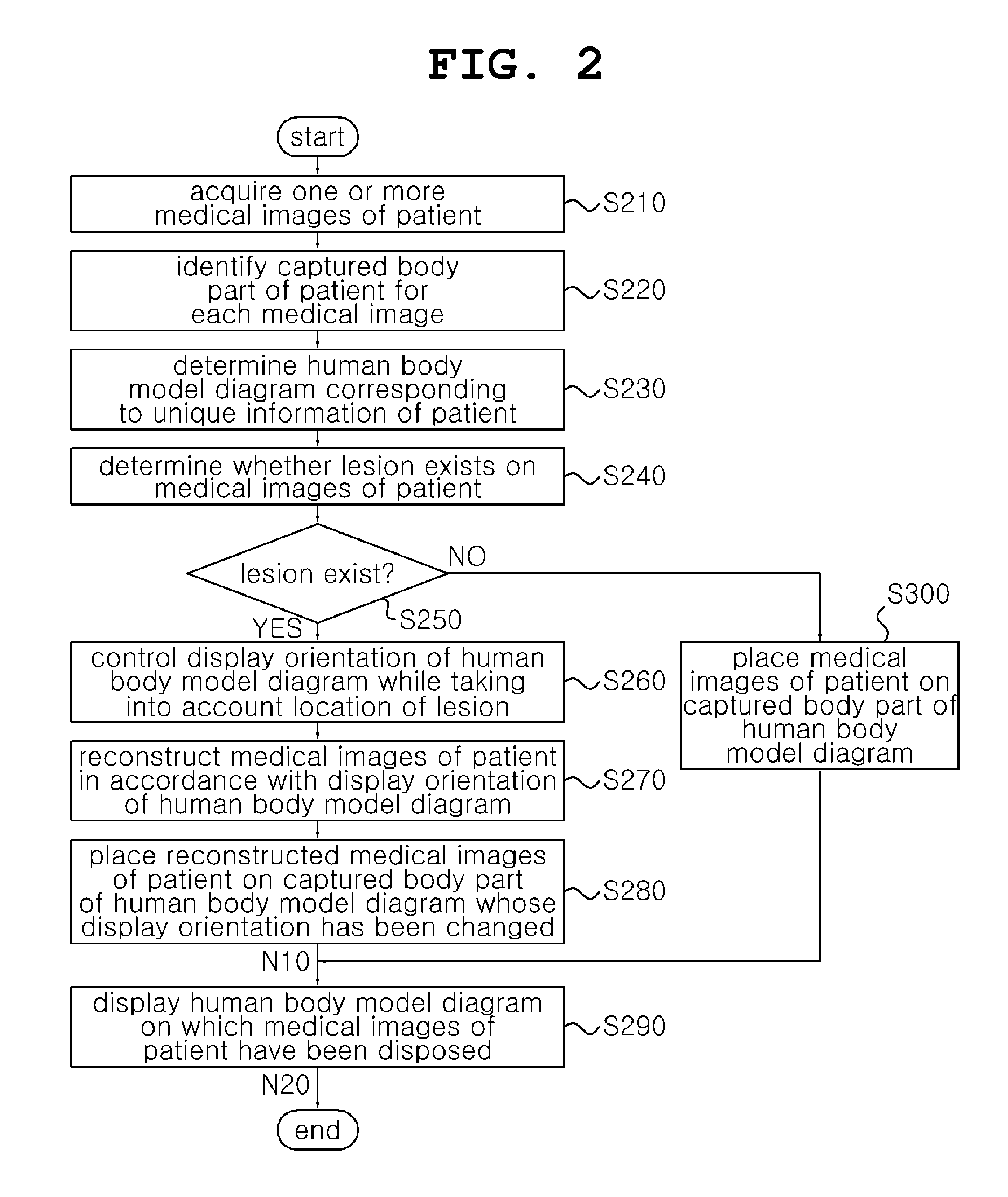

Medical image display method using virtual patient model and apparatus thereof

InactiveUS20140104311A1Clear visionSure easyCathode-ray tube indicatorsComputerised tomographsComputer scienceHuman-body model

Disclosed herein are a method and apparatus for displaying medical images using a virtual patient model. The apparatus includes a processor, the processor includes an image acquisition unit, a captured body part determination unit, a determination unit, and a display (control) unit. The image acquisition unit acquires one or more medical images of a patient. The captured body part determination unit determines the captured body part of each of the acquired one or more medical images. The determination unit determines a human body model diagram corresponding to unique information of the patient among a plurality of predetermined human body model diagrams. The display unit places and displays the one or more medical images on the determined captured body parts of the determined human body model diagram.

Owner:INFINITT HEALTHCARE CO LTD

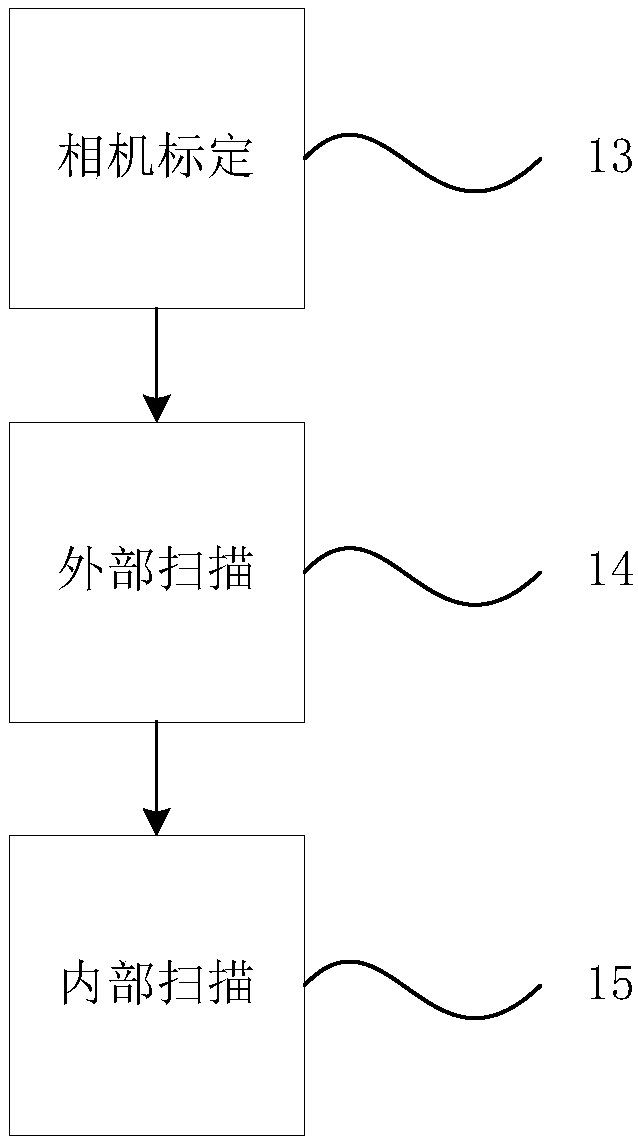

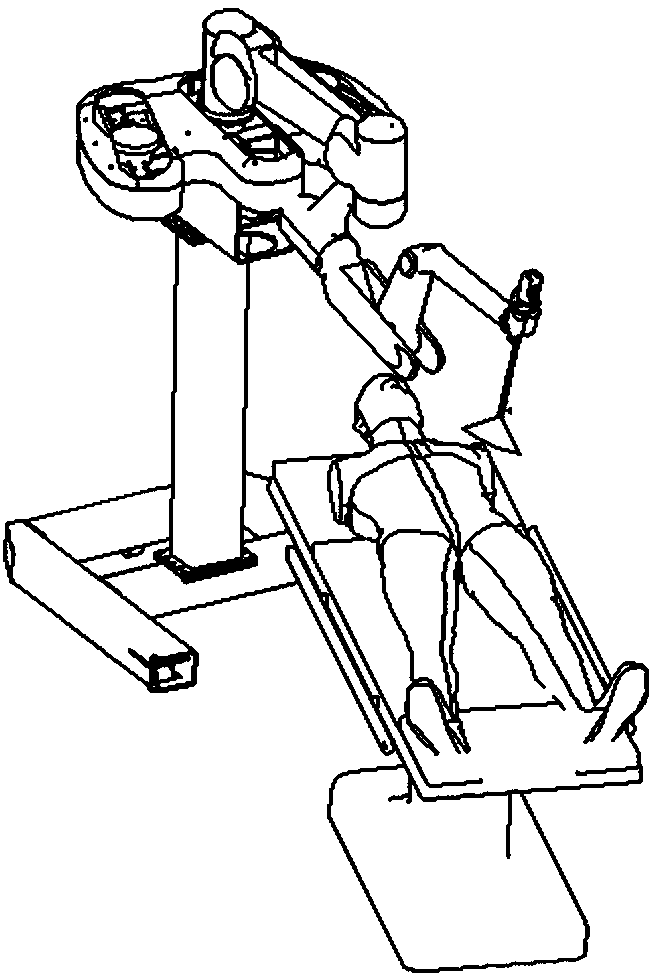

Surgical assistant locating system

The invention provides a surgical assistant locating system. The surgical assistant locating system is used for assisting a doctor in locating the position of a wound. The surgical assistant locatingsystem comprises a robot patient end, and the robot patient end comprises an instrument arm which is used for being detachably connected with a surgical instrument, and an endoscope arm which is usedfor being detachably connected with an endoscope. In the surgical assistant locating system, a scanning module is used for obtaining in-vivo and body-surface three-dimensional data of a patient, a modeling module is used for building a human body model according to the in-vivo and body-surface three-dimensional data obtained by the scanning module, and building position and pose descriptions of the human body model under the coordinate system of the robot patient end, and a locating module is used for locating the recommended position of the wound according to the human body, the moving spaceof the instrument arm in the human body model, the moving space of the endoscope arm in the human body model and the interference between the instrument arm and the endoscope arm in the human body model.

Owner:SHANGHAI MICROPORT MEDBOT (GRP) CO LTD

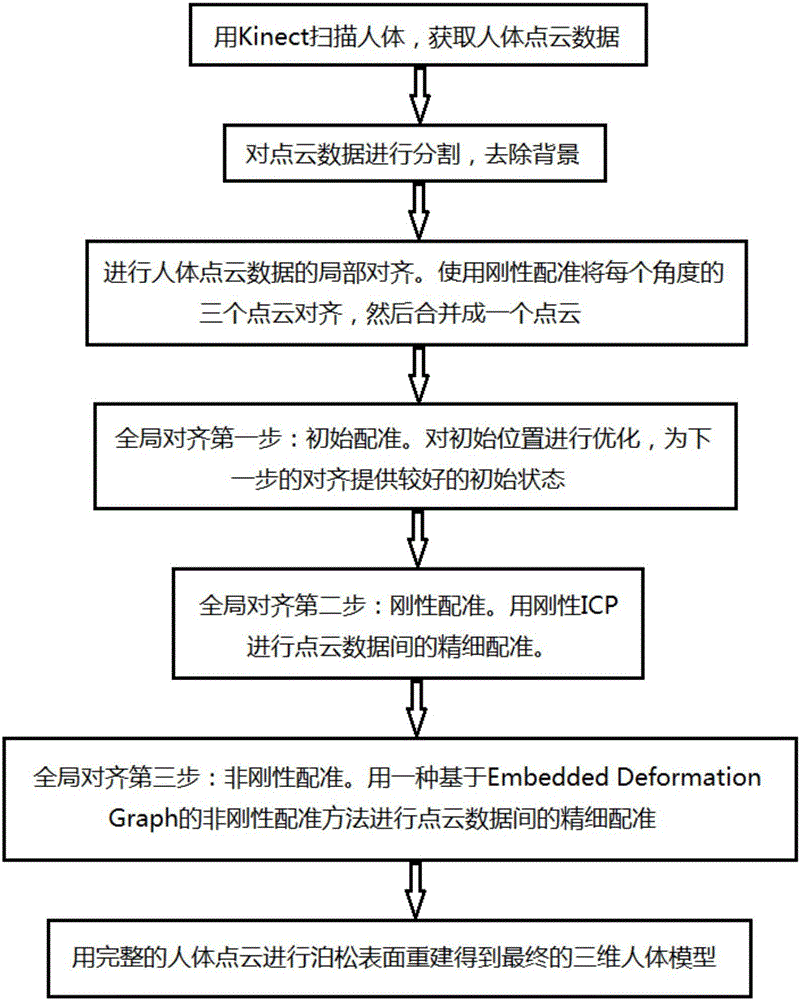

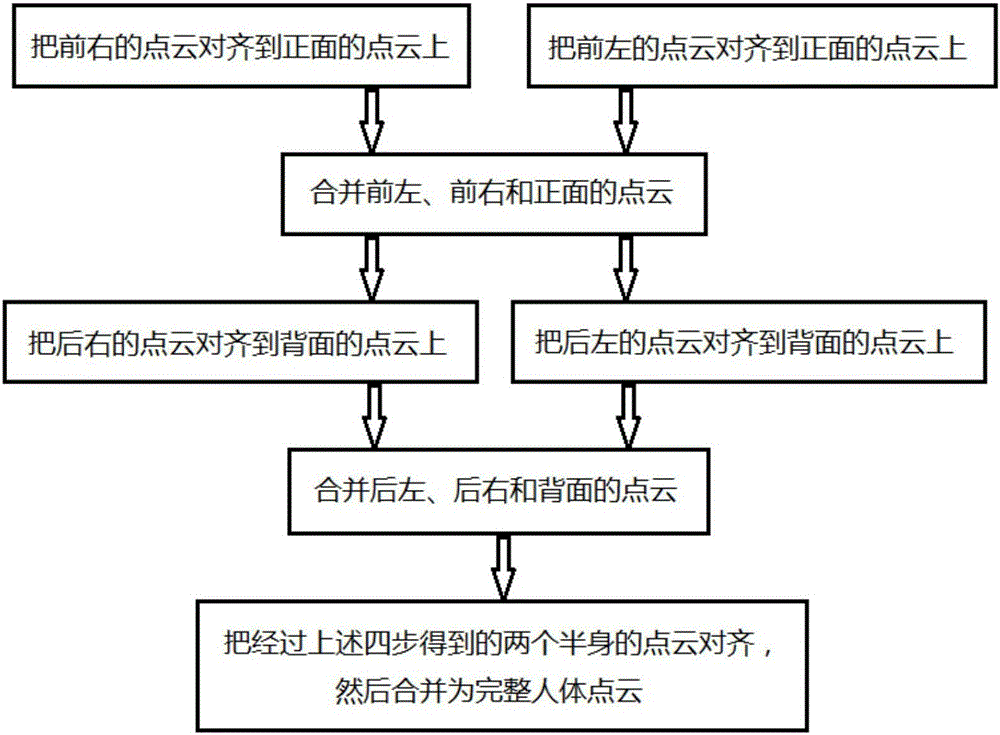

Simple and high-efficient three-dimensional human body reconstruction method based on single Kinect

The invention discloses a simple and high-efficient three-dimensional human body reconstruction method based on a single Kinect. The three-dimensional human body reconstruction method comprises the following steps of 1) acquiring point cloud; 2) carrying out point cloud pretreatment; 3) carrying out local aligning; 4) carrying out global aligning; and 5) carrying out surface reconstruction. A user can easily realize three-dimensional human body modeling in a narrow space, such as a home room or an office room, and only a personal computer and a Kinect are needed. In order to make the human body modeling become rapid, accurate and convenient, the invention provides an effective whole body scanning data acquisition strategy. Through six angles, three frame scanning is performed for each angle so that the human body can be completely covered. Point cloud data processing captured by the Kinect includes two steps of the local aligning and the global aligning. The new three dimensional human body modeling method can be suitable for most of applications, such as digital measurement, a product design and on-line shopping.

Owner:SOUTH CHINA UNIV OF TECH

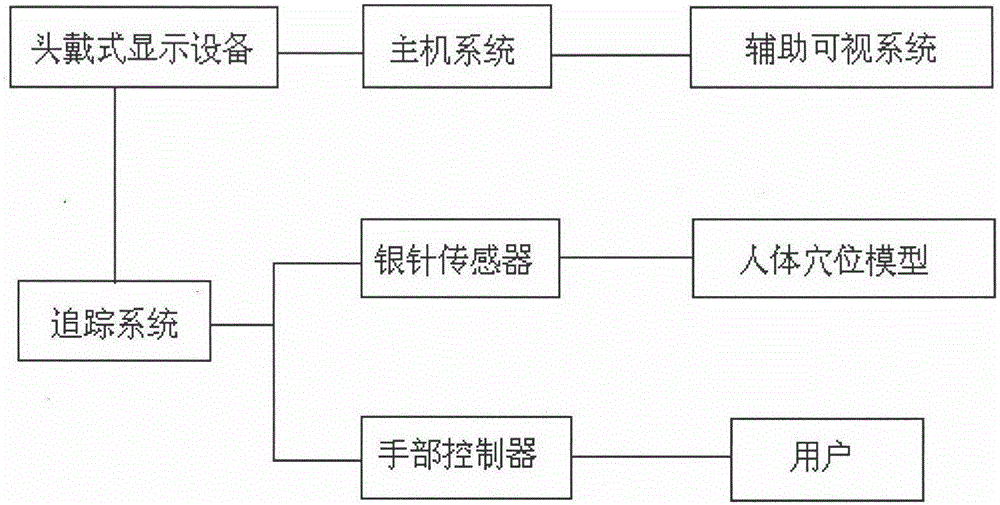

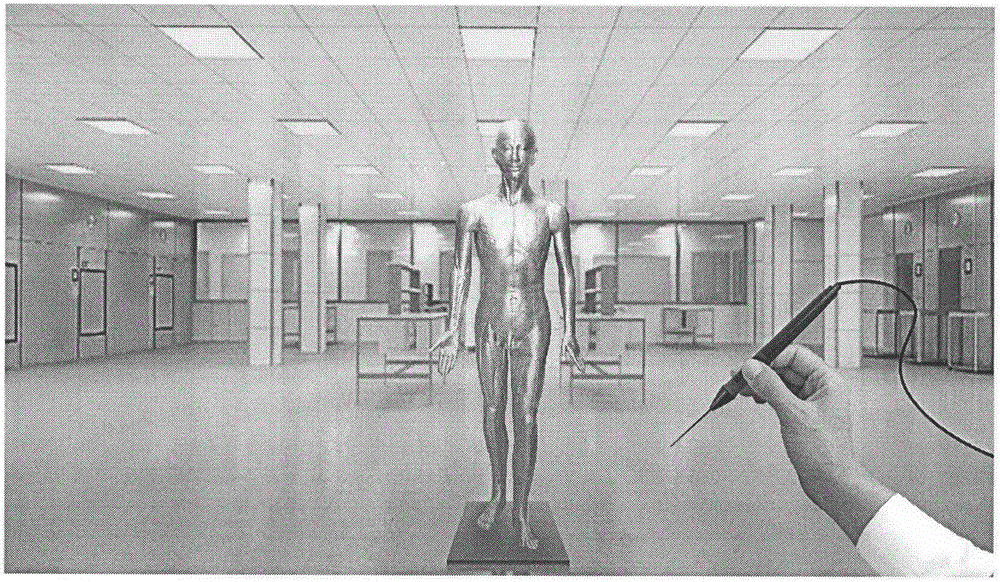

Acupuncture acupoint determination auxiliary teaching system

InactiveCN106327983AFine and accurate interactive experienceImprove realismEducational modelsHuman bodyAcupuncture treatment

Owner:CHENGDU CTC TIANFU DIGITAL TECH +1

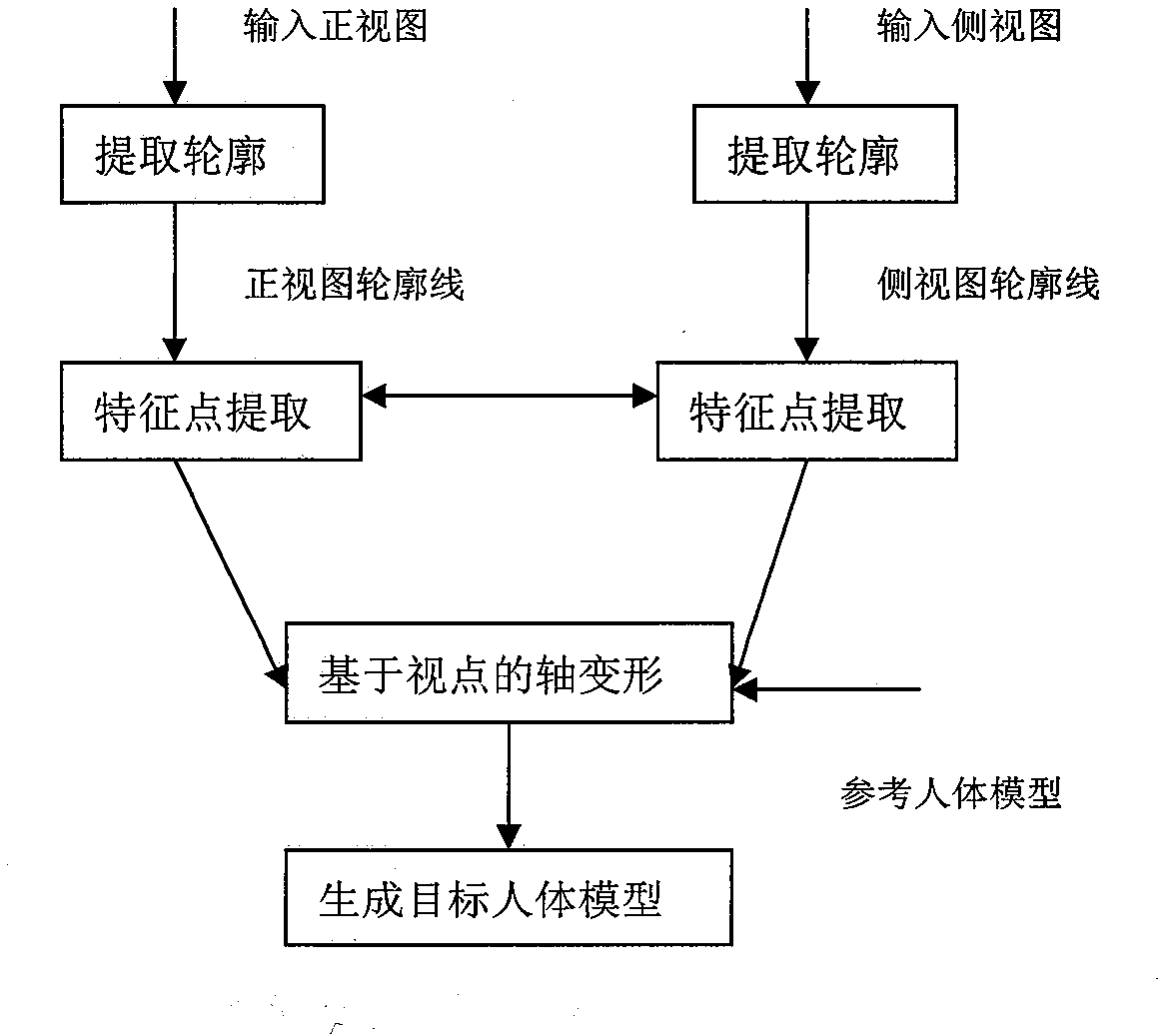

Three-dimensional virtual fitting system

InactiveCN103106586AImprove the design levelImprove efficiencyCommerceImage data processingHuman bodyPersonalization

The invention discloses a three-dimensional virtual fitting system and relates to the technical field of robot vision and digitized costume design. The three-dimensional virtual fitting system is characterized in that the object of costume three-dimensional virtual fitting is a three-dimensional human body model which is built through shooting and processing of a real human body. A customer is shot by a camera to obtain multiple groups of images; contour extraction and feature extraction are carried out on the images in a computer, based on axial deformation of viewpoints, with the human body model as reference, further factors including human body types and the like are considered, and the real-person human body model of the customer is finally obtained; the obtained model is input into the three-dimensional fitting system; through two-way selection, a style, cloth, design and color and the like of clothes are determined by the customer and a designer; the data are input into a 'custom-made system' to complete a costume design, an individual fashion sample is generated automatically and input back into the three-dimensional fitting system, and then a custom ready-to-wear is sewed in a virtual mode and worn on the real-person human body model to display an individual fitting effect intuitively; relative marking is carried out by an evaluation system, and scores can be a reference index for the customer and the designer; and the design level and design efficiency of the costume are greatly improved.

Owner:JIANGNAN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com