Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

21830 results about "Polycrystalline silicon" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Polycrystalline silicon, also called polysilicon or poly-Si, is a high purity, polycrystalline form of silicon, used as a raw material by the solar photovoltaic and electronics industry. Polysilicon is produced from metallurgical grade silicon by a chemical purification process, called the Siemens process. This process involves distillation of volatile silicon compounds, and their decomposition into silicon at high temperatures. An emerging, alternative process of refinement uses a fluidized bed reactor. The photovoltaic industry also produces upgraded metallurgical-grade silicon (UMG-Si), using metallurgical instead of chemical purification processes. When produced for the electronics industry, polysilicon contains impurity levels of less than one part per billion (ppb), while polycrystalline solar grade silicon (SoG-Si) is generally less pure. A few companies from China, Germany, Japan, Korea and the United States, such as GCL-Poly, Wacker Chemie, OCI, and Hemlock Semiconductor, as well as the Norwegian headquartered REC, accounted for most of the worldwide production of about 230,000 tonnes in 2013.

Memory cell incorporating a chalcogenide element and method of making same

Owner:ROUND ROCK RES LLC

Formation of deep via airgaps for three dimensional wafer to wafer interconnect

InactiveUS20060223301A1Semiconductor/solid-state device detailsSolid-state devicesConductive materialsSemiconductor

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

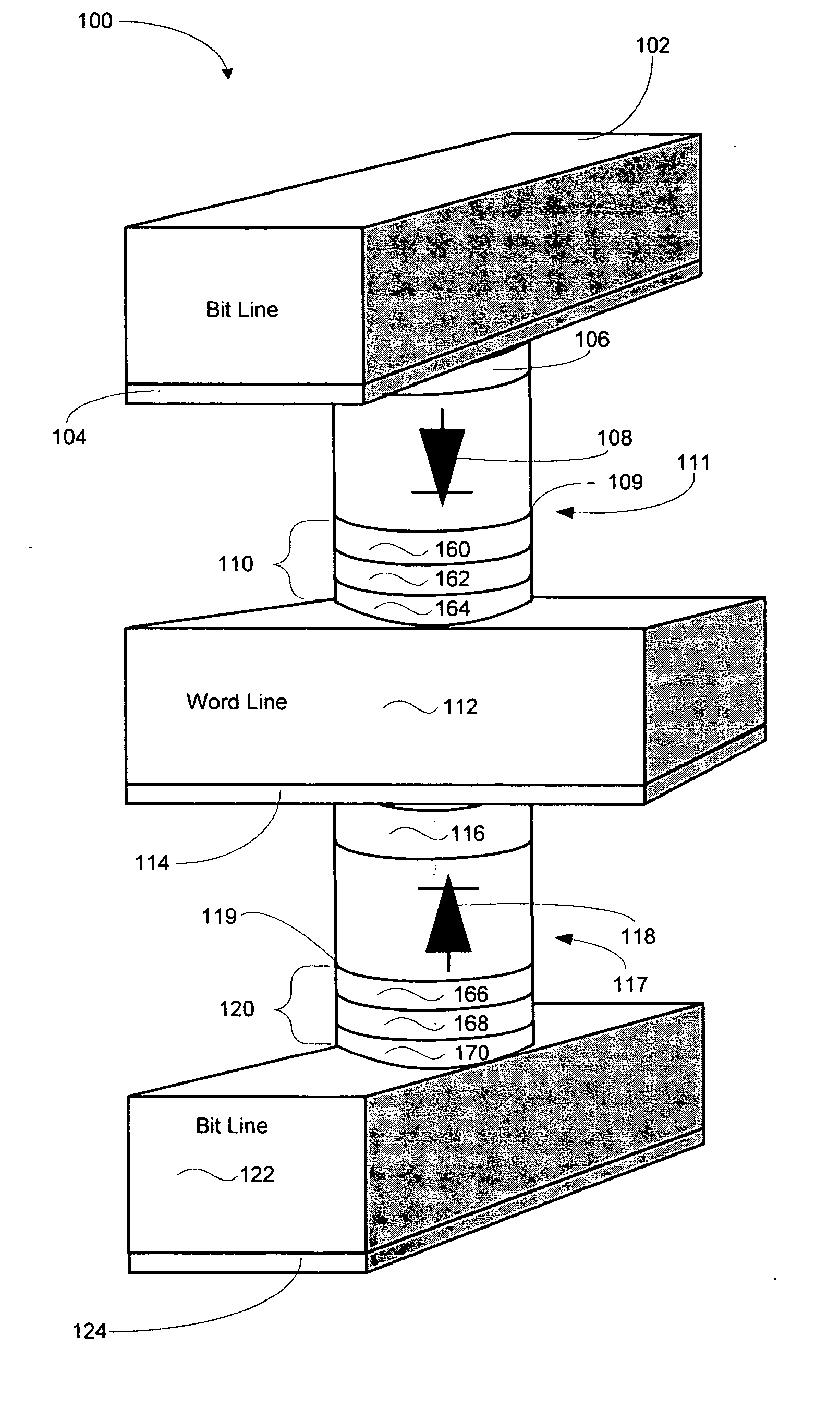

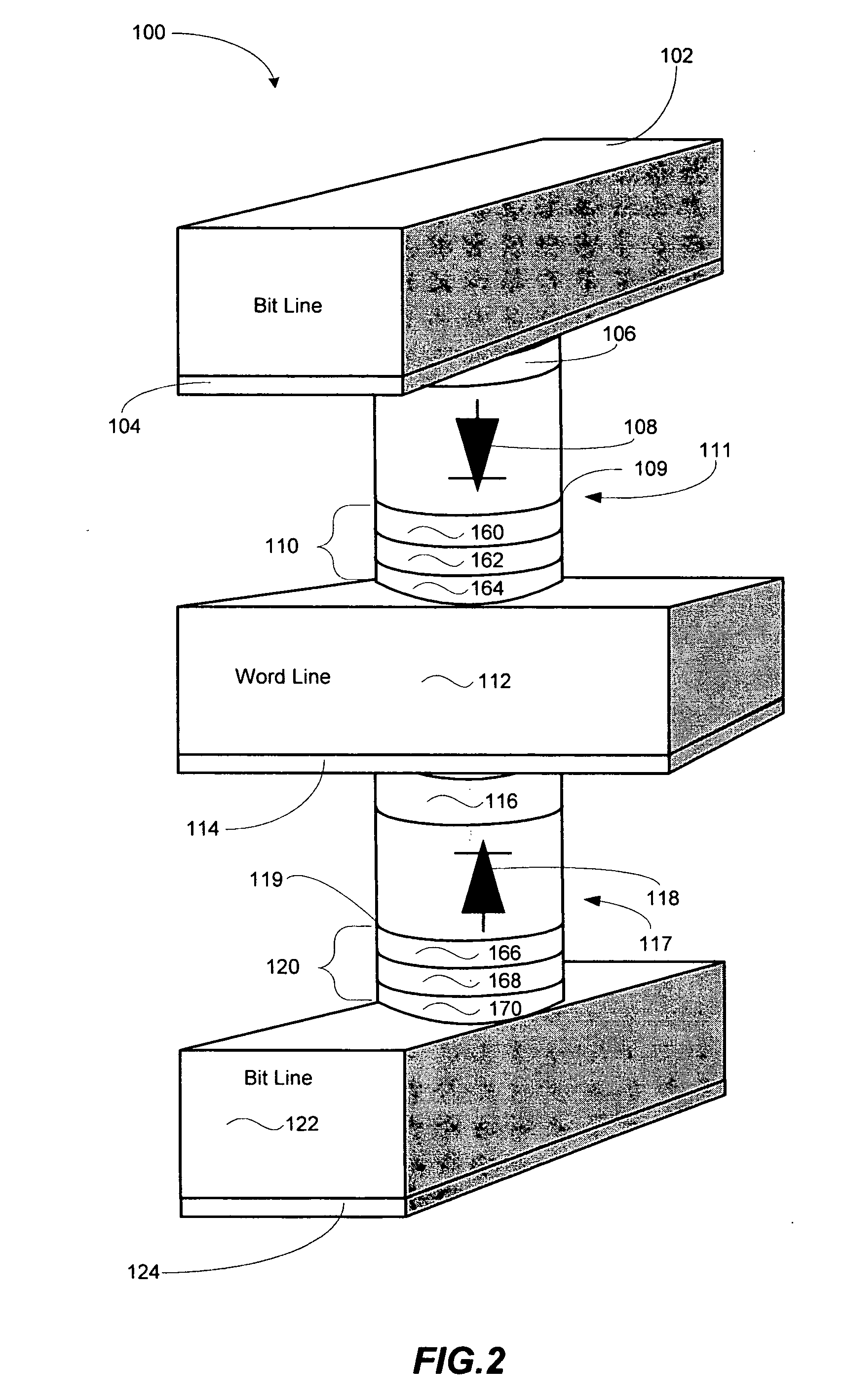

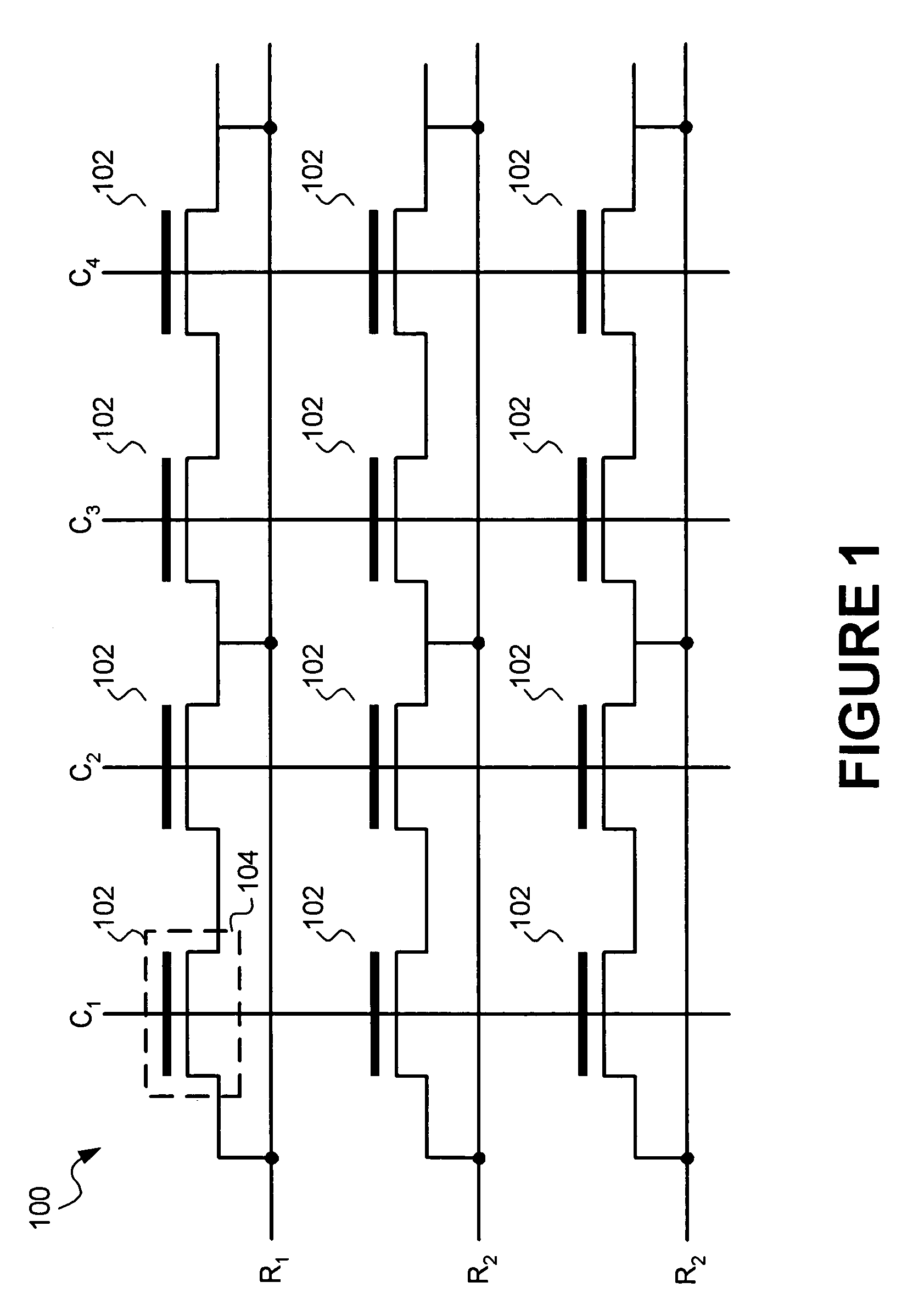

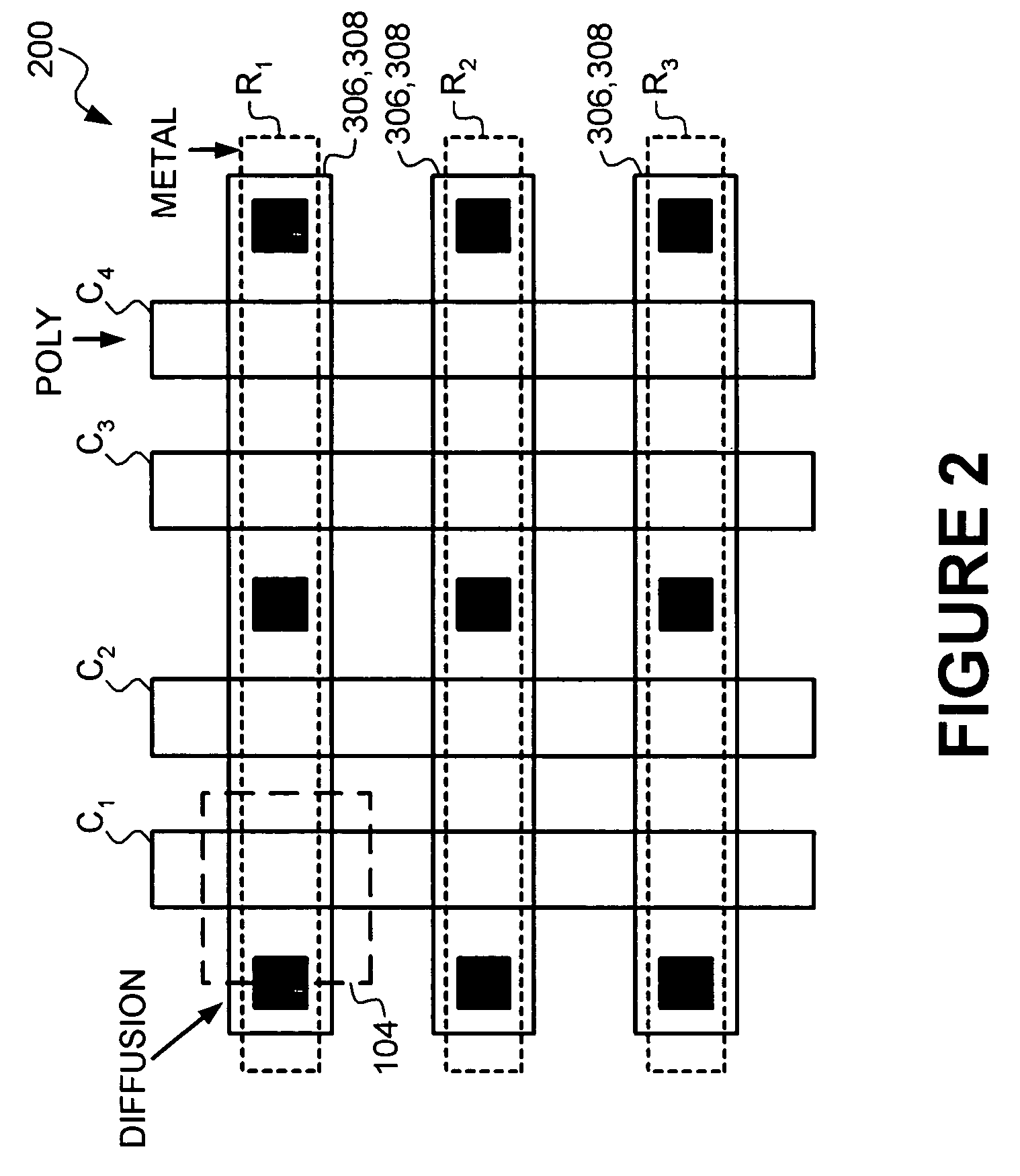

Unipolar resistance random access memory (RRAM) device and vertically stacked architecture

InactiveUS20070132049A1Improve performanceGalvano-magnetic devicesSolid-state devicesRandom access memoryEngineering

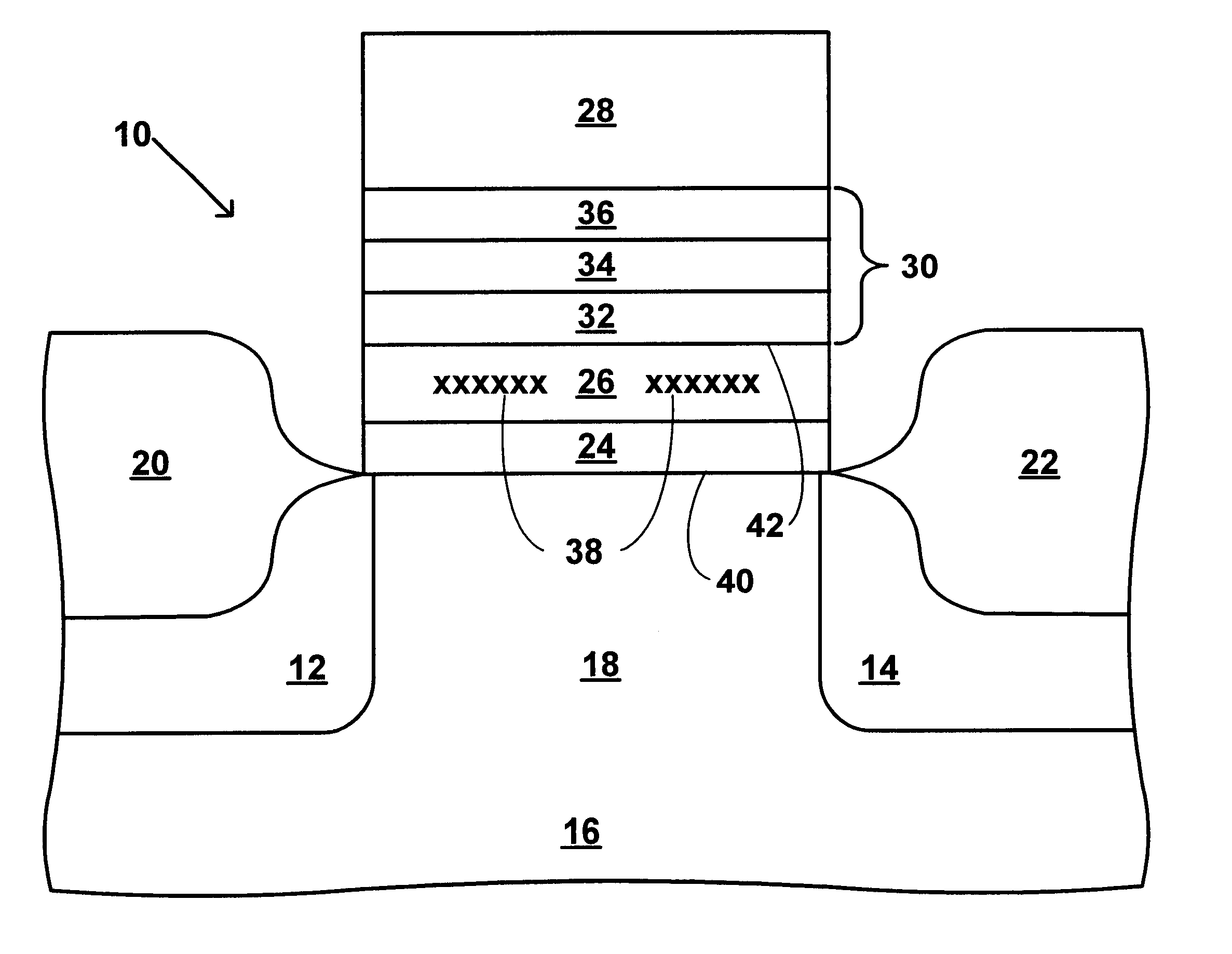

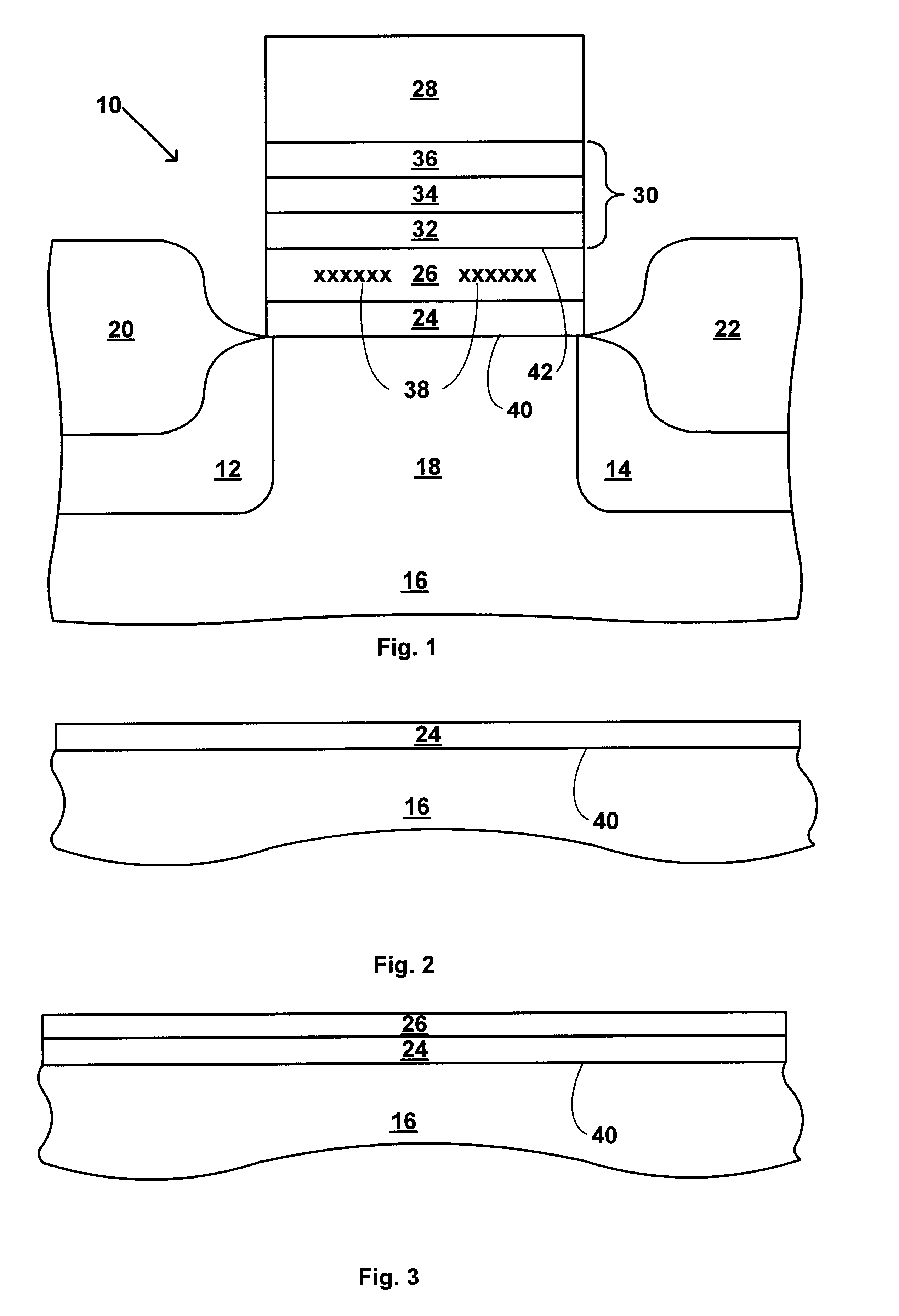

One embodiment of the present invention includes a low-cost unipolar rewritable variable-resistance memory device, made of cross-point arrays of memory cells, vertically stacked on top of one another and compatible with a polycrystalline silicon diode.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

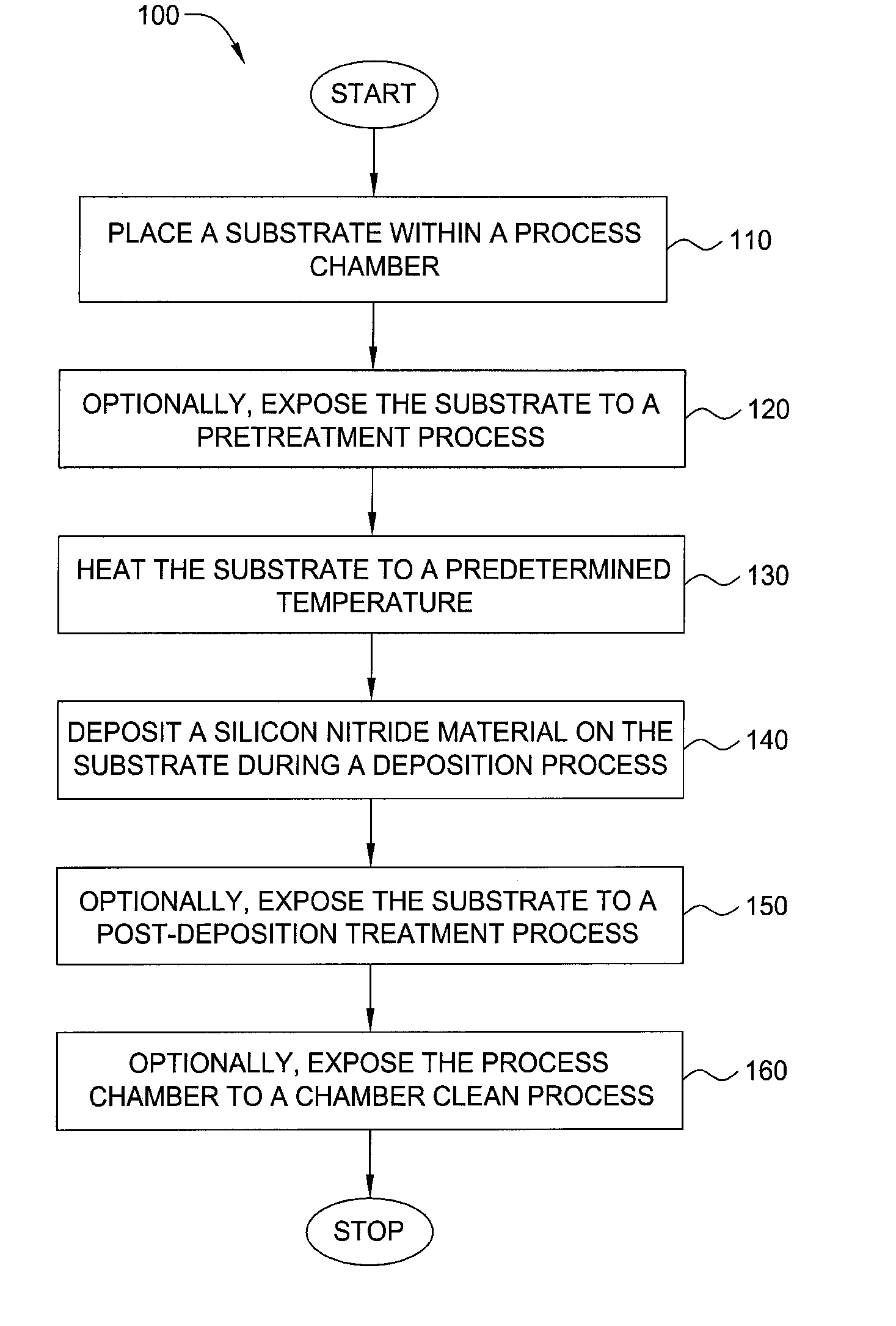

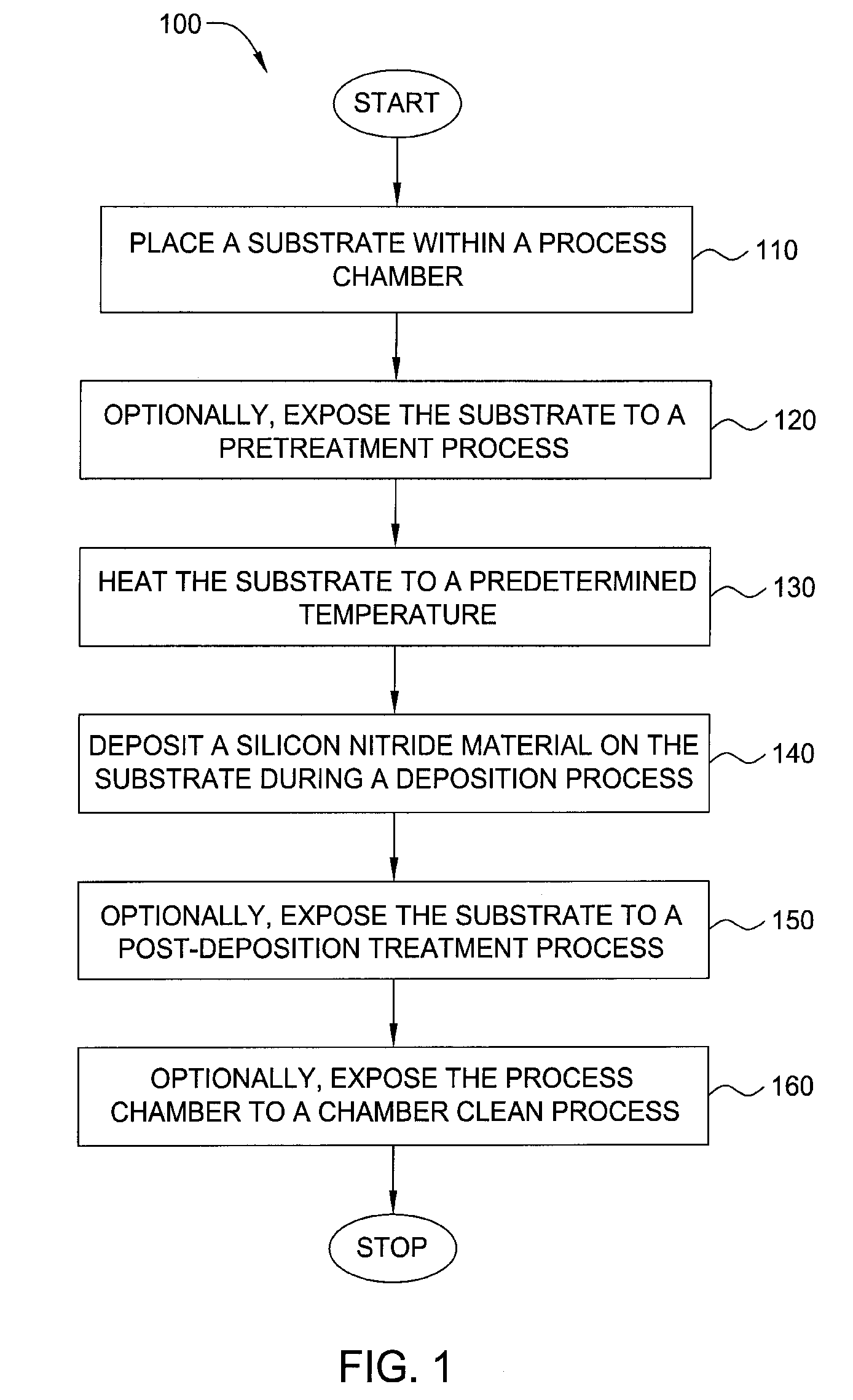

Method for forming silicon-containing materials during a photoexcitation deposition process

InactiveUS20060286774A1Enhance chamber cleaning processHigh surface energyPolycrystalline material growthSemiconductor/solid-state device manufacturingVolatilesSilicon oxide

Embodiments of the invention generally provide a method for depositing films or layers using a UV source during a photoexcitation process. The films are deposited on a substrate and usually contain a material, such as silicon (e.g., epitaxy, crystalline, microcrystalline, polysilicon, or amorphous), silicon oxide, silicon nitride, silicon oxynitride, or other silicon-containing materials. The photoexcitation process may expose the substrate and / or gases to an energy beam or flux prior to, during, or subsequent a deposition process. Therefore, the photoexcitation process may be used to pre-treat or post-treat the substrate or material, to deposit the silicon-containing material, and to enhance chamber cleaning processes. Attributes of the method that are enhanced by the UV photoexcitation process include removing native oxides prior to deposition, removing volatiles from deposited films, increasing surface energy of the deposited films, increasing the excitation energy of precursors, reducing deposition time, and reducing deposition temperature.

Owner:APPLIED MATERIALS INC

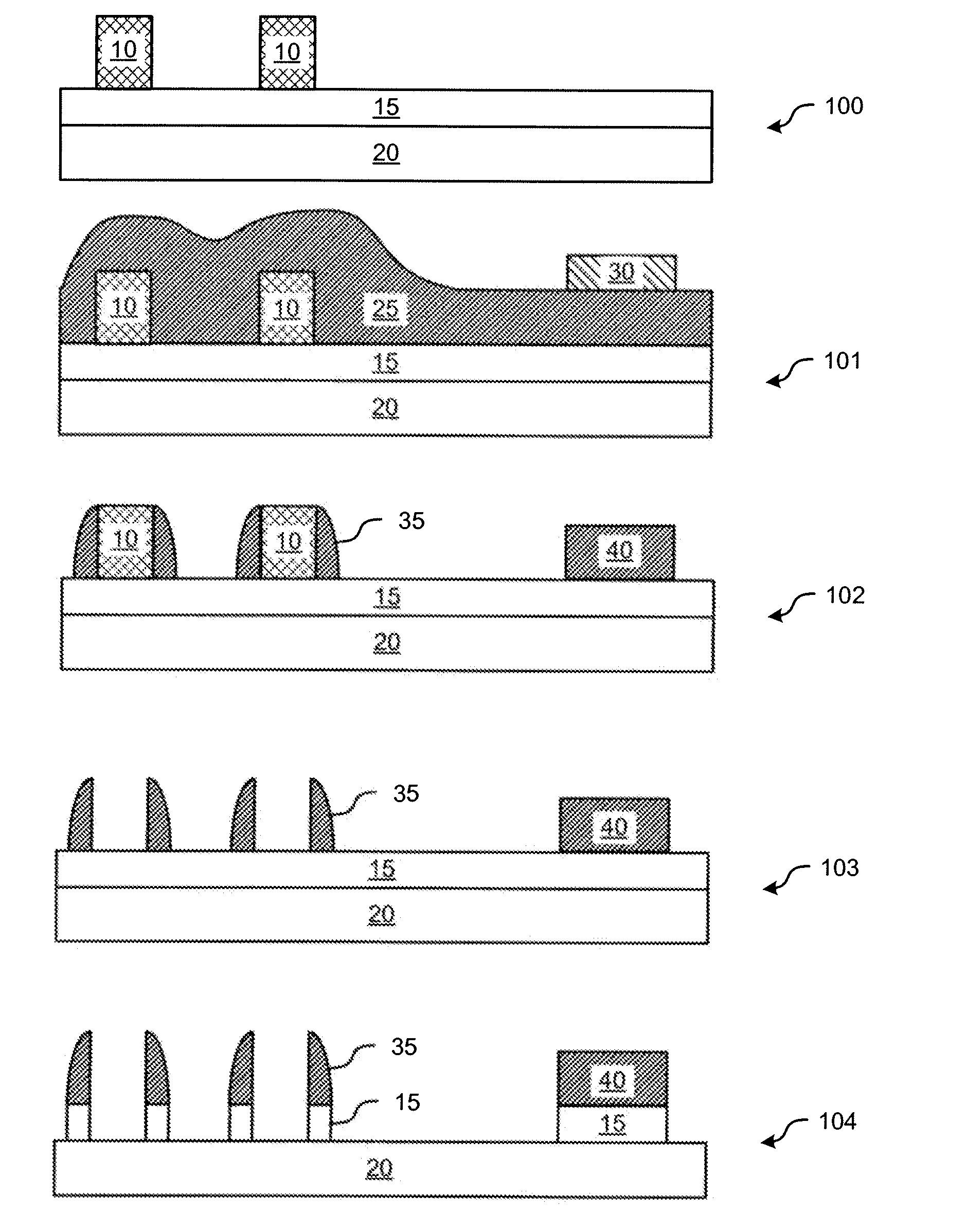

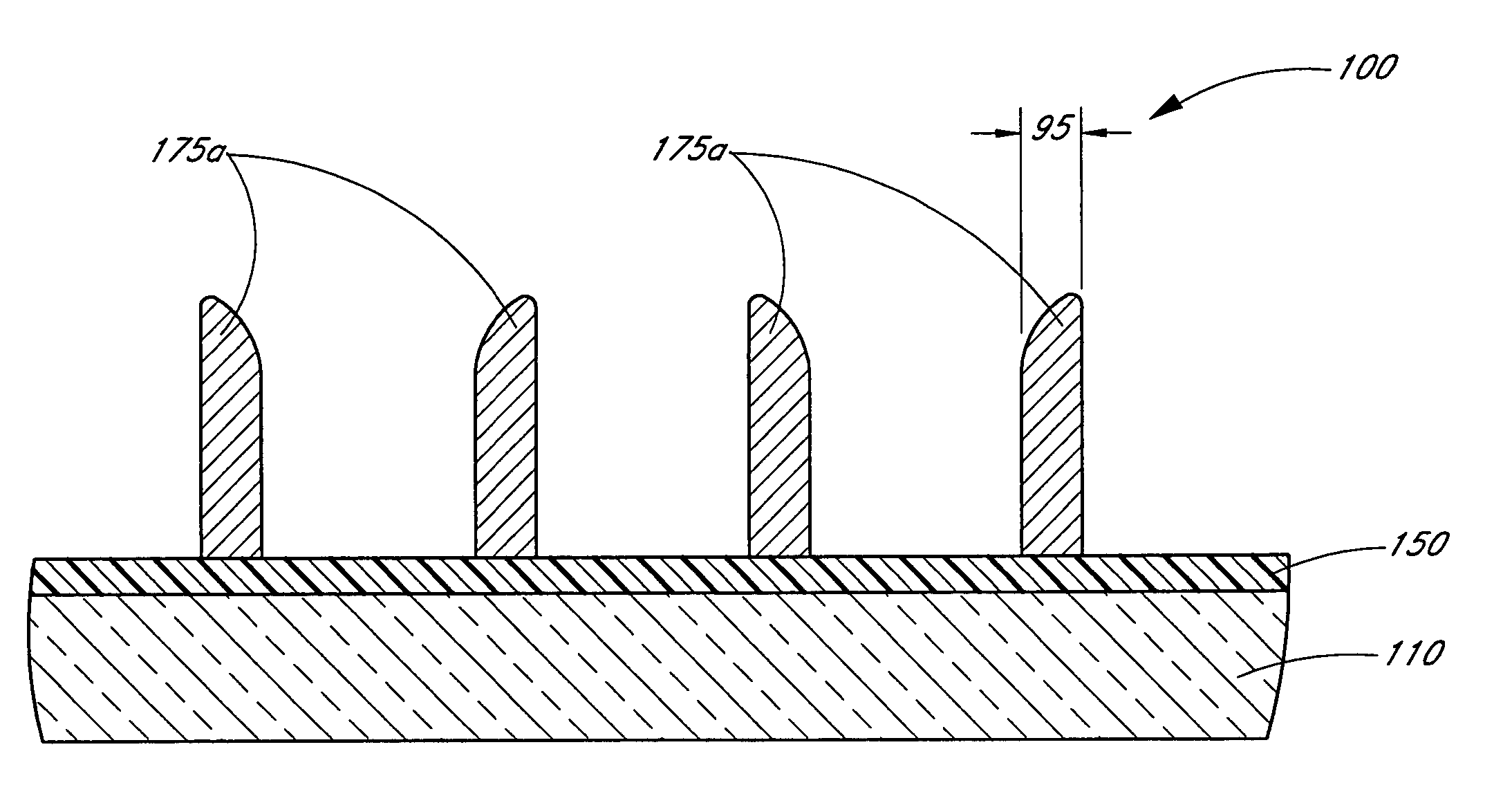

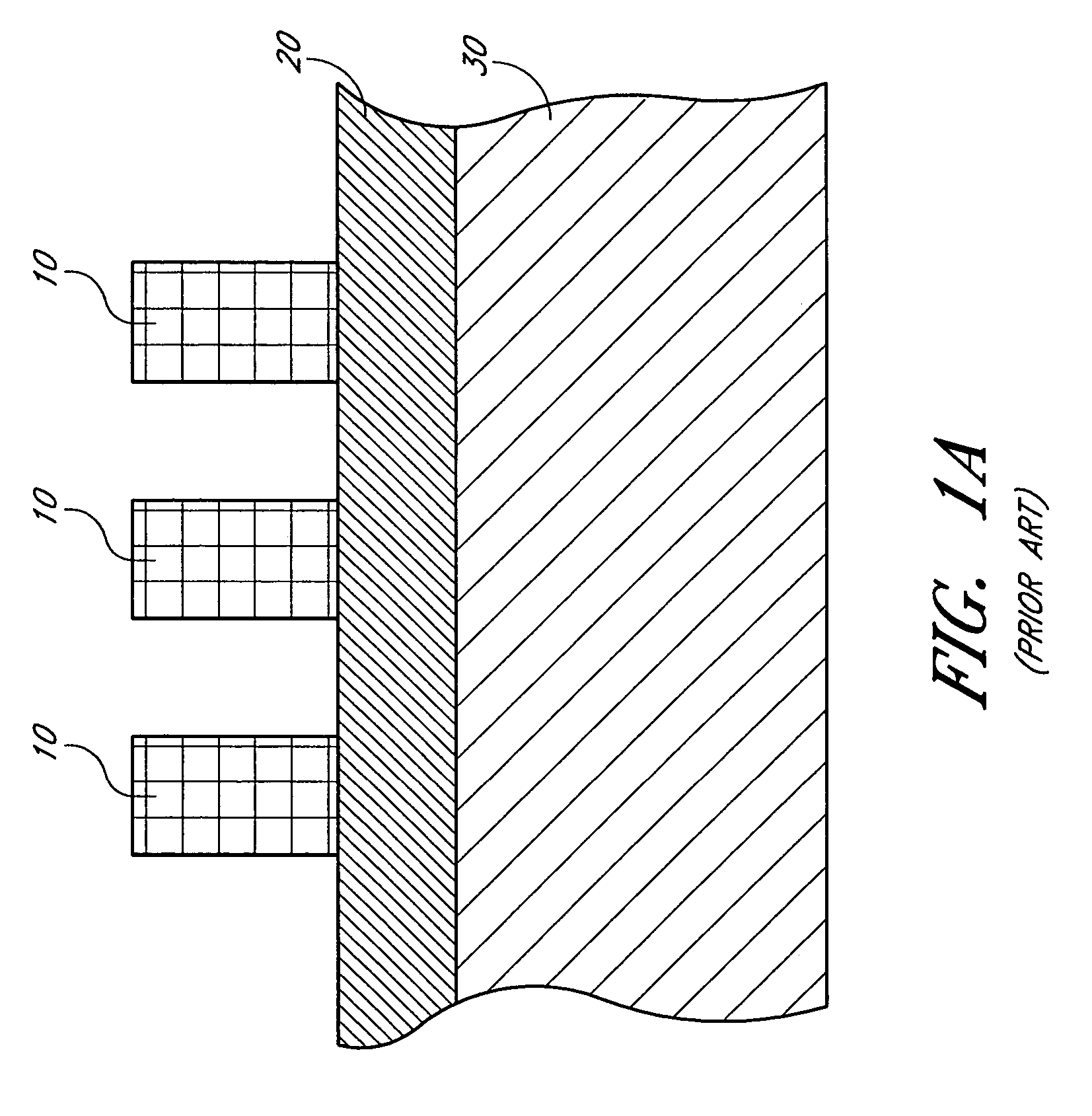

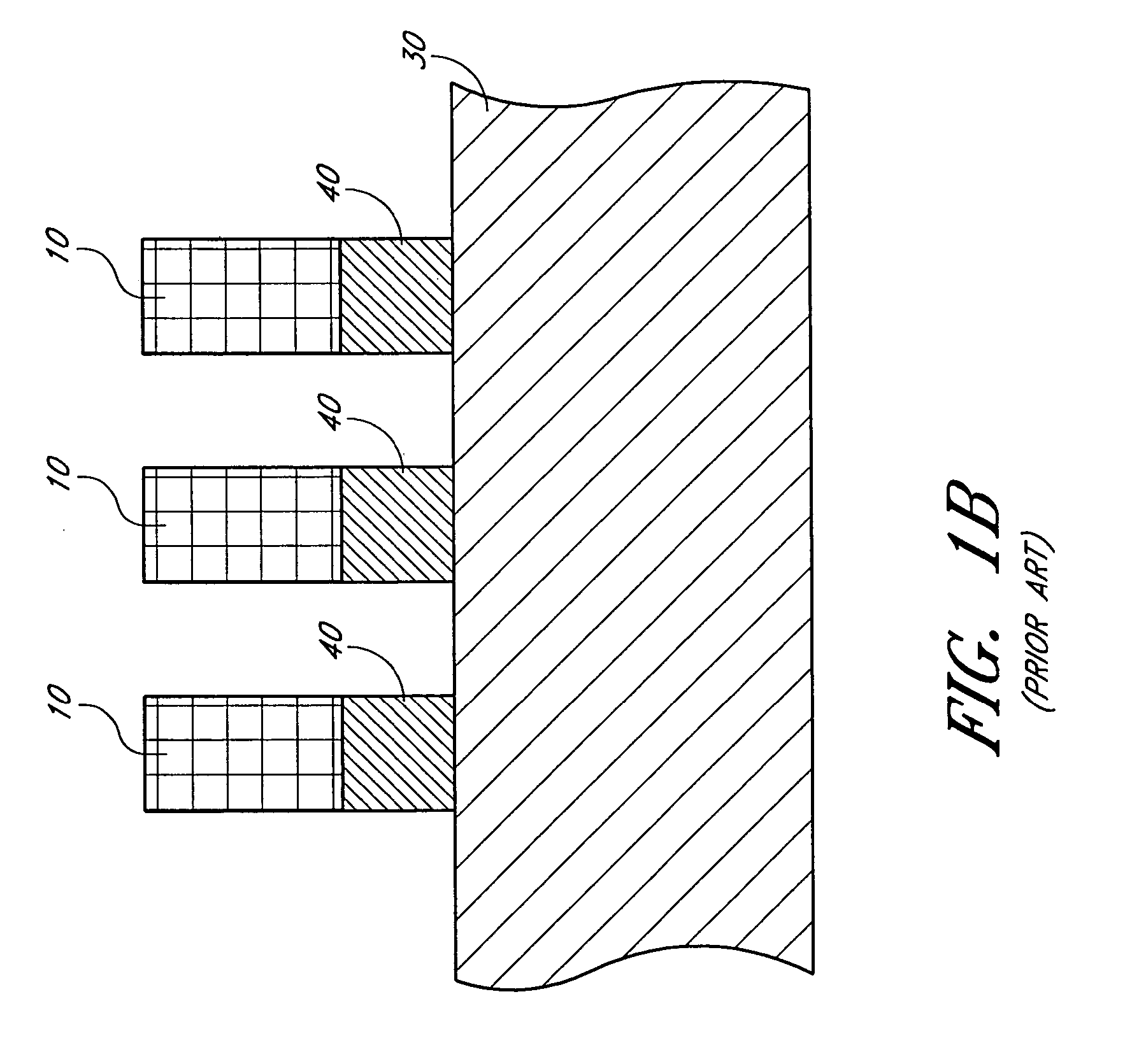

Method of eliminating a lithography operation

ActiveUS20090146322A1Semiconductor/solid-state device detailsSolid-state devicesLithographic artistEngineering

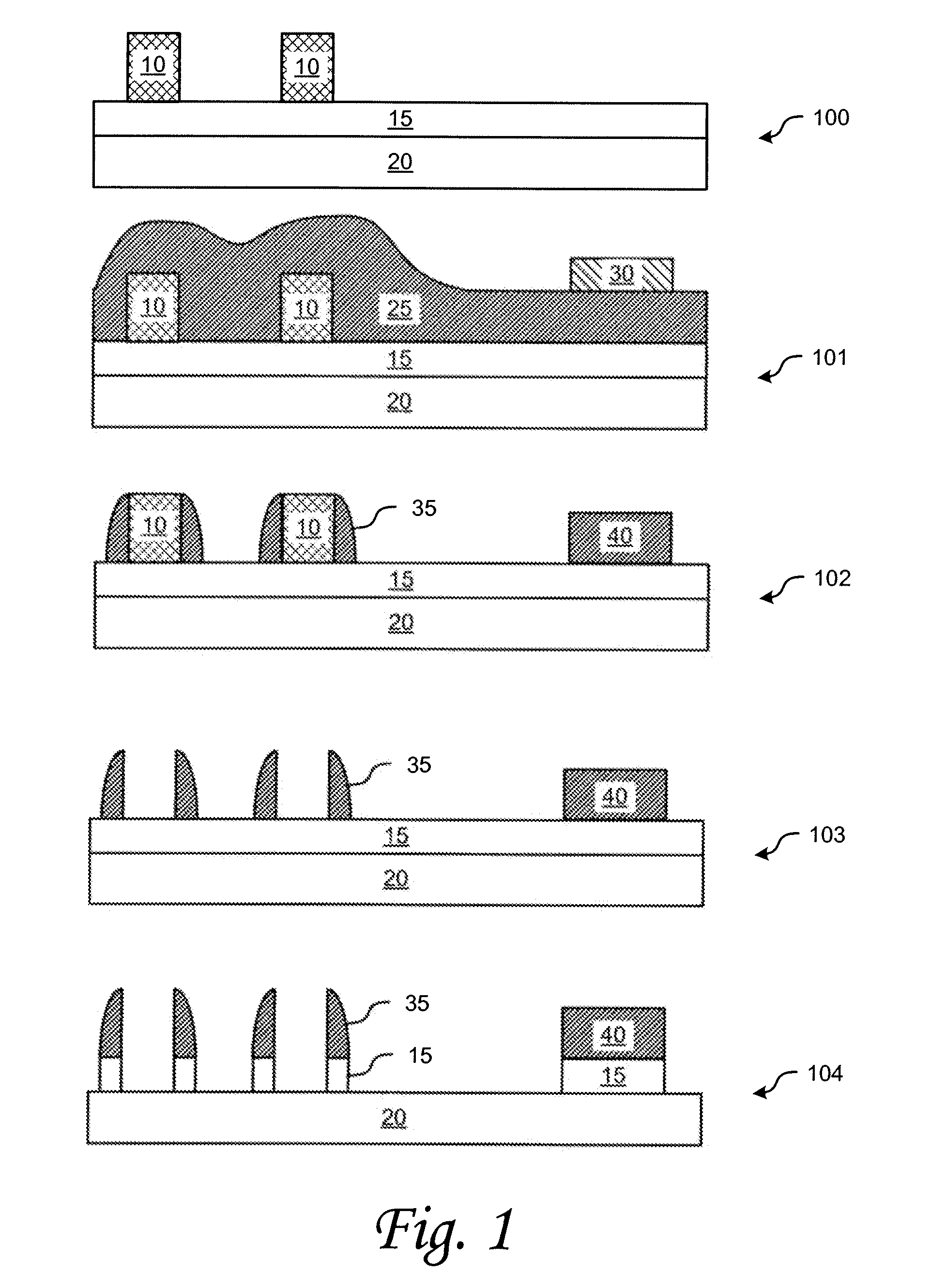

Methods of semiconductor device fabrication are disclosed. An exemplary method includes processes of depositing a first pattern on a semiconductor substrate, wherein the first pattern defines wide and narrow spaces; depositing spacer material over the first pattern on the substrate; etching the spacer material such that the spacer material is removed from horizontal surfaces of the substrate and the first pattern but remains adjacent to vertical surfaces of a wide space defined by the first pattern and remains within narrow a space defined by the first pattern; and removing the first pattern from the substrate. In one embodiment, the first pattern can comprise sacrificial material, which can include, for example, polysilicon material. The deposition can comprise physical vapor deposition, chemical vapor deposition, electrochemical deposition, molecular beam epitaxy, atomic layer deposition or other deposition techniques. According to another embodiment, features for lines and logic device components having a width greater than that of the lines are formed in the spacer material in the same mask layer.

Owner:CADENCE DESIGN SYST INC

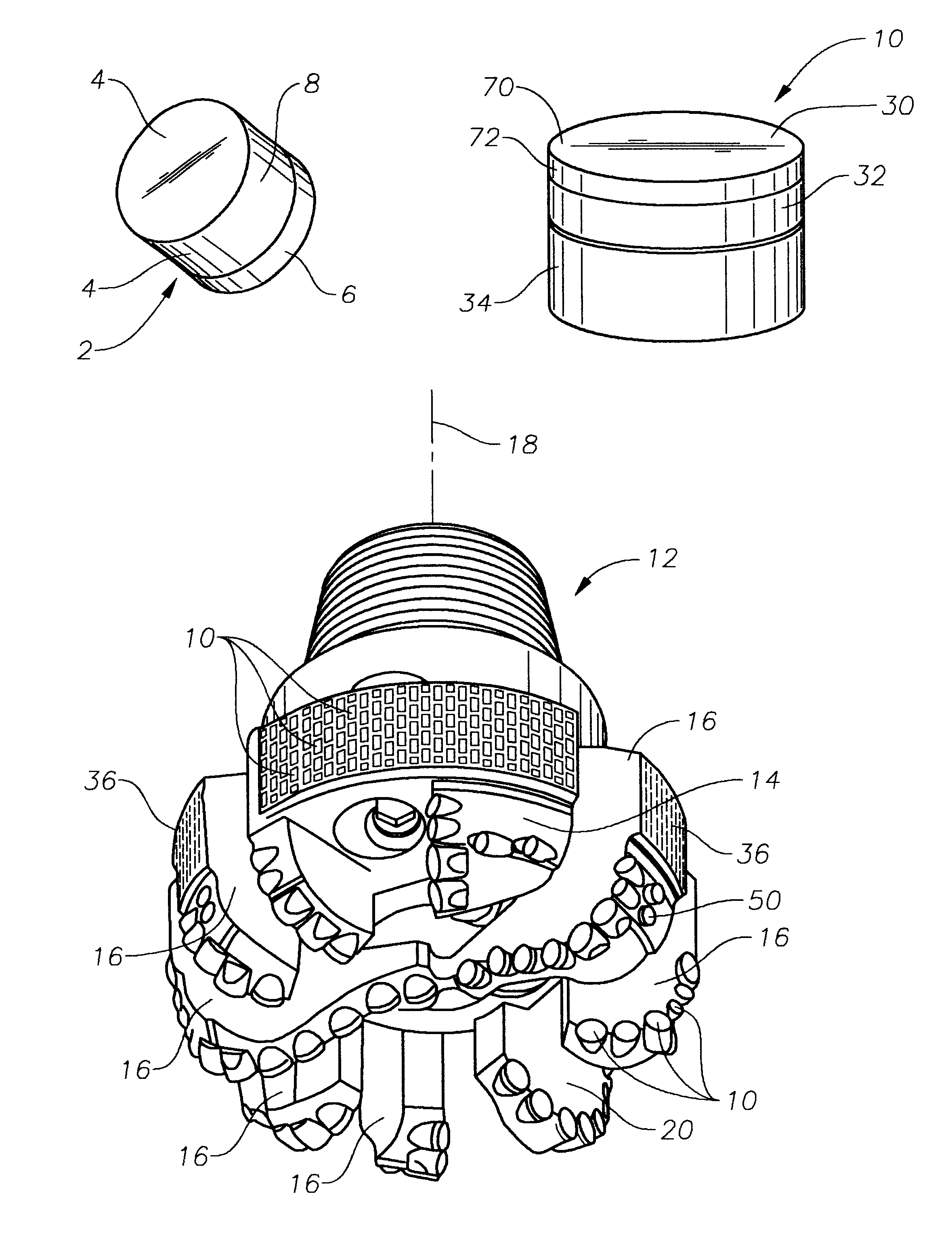

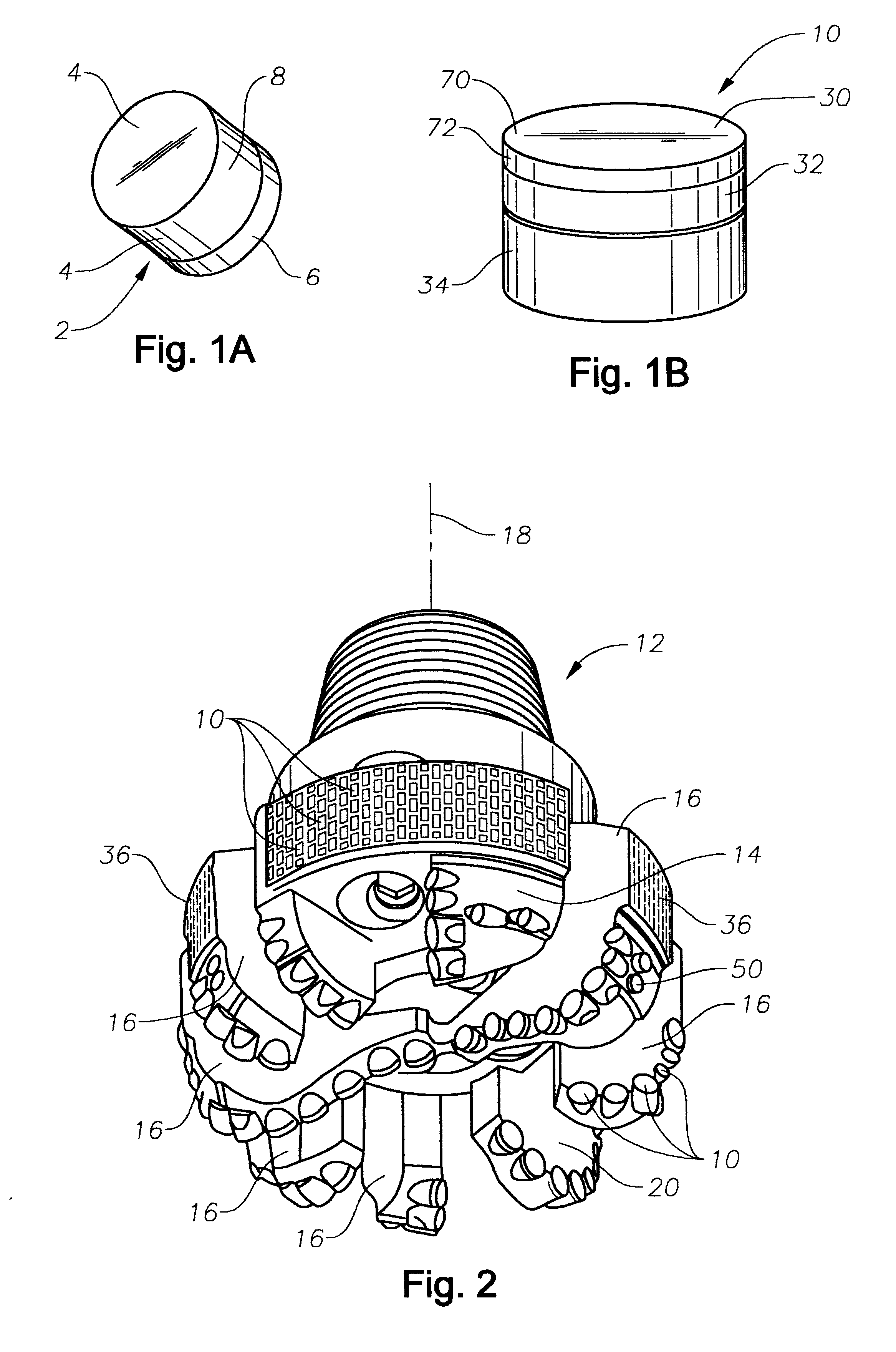

Polycrystalline diamond cutters with working surfaces having varied wear resistance while maintaining impact strength

InactiveUS6601662B2Improve wear resistanceMaintain strengthDrill bitsConstructionsDiamond crystalPolycrystalline diamond

Disclosed is a polycrystalline diamond or diamond-like element with greatly improved wear resistance without loss of impact strength. These elements are formed with a binder-catalyzing material in a high-temperature, high-pressure (HTHP) process. The PCD element has a body with a plurality of bonded diamond or diamond-like crystals forming a continuous diamond matrix that has a diamond volume density greater than 85%. Interstices among the diamond crystals form a continuous interstitial matrix containing a catalyzing material. The diamond matrix table is formed and integrally bonded with a metallic substrate containing the catalyzing material during the HTHP process. The diamond matrix body has a working surface, where a first portion of the interstitial matrix in the body adjacent to the working surface is substantially free of the catalyzing material, and a second portion of the interstitial matrix in the body adjacent to the working surface contains the catalyzing material. The first portion of the interstitial matrix and the second portion of the interstitial matrix have substantially the same impact strength.

Owner:REEDHYCALOG UK

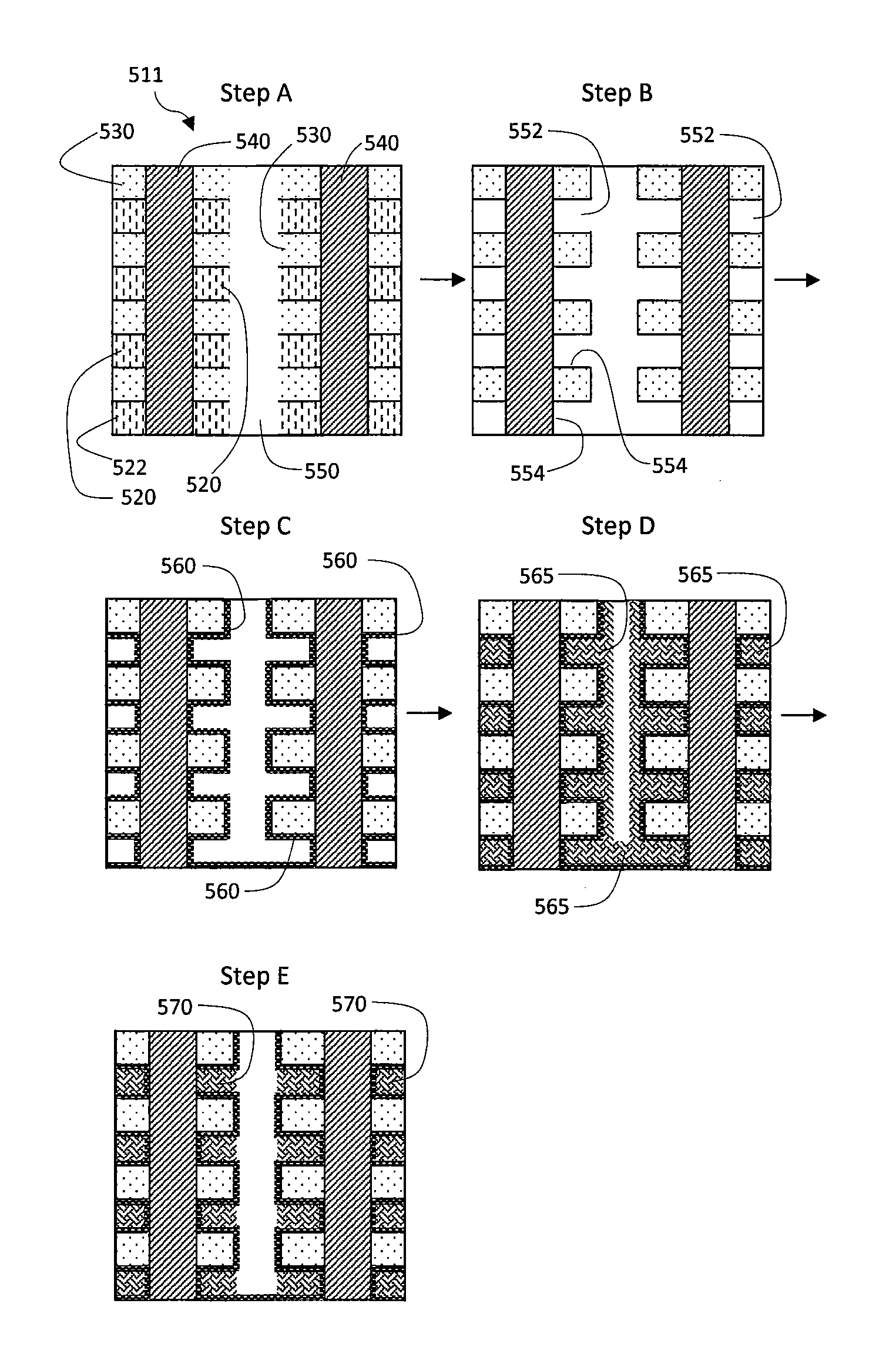

Mask material conversion

ActiveUS7910288B2Photomechanical apparatusSemiconductor/solid-state device manufacturingAmorphous siliconEngineering

The dimensions of mask patterns, such as pitch-multiplied spacers, are controlled by controlled growth of features in the patterns after they are formed. To form a pattern of pitch-multiplied spacers, a pattern of mandrels is first formed overlying a semiconductor substrate. Spacers are then formed on sidewalls of the mandrels by depositing a blanket layer of material over the mandrels and preferentially removing spacer material from horizontal surfaces. The mandrels are then selectively removed, leaving behind a pattern of freestanding spacers. The spacers comprise a material, such as polysilicon and amorphous silicon, known to increase in size upon being oxidized. The spacers are oxidized to grow them to a desired width. After reaching the desired width, the spacers can be used as a mask to pattern underlying layers and the substrate. Advantageously, because the spacers are grown by oxidation, thinner blanket layers can be deposited over the mandrels, thereby allowing the deposition of more conformal blanket layers and widening the process window for spacer formation.

Owner:MICRON TECH INC

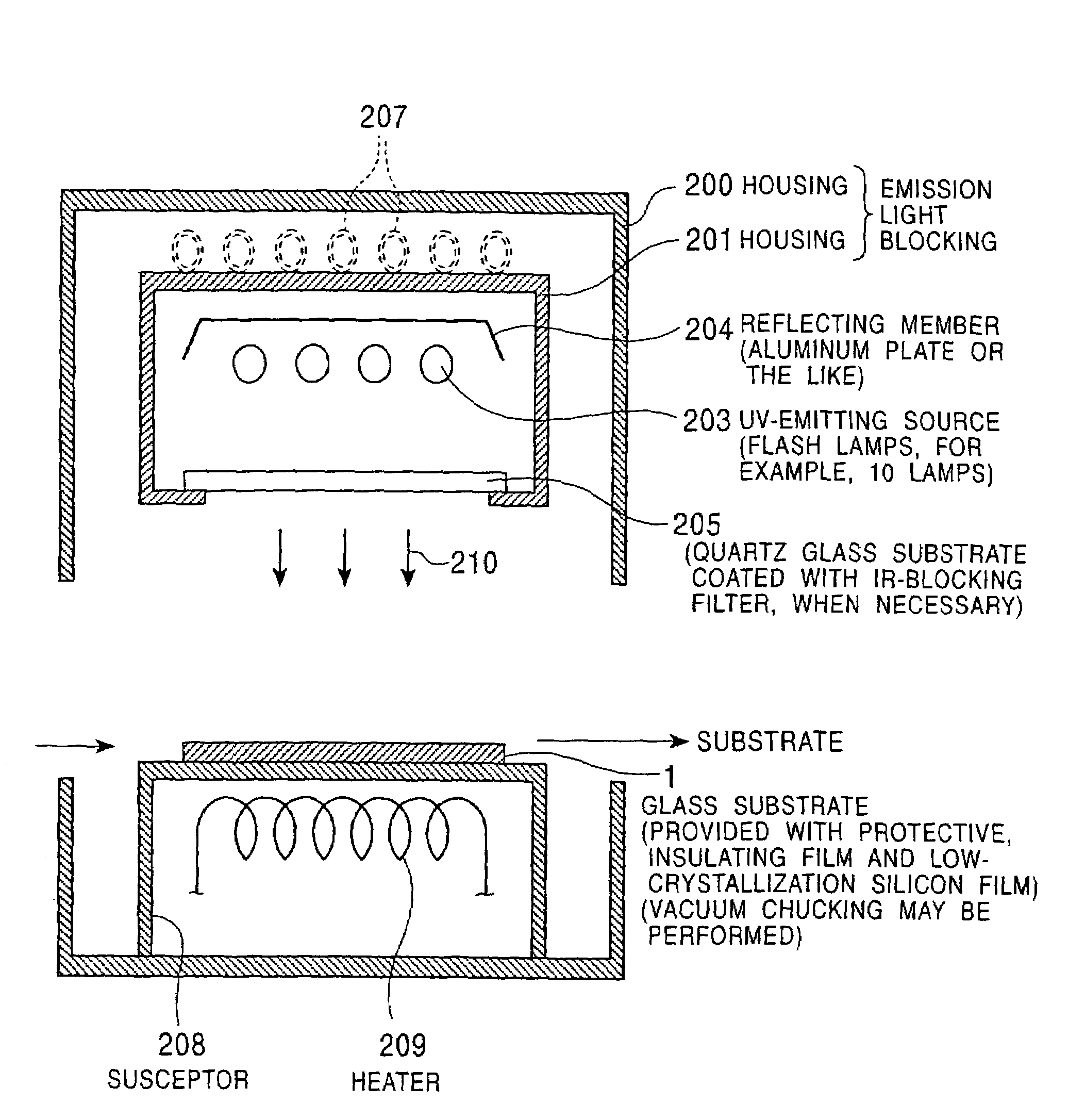

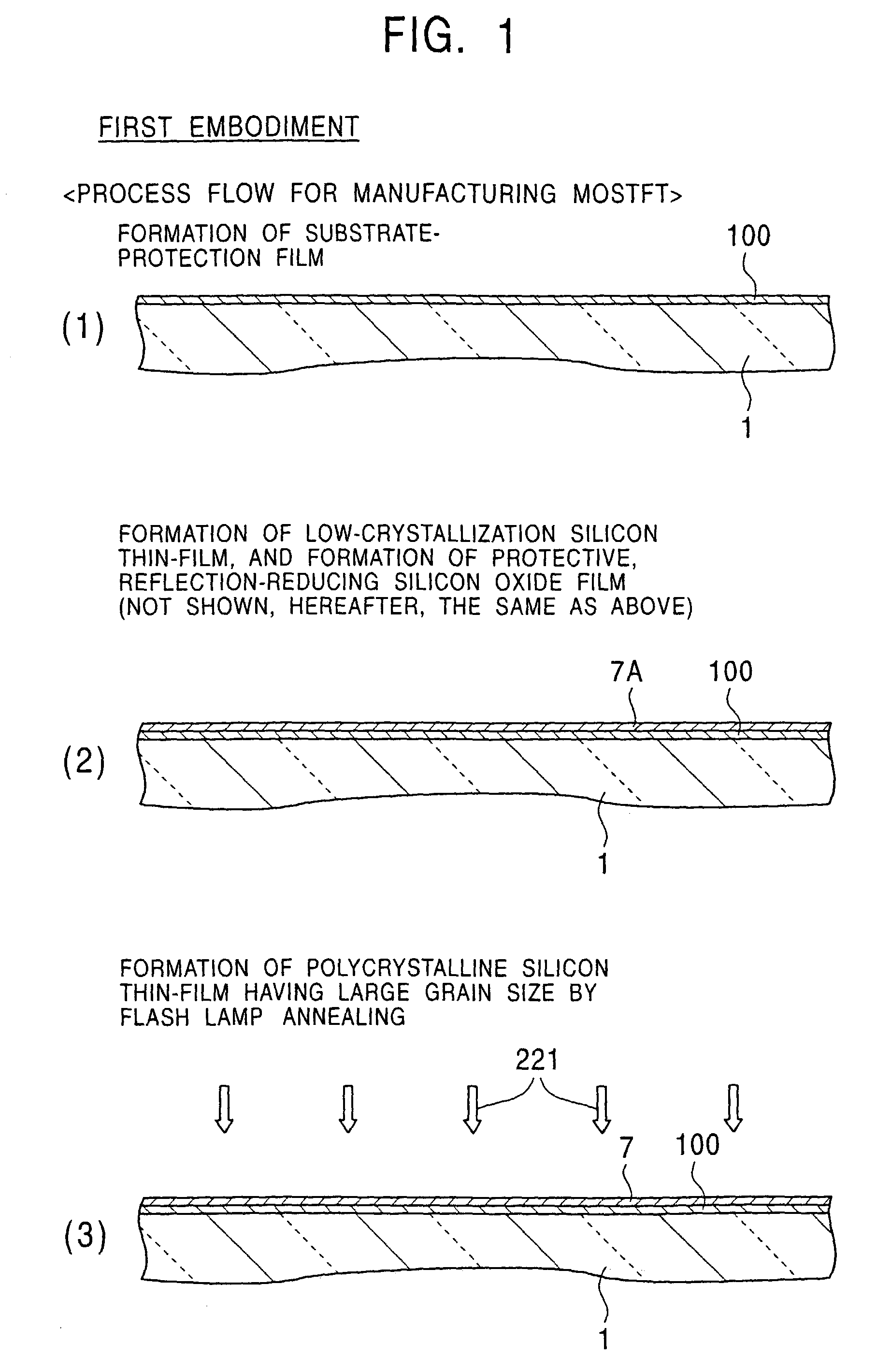

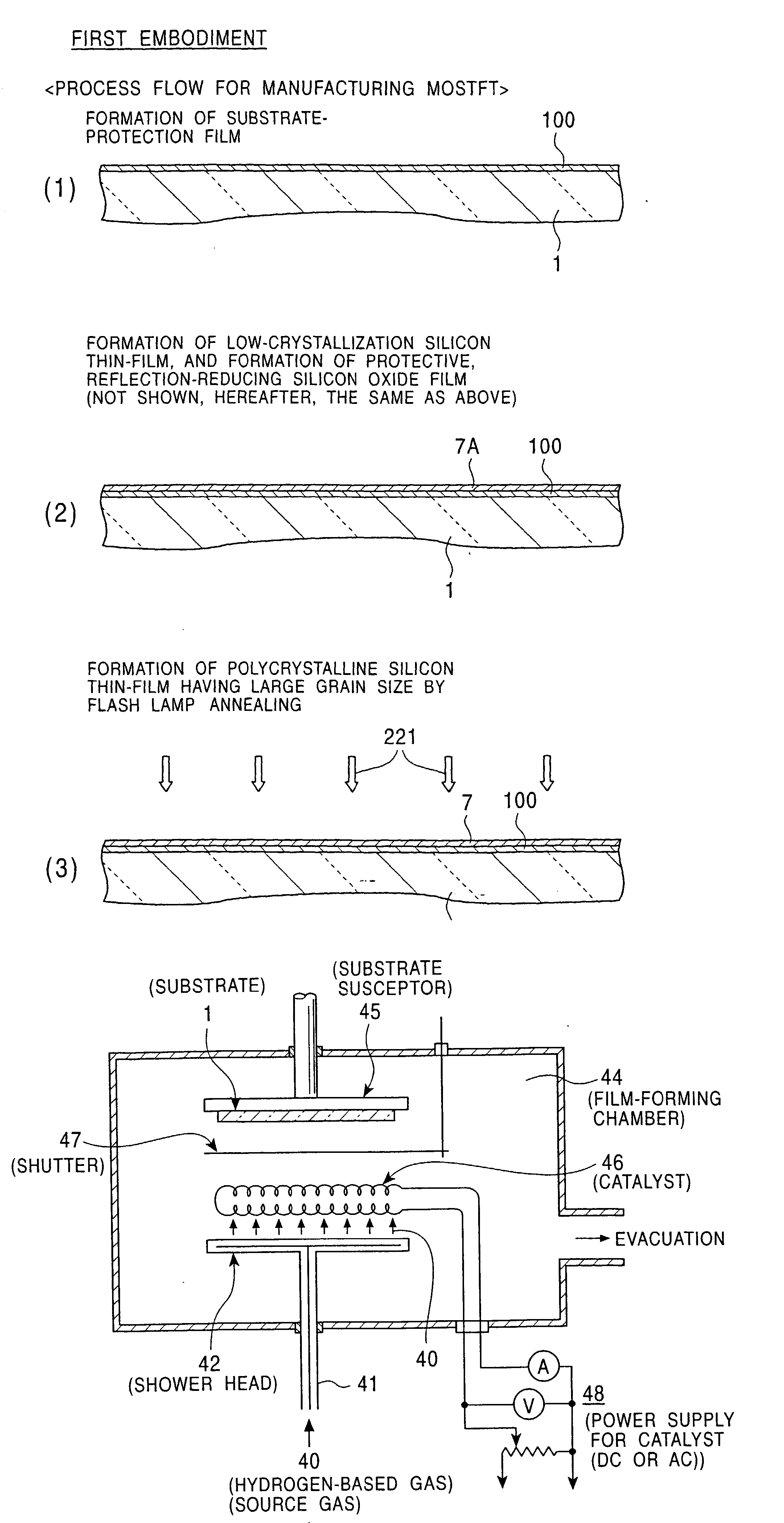

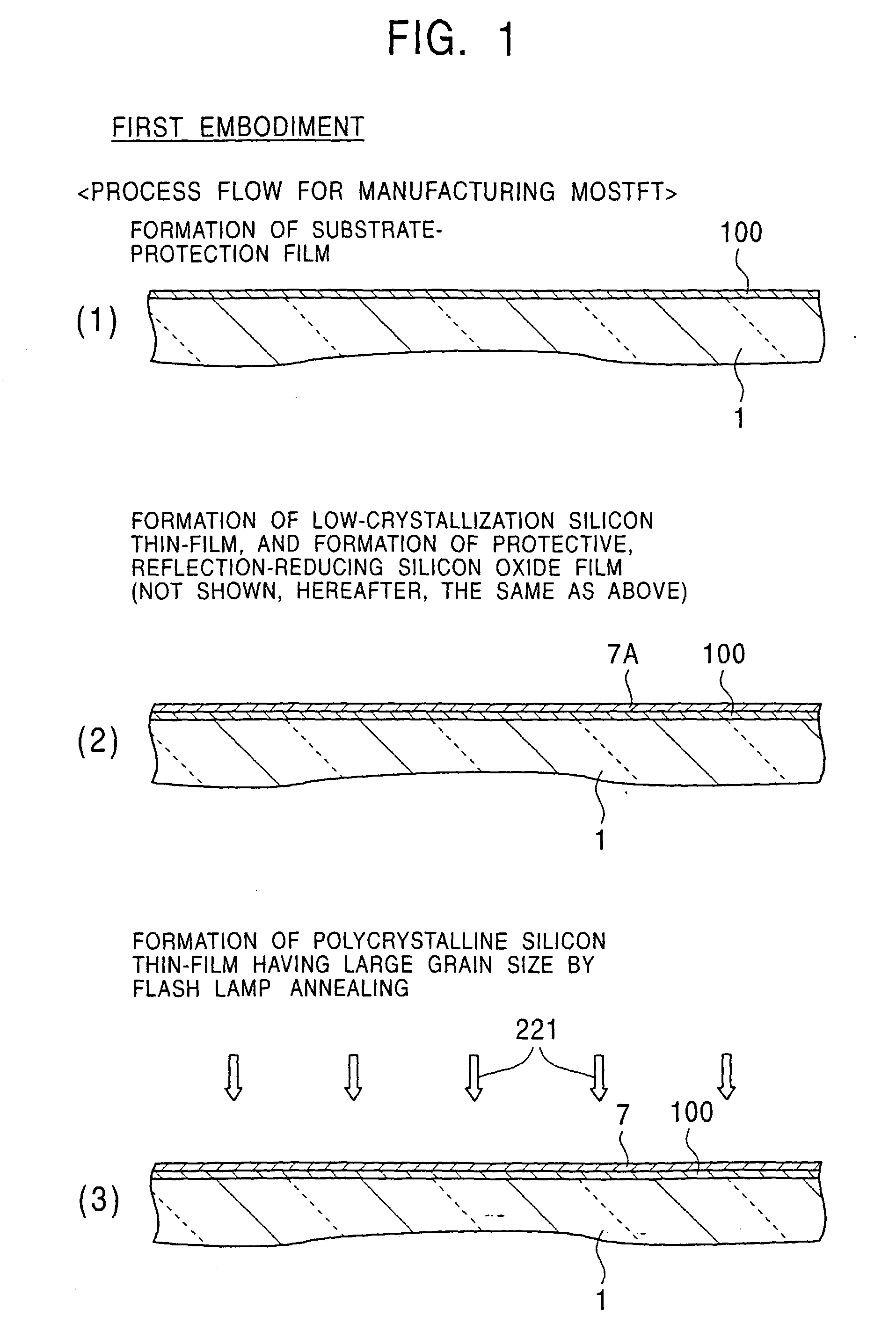

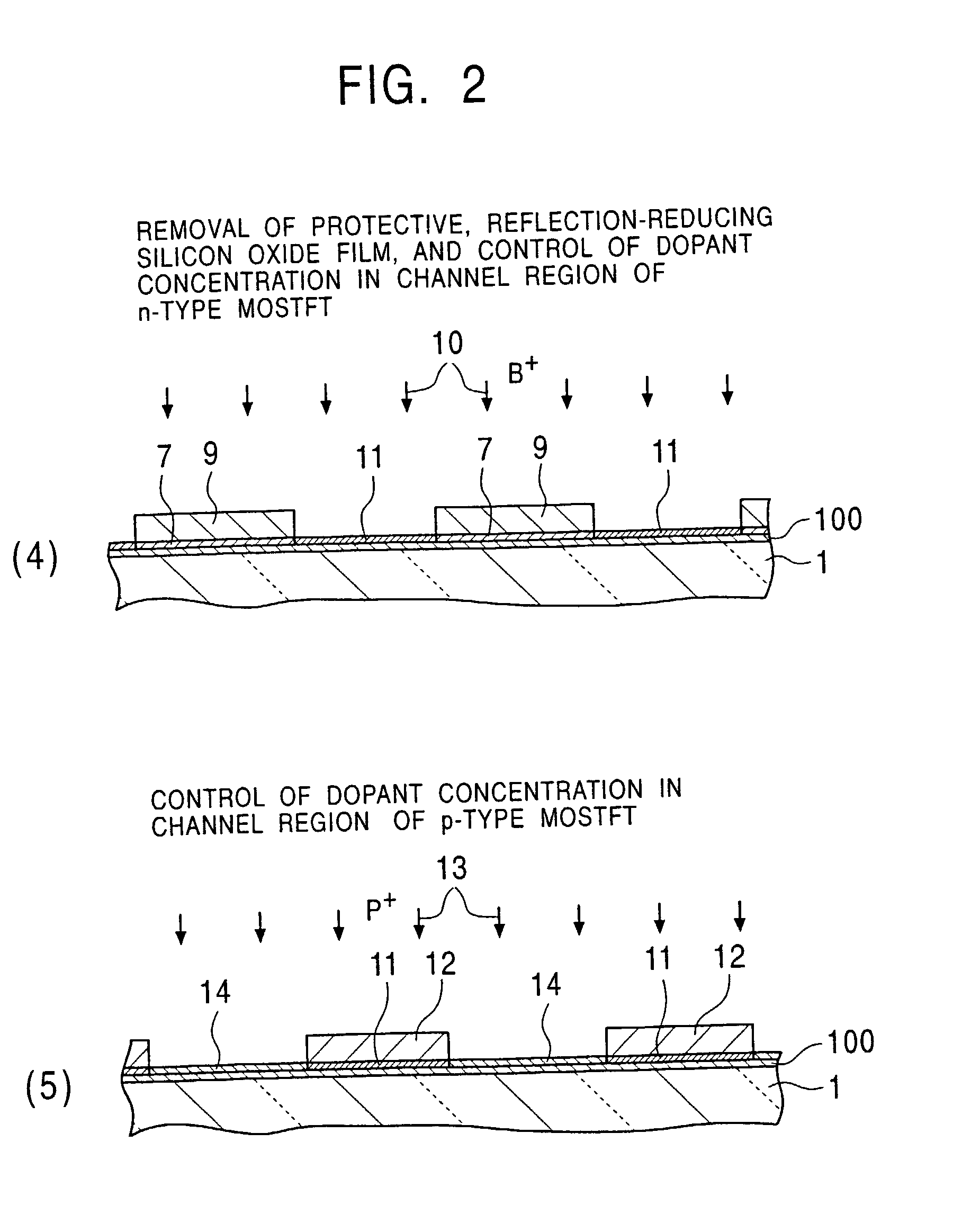

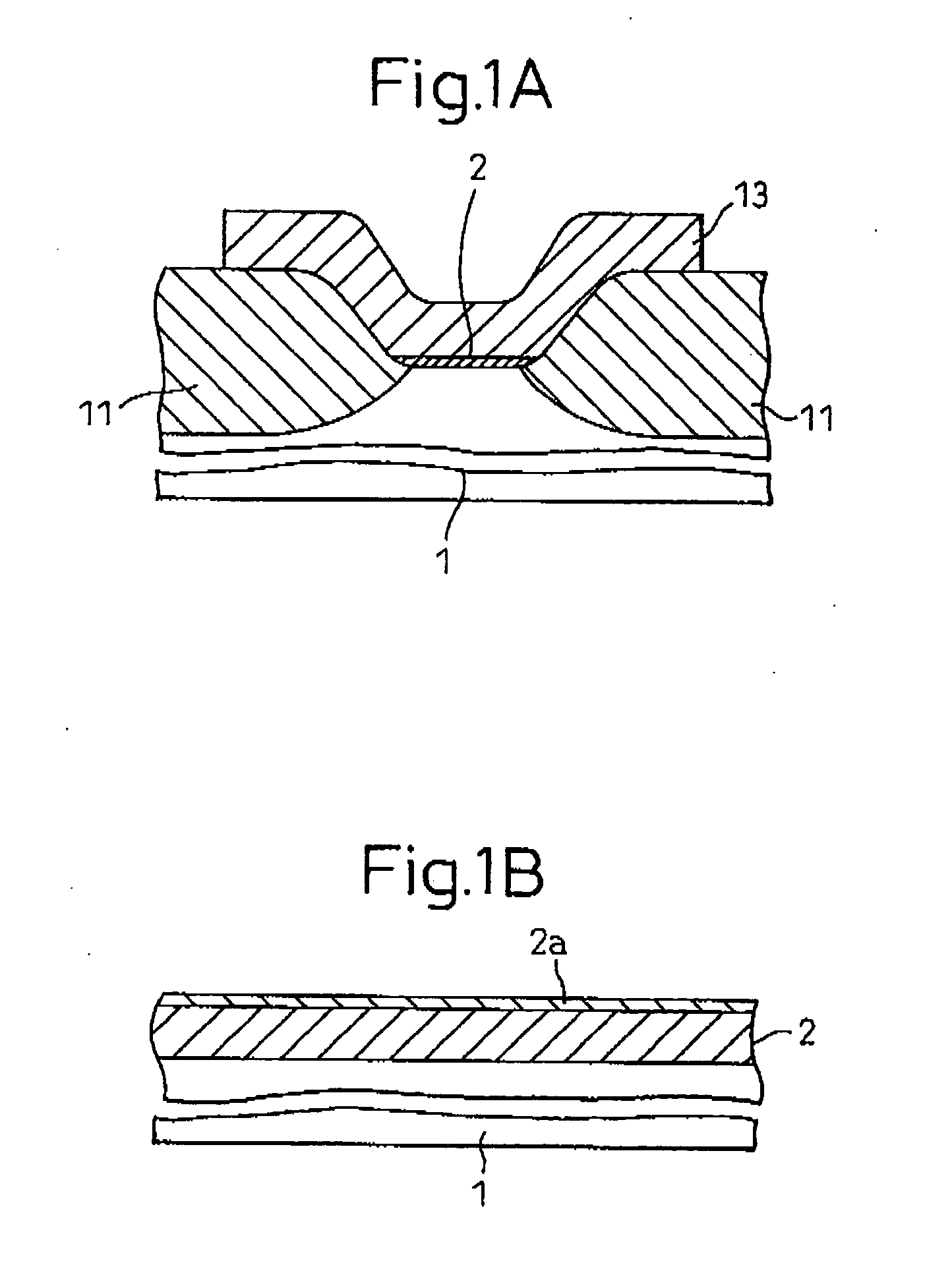

Semiconductor thin film forming method, production methods for semiconductor device and electrooptical device, devices used for these methods, and semiconductor device and electrooptical device

InactiveUS7183229B2Promote crystallizationTransistorDrying solid materials with heatSingle crystalCrystallinity

An object of the present invention is to provide a method for easily forming a polycrystalline semiconductor thin-film, such as polycrystalline silicon having high crystallinity and high quality, or a single crystalline semiconductor thin-film at inexpensive cost, the crystalline semiconductor thin-film having a large area, and to provide an apparatus for processing the method described above. In forming a polycrystalline (or single crystalline) semiconductor thin-film (7), such as a polycrystalline silicon thin-film, having high crystallinity and a large grain size on a substrate (1), or in forming a semiconductor device having the polycrystalline (or single crystalline) semiconductor thin-film (7) on the substrate (1), a method comprises forming a low-crystallization semiconductor thin-film (7A) on the substrate (1), and subsequently heating and cooling this low-crystallization semiconductor thin-film (7A) to a fusion, a semi-fusion, or a non-fusion state by flash lamp annealing to facilitate the crystallization of the low-crystallization semiconductor thin-film, whereby a polycrystalline (single crystalline) semiconductor thin-film (7) is obtained. A method for forming the semiconductor device and an apparatus for processing the methods are also disclosed.

Owner:SONY CORP

Process for Polycrystalline film silicon growth

InactiveUS6281098B1Widely distributedQuality improvementPolycrystalline material growthLiquid surface applicatorsVapor barrierProduct gas

A process for depositing polycrystalline silicon on substrates, including foreign substrates, occurs in a chamber at about atmospheric pressure, wherein a temperature gradient is formed, and both the atmospheric pressure and the temperature gradient are maintained throughout the process. Formation of a vapor barrier within the chamber that precludes exit of the constituent chemicals, which include silicon, iodine, silicon diiodide, and silicon tetraiodide. The deposition occurs beneath the vapor barrier. One embodiment of the process also includes the use of a blanketing gas that precludes the entrance of oxygen or other impurities. The process is capable of repetition without the need to reset the deposition zone conditions.

Owner:ALLIANCE FOR SUSTAINABLE ENERGY

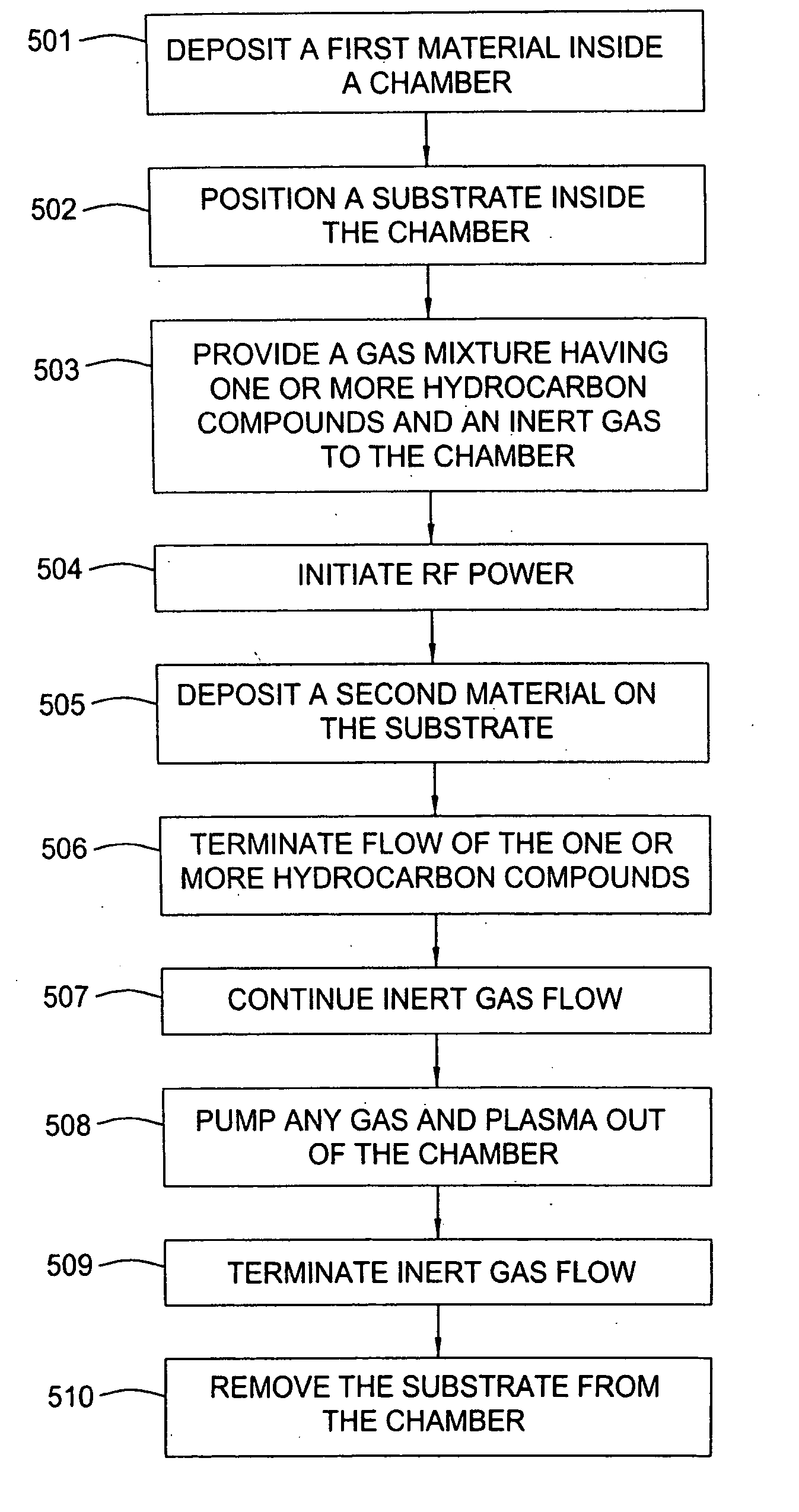

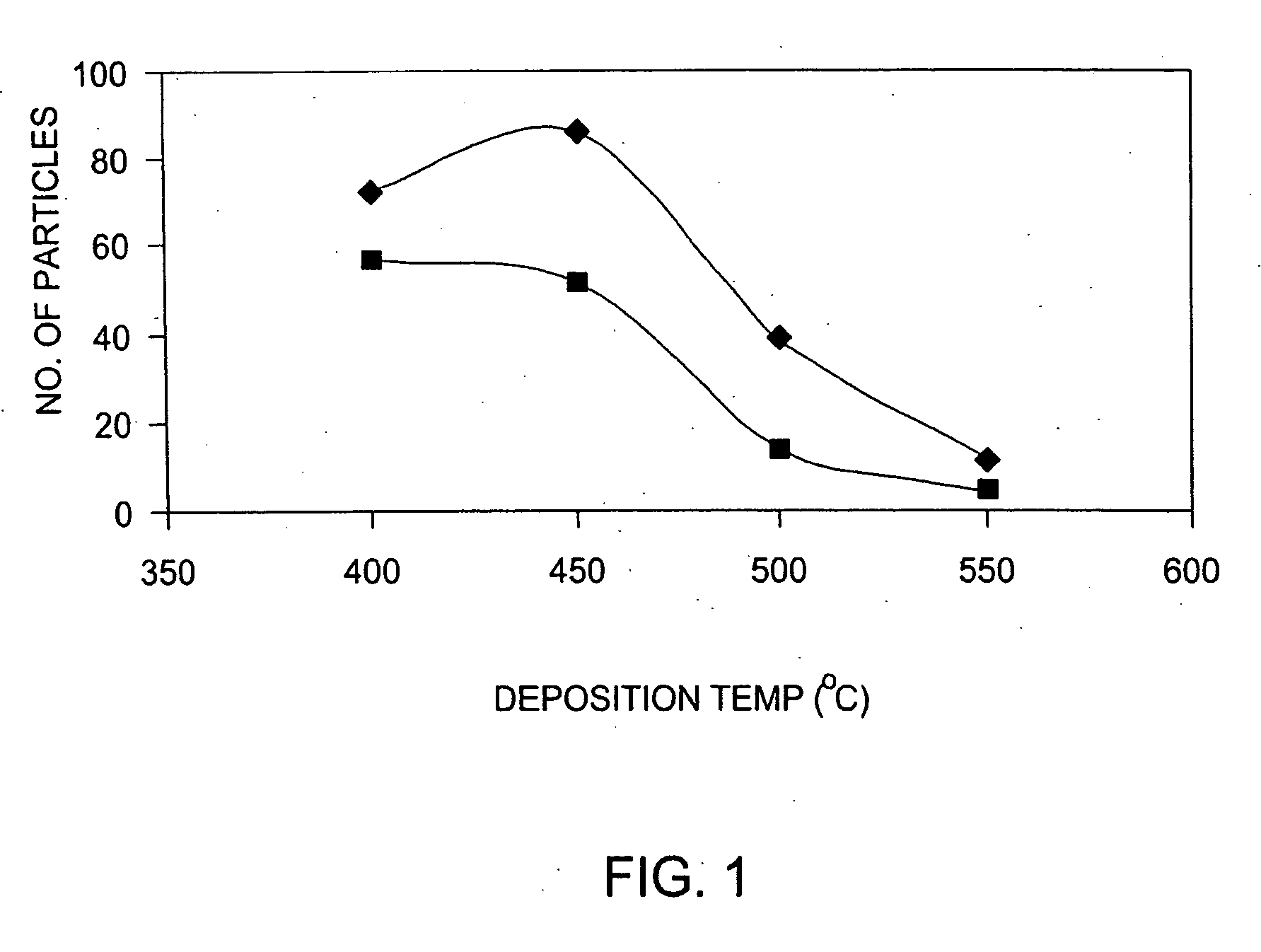

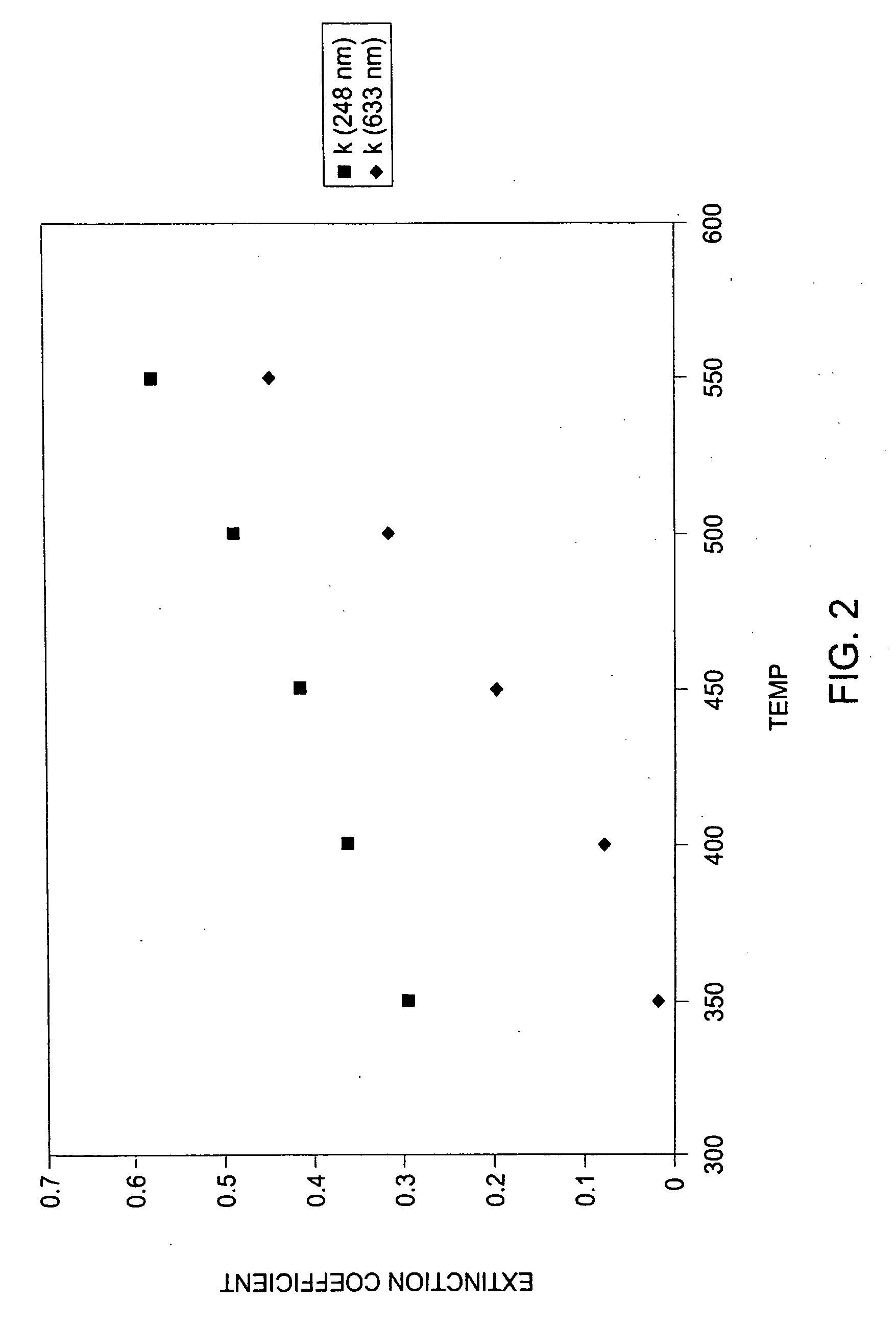

Methods for the reduction and elimination of particulate contamination with CVD of amorphous carbon

InactiveUS20060014397A1Minimal defect formationReduce particle pollutionSemiconductor/solid-state device manufacturingSpecial surfacesVariable thicknessMicroparticle

A method is provided for forming an amorphous carbon layer, deposited on a dielectric material such as oxide, nitride, silicon carbide, carbon doped oxide, etc., or a metal layer such as tungsten, aluminum or poly-silicon. The method includes the use of chamber seasoning, variable thickness of seasoning film, wider spacing, variable process gas flows, post-deposition purge with inert gas, and post-deposition plasma purge, among others, to make the deposition of an amorphous carbon film at low deposition temperatures possible without any defects or particle contamination.

Owner:APPLIED MATERIALS INC +1

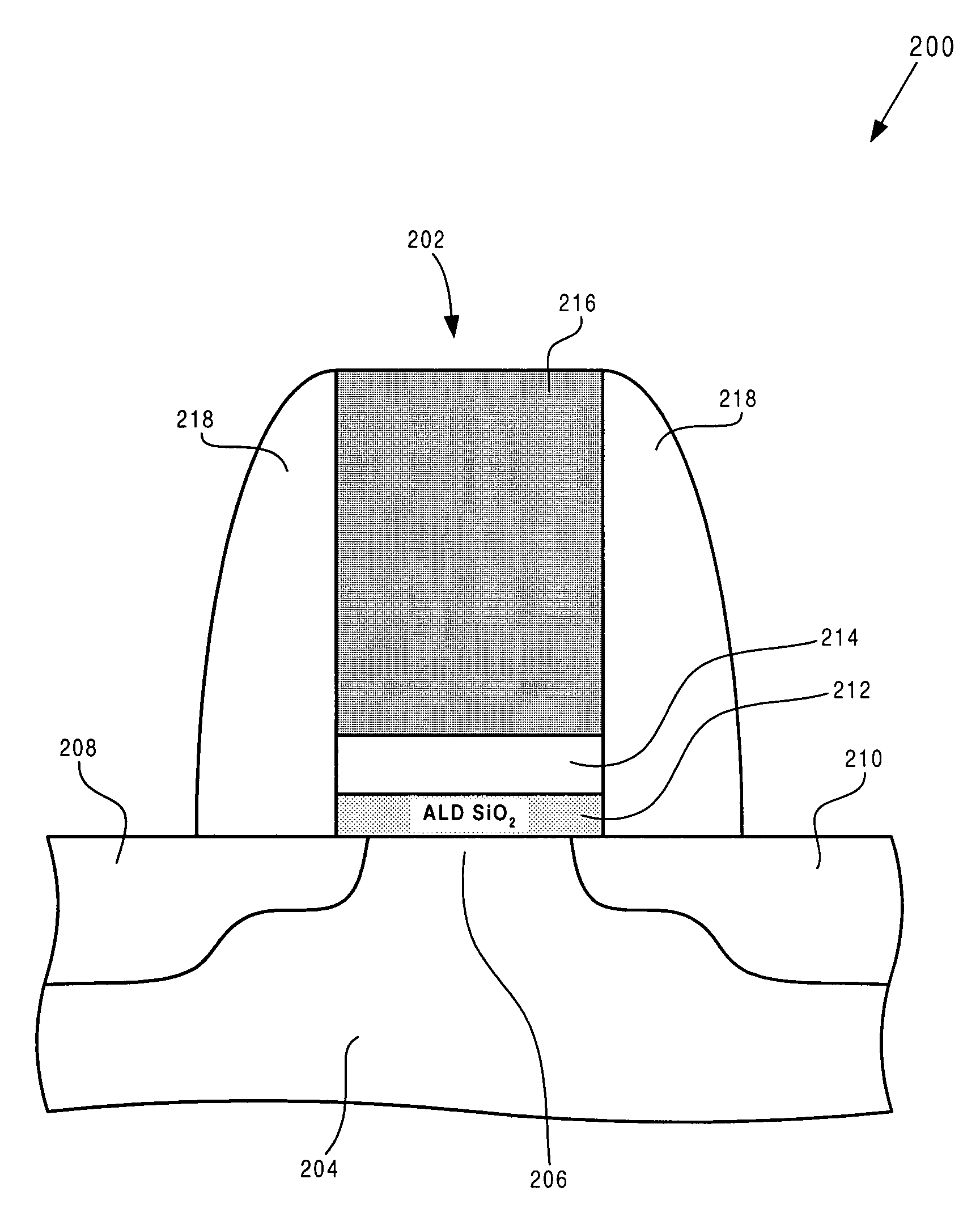

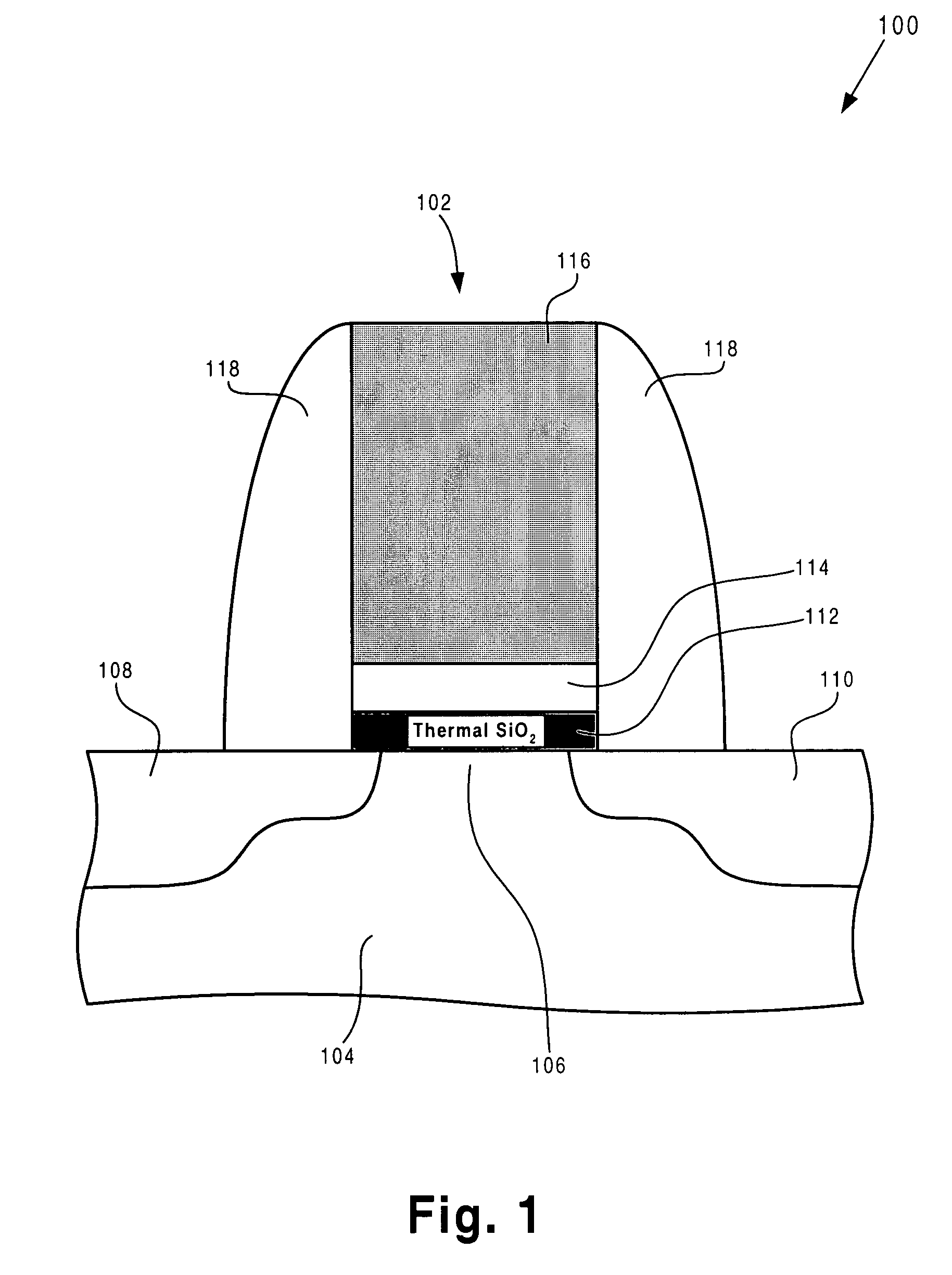

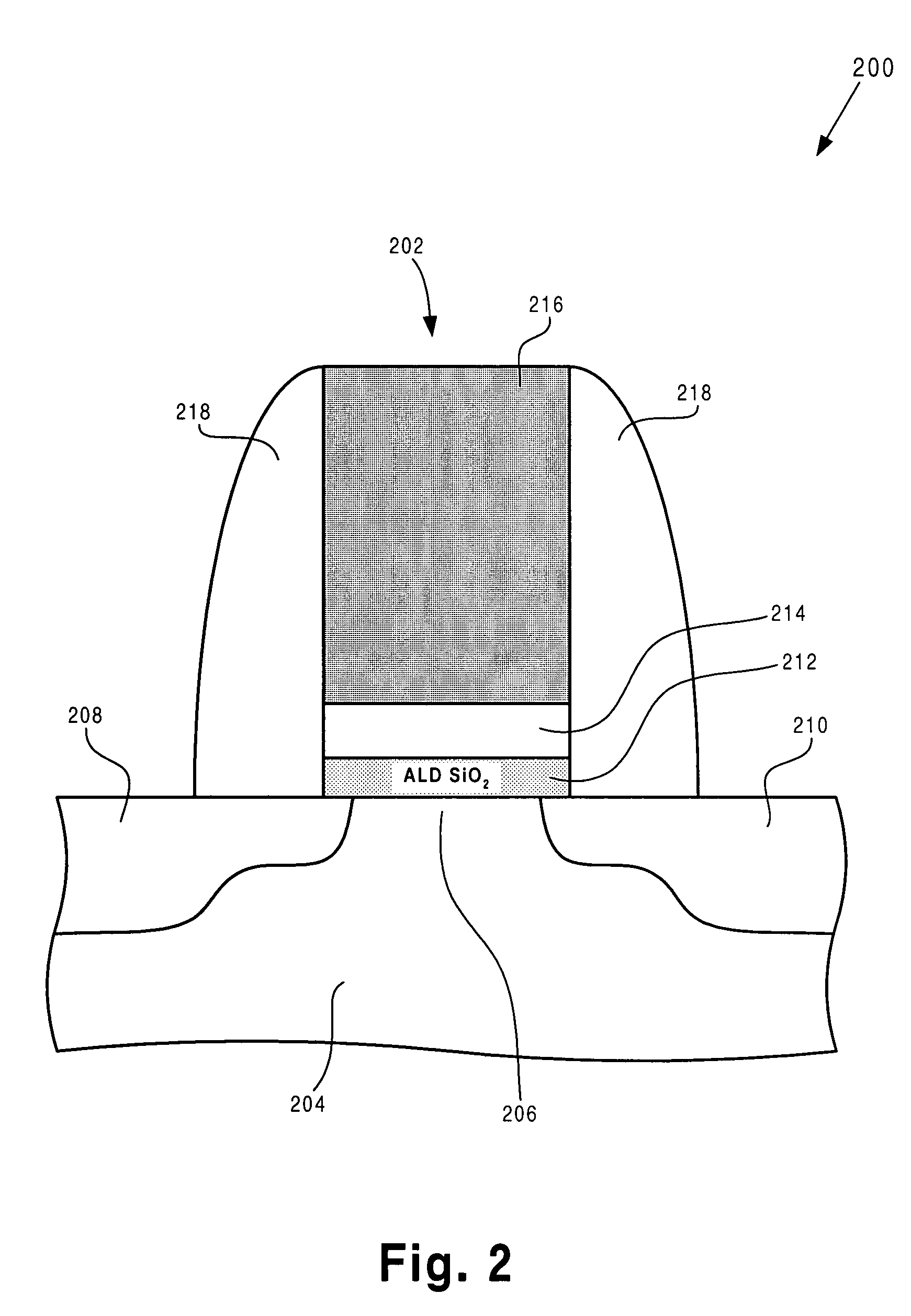

Method for forming a thin, high quality buffer layer in a field effect transistor and related structure

ActiveUS7071051B1Readily apparentSemiconductor/solid-state device manufacturingSemiconductor devicesOrganic field-effect transistorOptoelectronics

According to one exemplary embodiment, a method for forming a field-effect transistor on a substrate comprises a step of forming a buffer layer on the substrate, where the buffer layer comprises ALD silicon dioxide. The buffer layer can be formed by utilizing a silicon tetrachloride precursor in an atomic layer deposition process, for example. The buffer layer comprises substantially no pin-hole defects and may have a thickness, for example, that is less than approximately 5.0 Angstroms. The method further comprises forming a high-k dielectric layer over the buffer layer. The high-k dielectric layer may be, for example, hafnium oxide, zirconium oxide, or aluminum oxide. According to this exemplary embodiment, the method further comprises forming a gate electrode layer over the high-k dielectric layer. The gate electrode layer may be polycrystalline silicon, for example.

Owner:GLOBALFOUNDRIES US INC

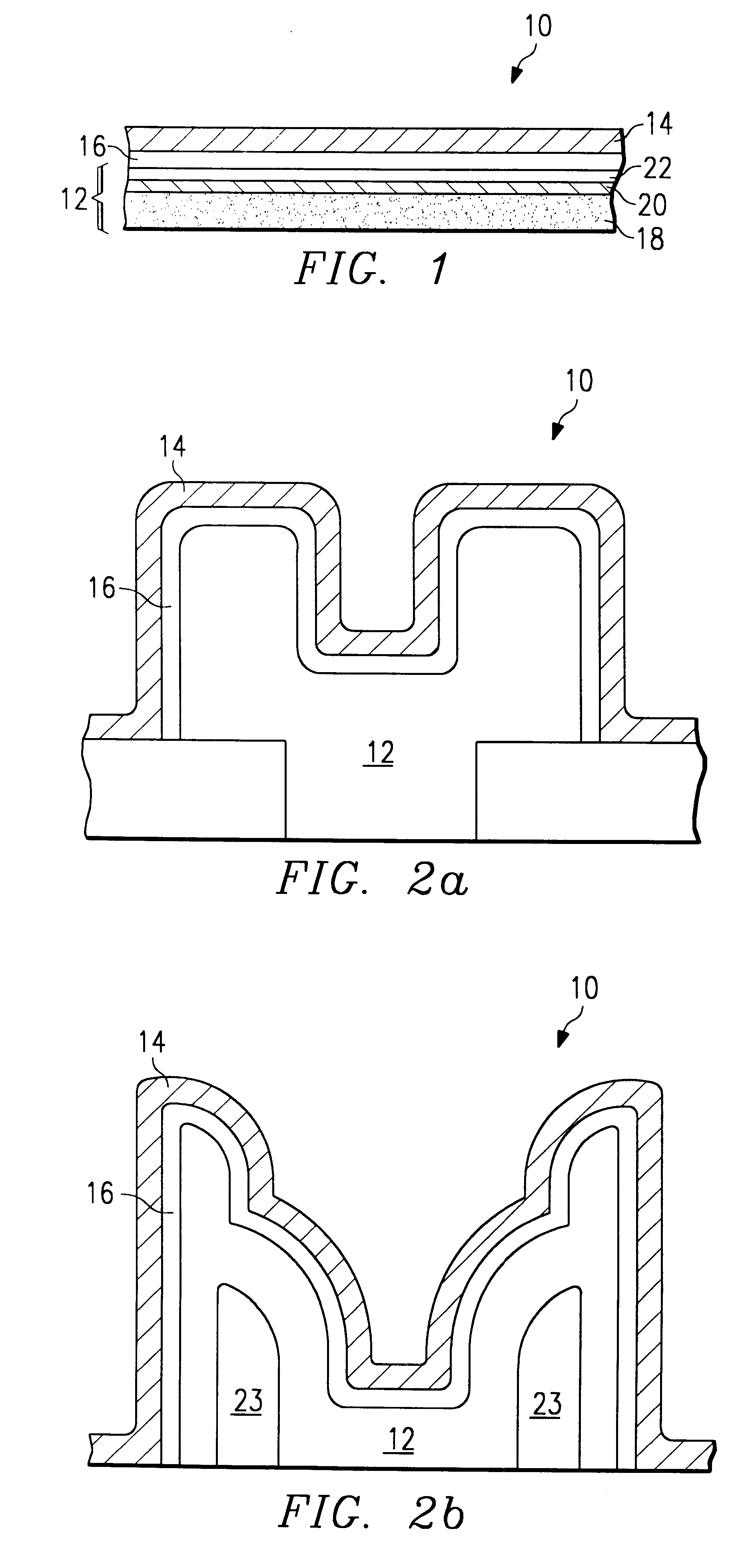

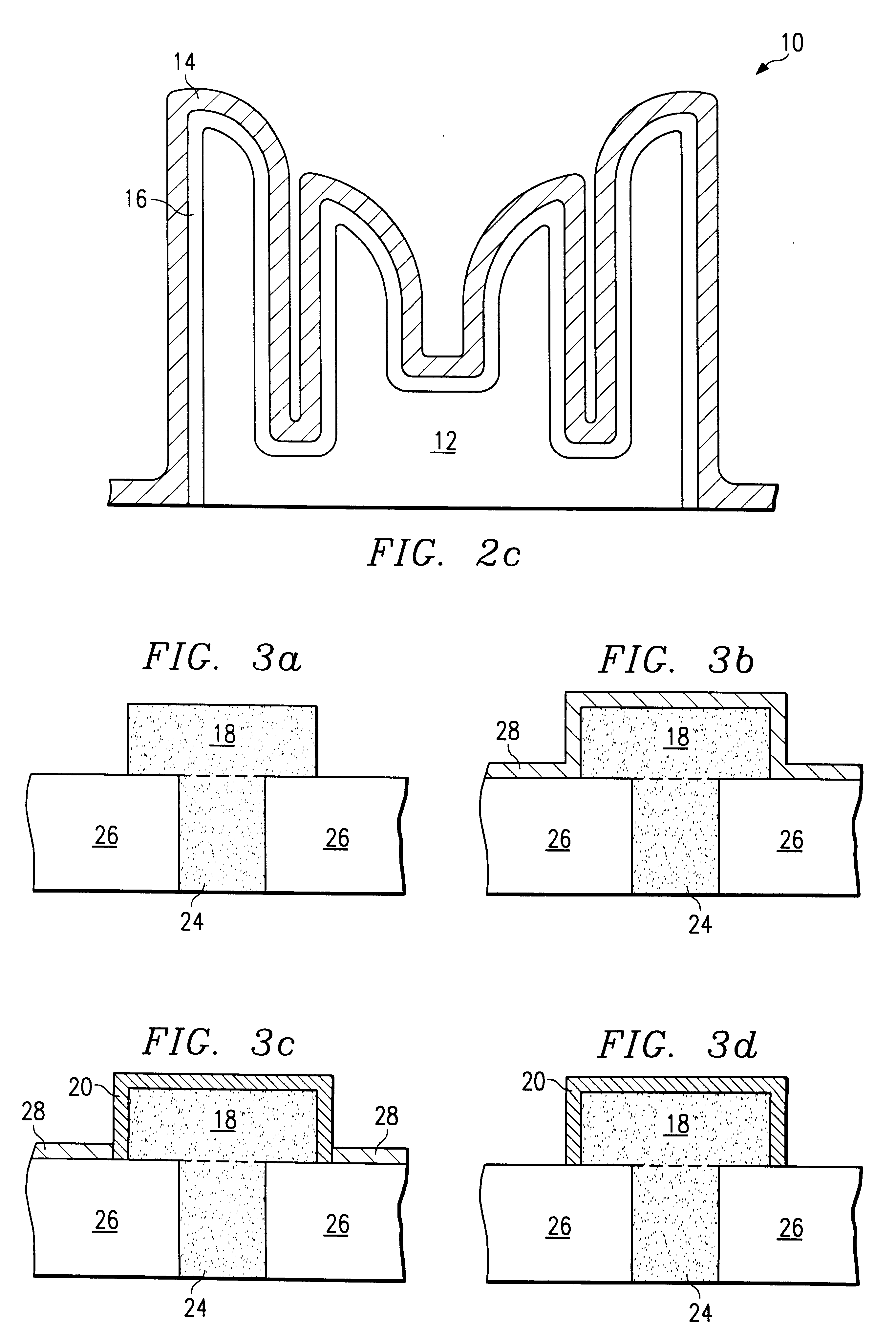

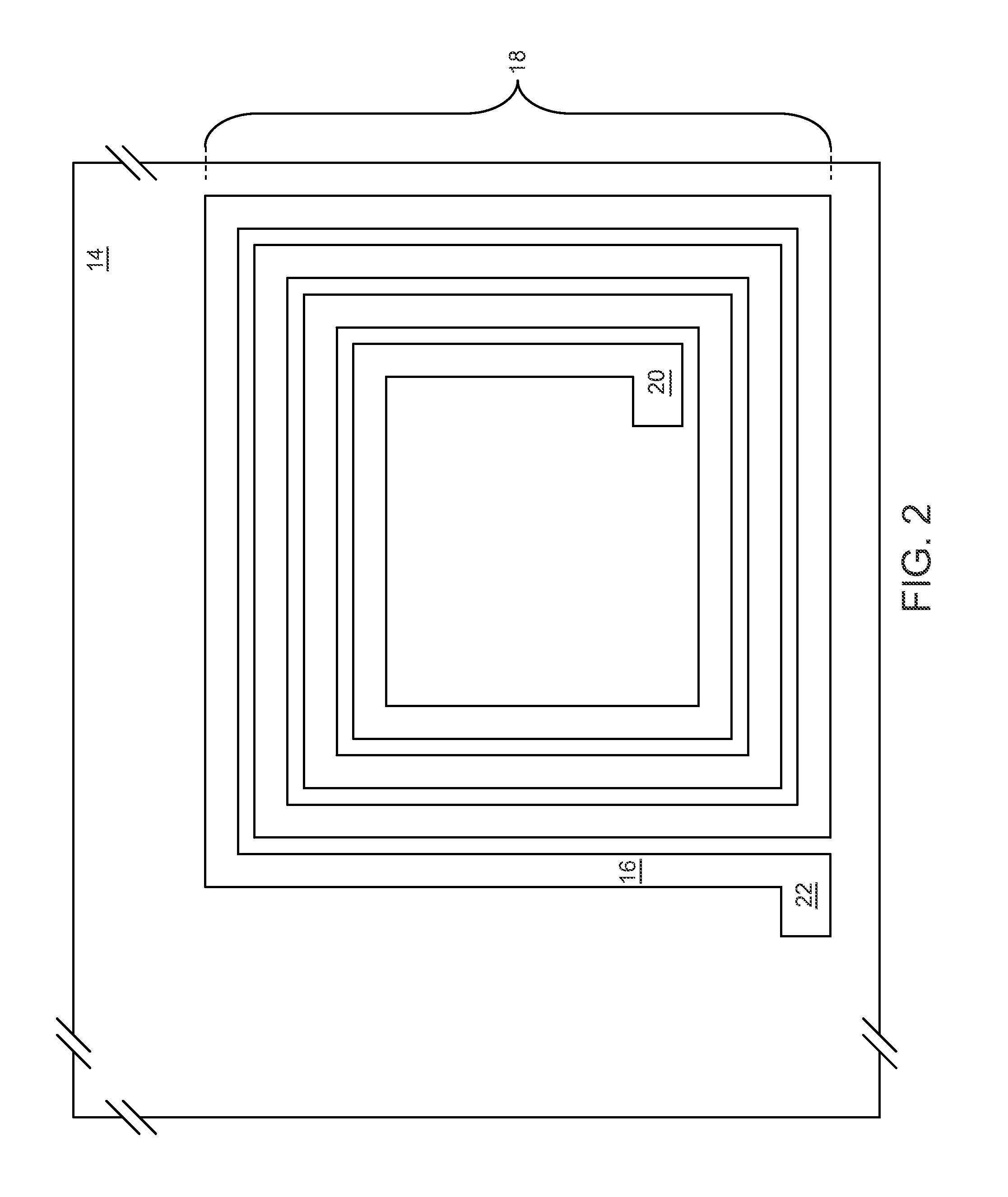

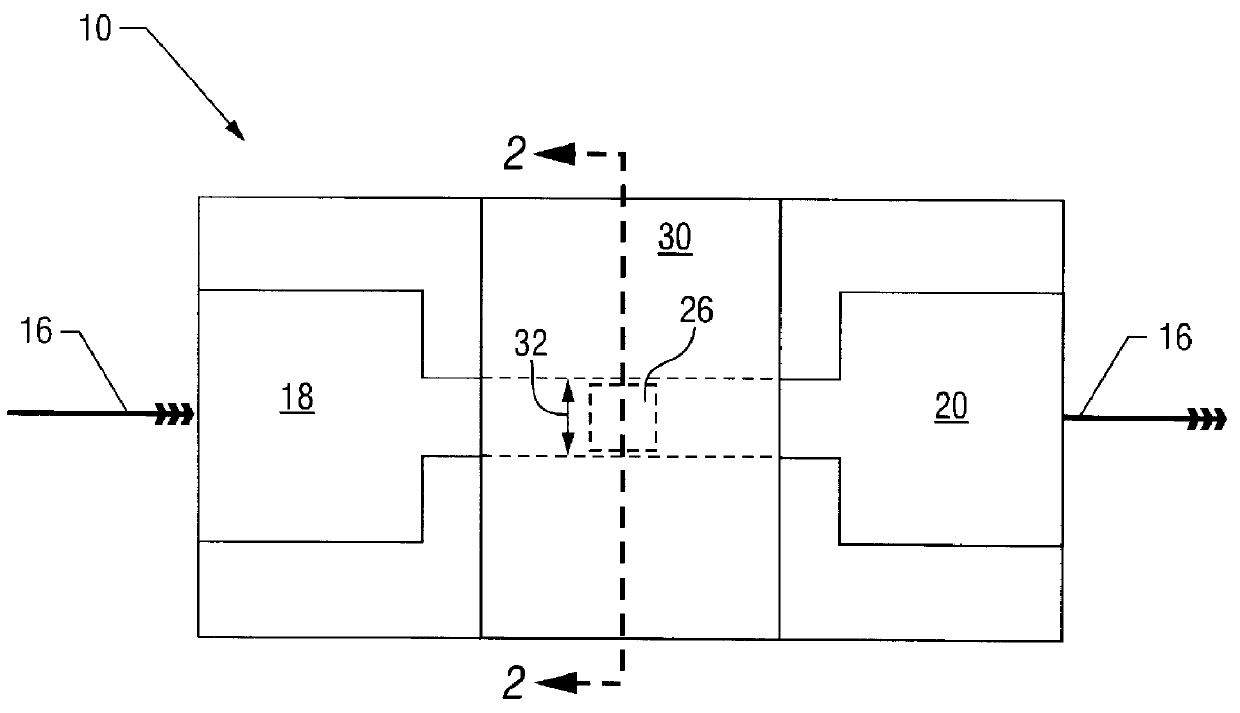

Integrated circuit capacitor

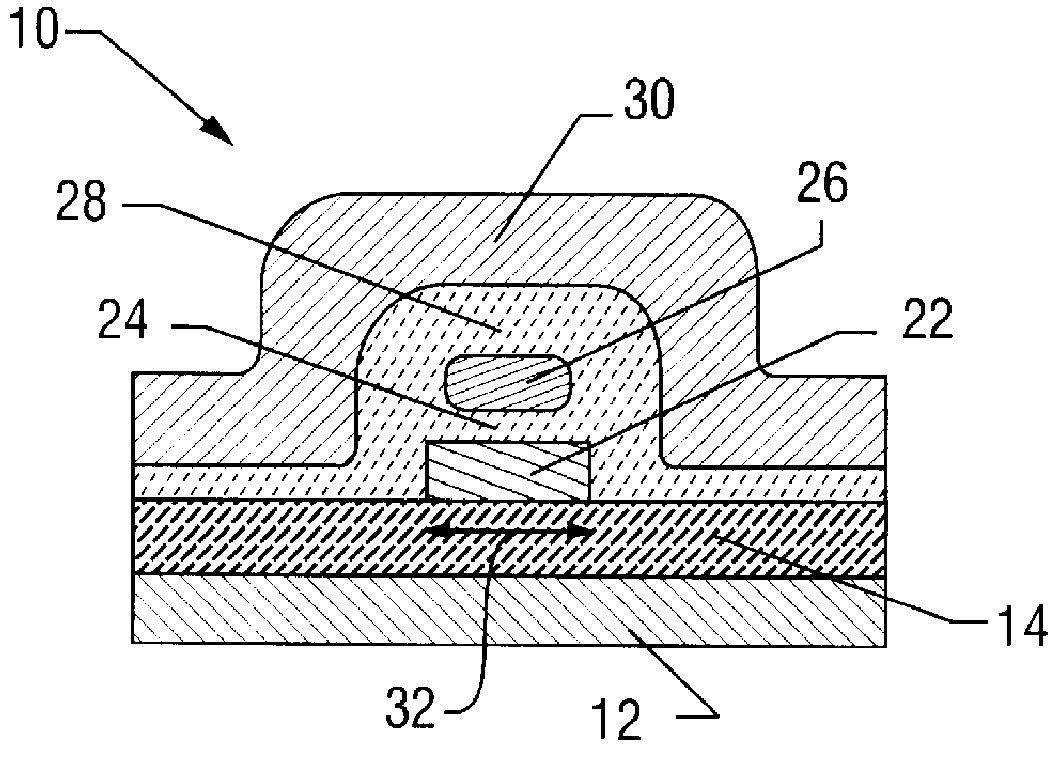

The present invention discloses a novel integrated circuit capacitor and a method of forming such a capacitor. The capacitor formation begins with a base electrode 18 adjacent an insulating region 26. This base electrode 18 can comprise either polysilicon or a metal. A layer 28 of a first material, such as a siliciding metal, is formed over the base electrode 18 as well as the adjacent insulating region. A self-aligned capacitor electrode 12 can then be formed by reacting the first material 28 with the base electrode 18 and removing unreacted portions of the first material 28 from the insulating region 26. The capacitor is then completed by forming a dielectric layer 16 over the self-aligned capacitor electrode 12 and a second capacitor electrode 14 over the dielectric layer 16.

Owner:TEXAS INSTR INC

Memory cell incorporating a chalcogenide element

A memory cell incorporating a chalcogenide element and a method of making same is disclosed. In the method, a doped silicon substrate is provided with two or more polysilicon plugs to form an array of diode memory cells. A layer of silicon nitride is disposed over the plugs. Using a poly-spacer process, small pores are formed in the silicon nitride to expose a portion of the polysilicon plugs. A chalcogenide material is disposed in the pores by depositing a layer of chalcogenide material on the silicon nitride layer and planarizing the chalcogenide layer to the silicon nitride layer using CMP. A layer of TiN is next deposited over the plugs, followed by a metallization layer. The TiN and metallization layers are then masked and etched to define memory cell areas.

Owner:ROUND ROCK RES LLC

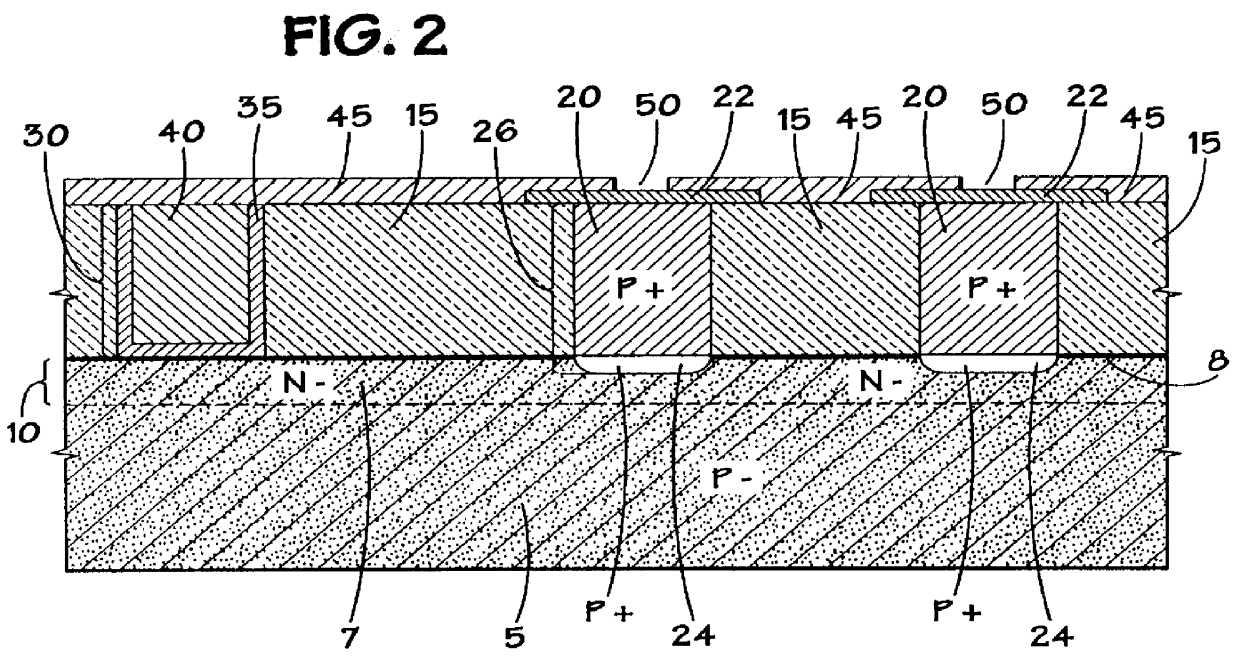

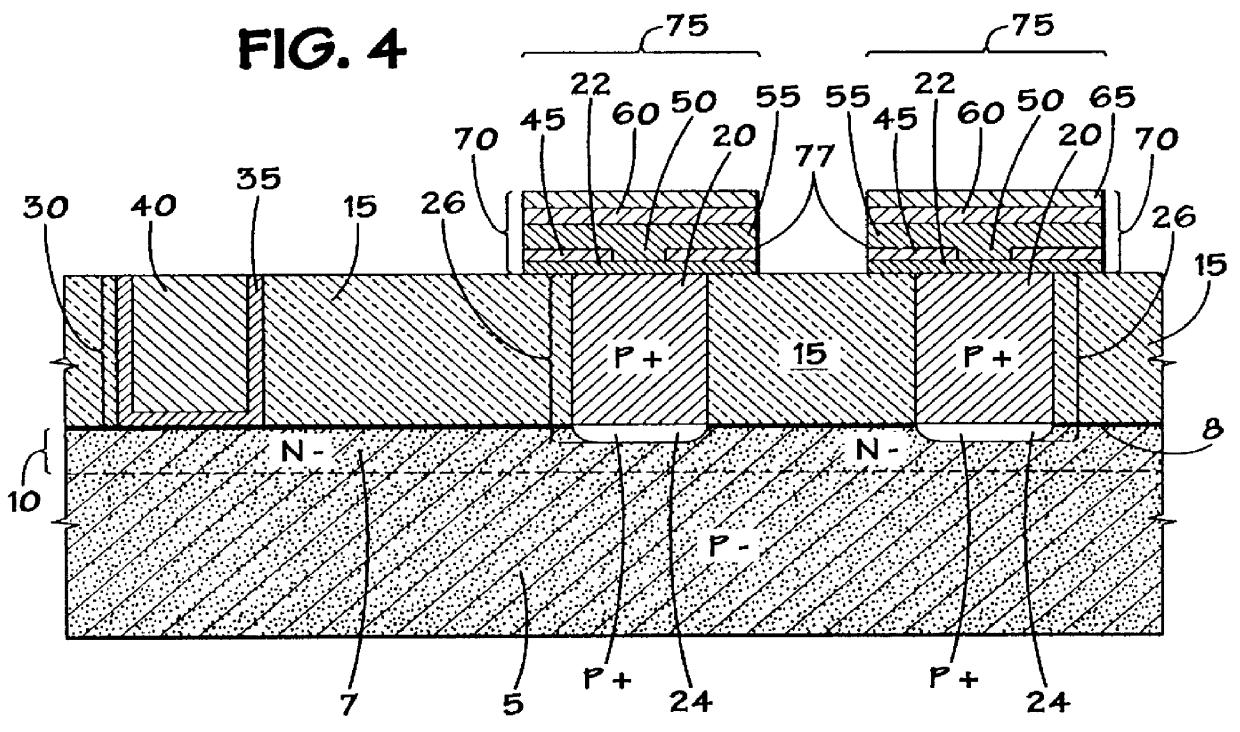

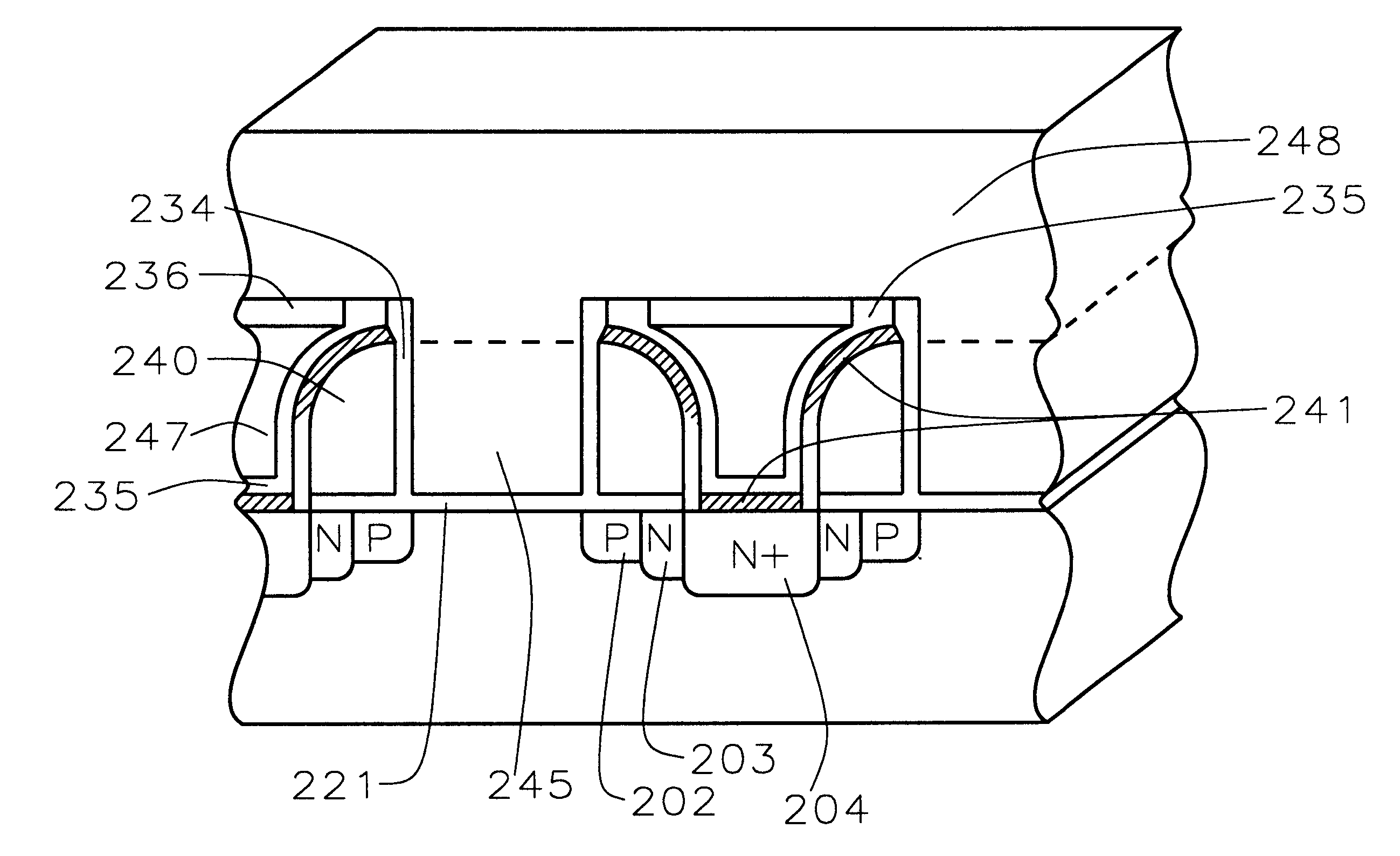

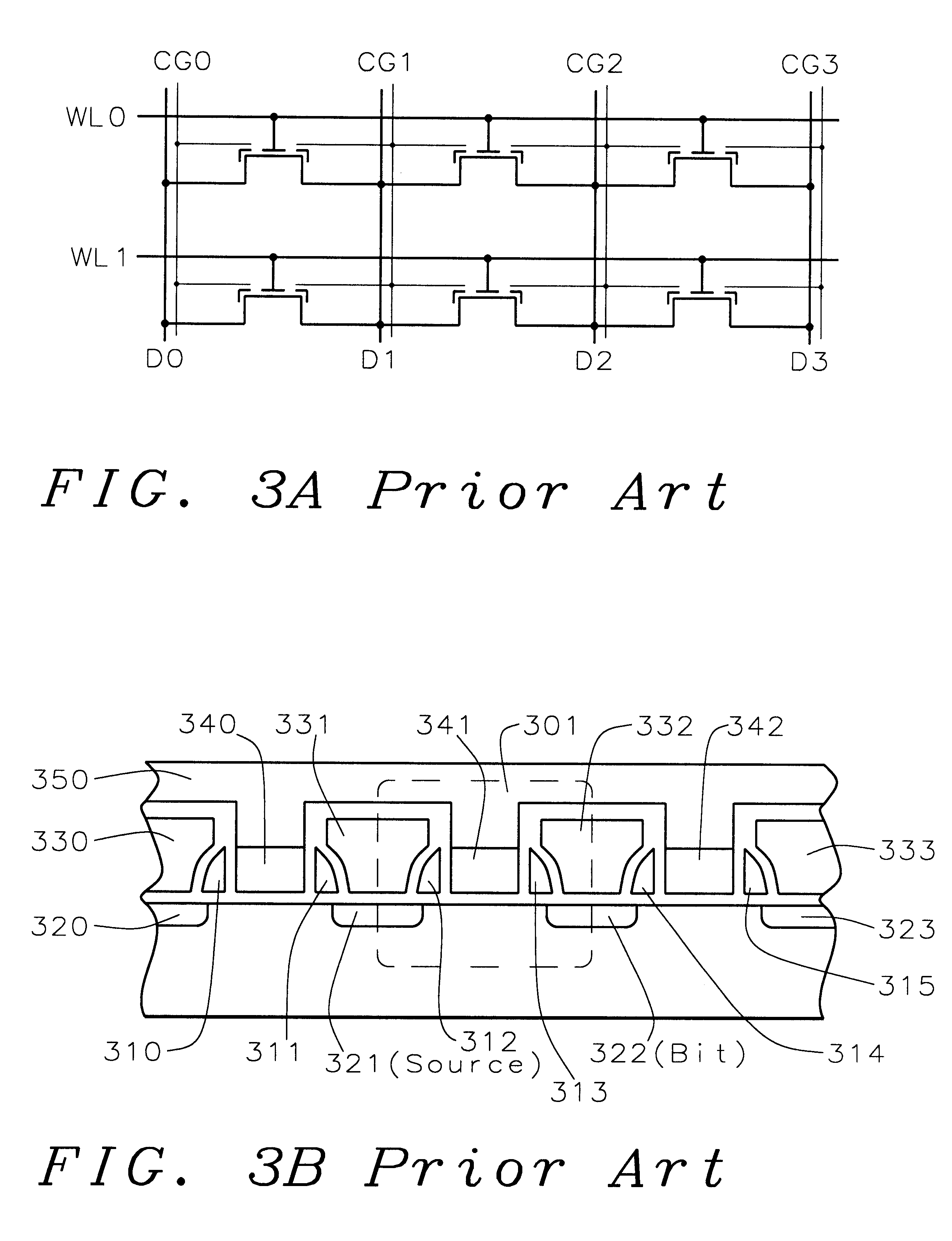

Process for making and programming and operating a dual-bit multi-level ballistic MONOS memory

A fast low voltage ballistic program, ultra-short channel, ultra-high density, dual-bit multi-level flash memory is described with a two or three polysilicon split gate side wall process. The structure and operation of this invention is enabled by a twin MONOS cell structure having an ultra-short control gate channel of less than 40nm, with ballistic injection which provides high electron injection efficiency and very fast program at low program voltages of 3~5V. The cell structure is realized by (i) placing side wall control gates over a composite of Oxide-Nitride-Oxide (ONO) on both sides of the word gate, and (ii) forming the control gates and bit diffusion by self-alignment and sharing the control gates and bit diffusions between memory cells for high density. Key elements used in this process are: 1) Disposable side wall process to fabricate the ultra short channel and the side wall control gate with or without a step structure, and 2) Self-aligned definition of the control gate over the storage nitride and the bit line diffusion, which also runs in the same direction as the control gate. The features of fast program, low voltage, ultra-high density, dual-bit, multi-level MONOS NVRAM of the present invention include: 1) Electron memory storage in nitride regions within an ONO layer underlying the control gates, 2) high density dual-bit cell in which there are two nitride memory storage elements per cell, 3) high density dual-bit cell can store multi-levels in each of the nitride regions, 4) low current program controlled by the word gate and control gate, 5) fast, low voltage program by ballistic injection utilizing the controllable ultra-short channel MONOS, and 6) side wall control poly gates to program and read multi-levels while masking out memory storage state effects of the unselected adjacent nitride regions and memory cells. The ballistic MONOS memory cell is arranged in the following array: each memory cell contains two nitride regions for one word gate, and ½ a source diffusion and ½ a bit diffusion. Control gates can be defined separately or shared together over the same diffusion. Diffusions are shared between cells and run in parallel to the side wall control gates, and perpendicular to the word line.

Owner:HALO LSI INC

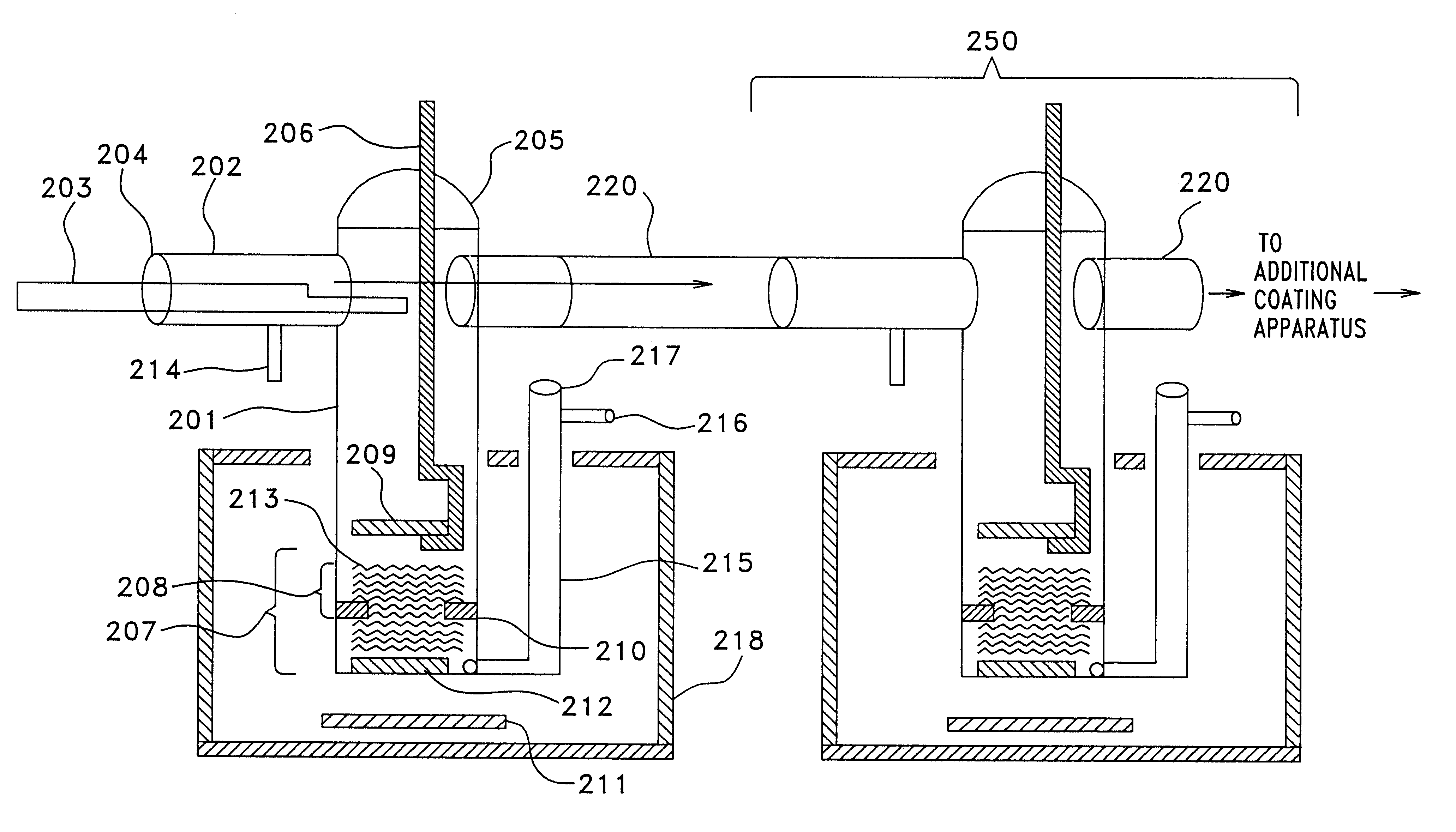

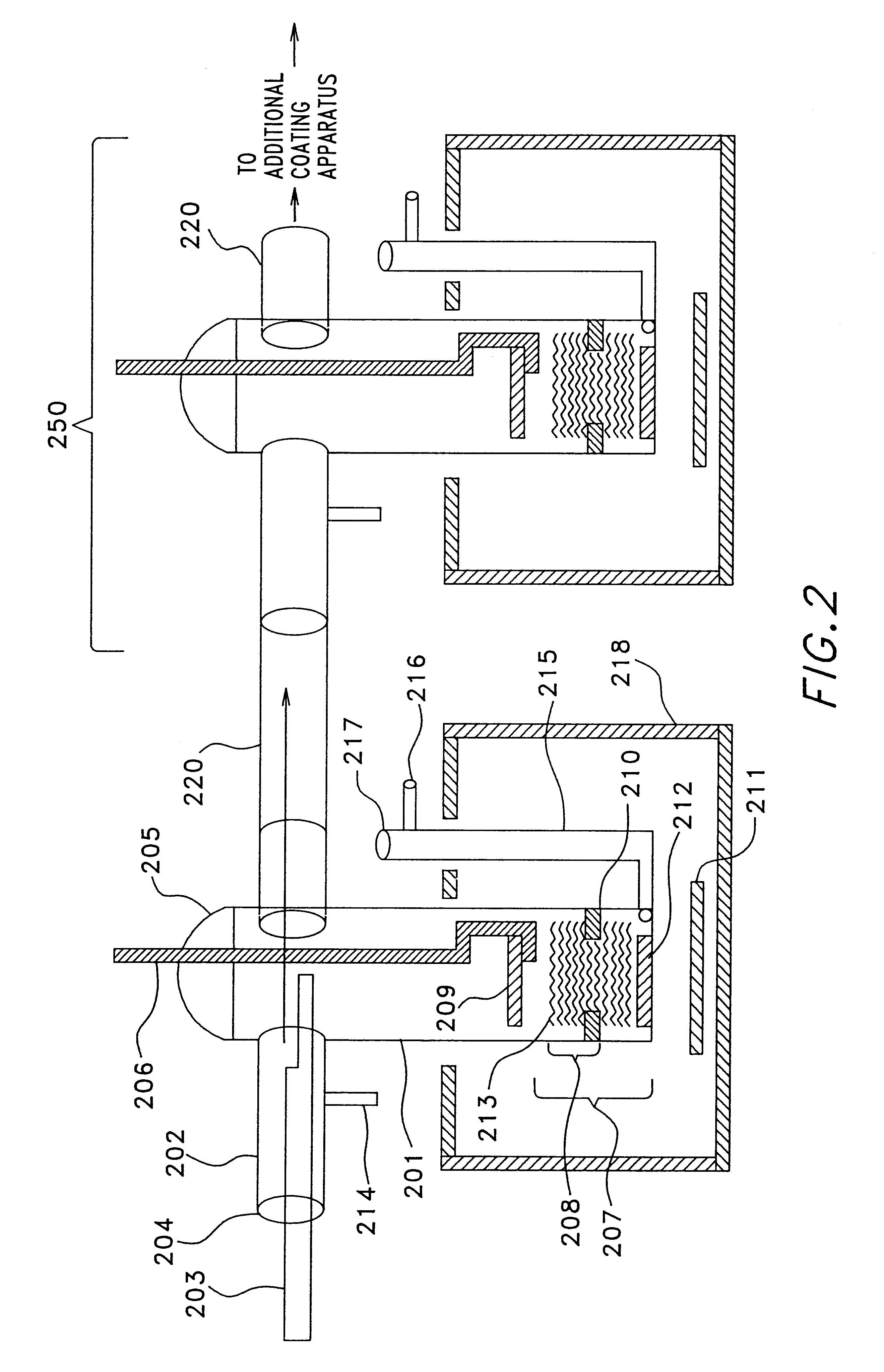

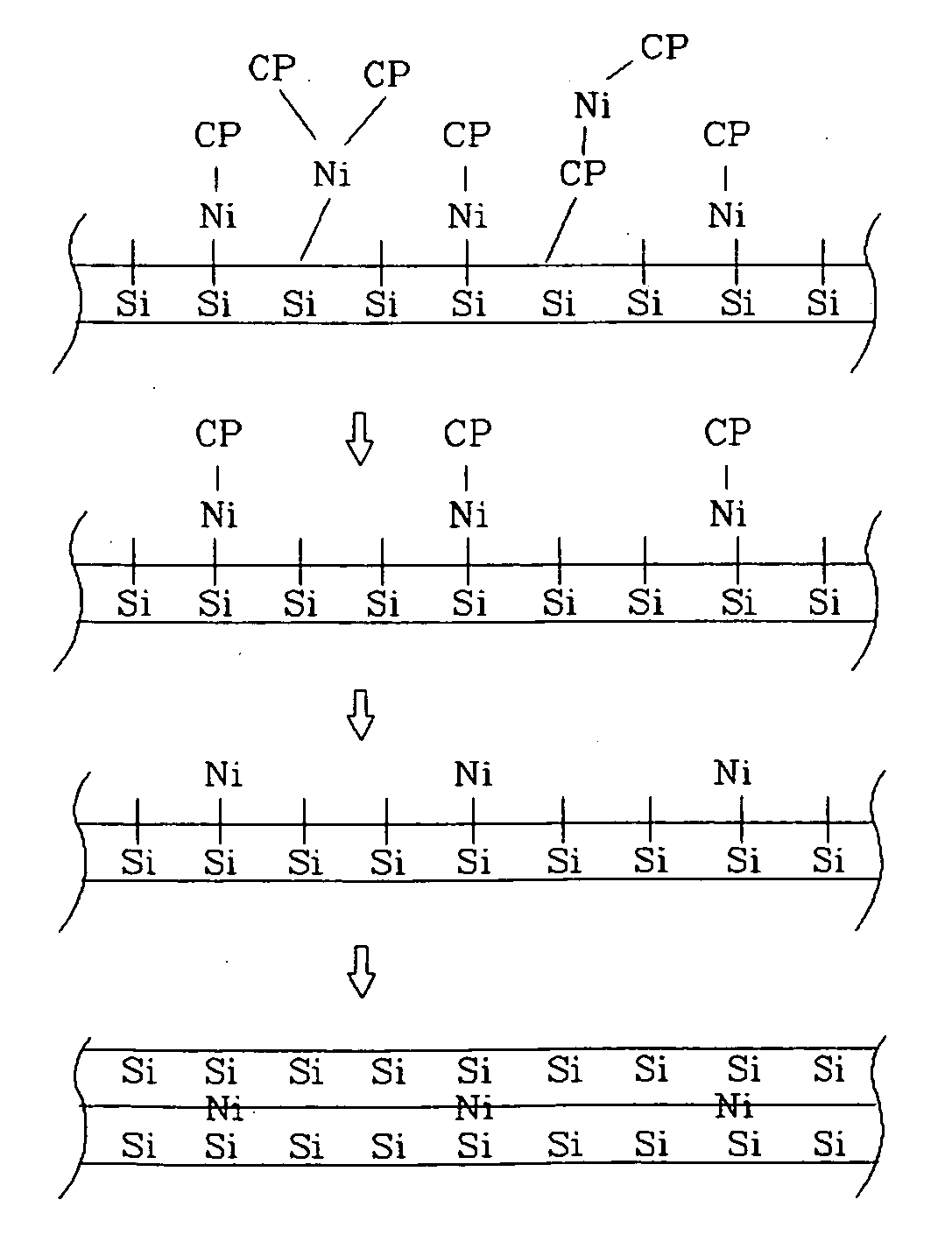

Apparatus and method for forming polycrystalline silicon thin film

ActiveUS20070054499A1Increase the rate of crystallizationDecrease in crystallization temperatureAfter-treatment apparatusSemiconductor/solid-state device manufacturingGas phaseAmorphous silicon

Apparatus and method for forming a polycrystalline silicon thin film by converting an amorphous silicon thin film into the polycrystalline silicon thin film using a metal are provided. The method includes: a metal nucleus adsorbing step of introducing a vapor phase metal compound into a process space where the glass substrate having the amorphous silicon formed thereon is disposed, to adsorb a metal nucleus contained in the metal compound into the amorphous silicon layer; a metal nucleus distribution region-forming step of forming a community region including a plurality of silicon particles every metal nucleus in a plane boundary region occupied by the metal compound by a self-limited mechanism due to the adsorption of the metal nucleus; and an excess gas removing step of purging and removing an excess gas which is not adsorbed in the metal nucleus distribution region-forming step.

Owner:WONIK IPS CO LTD

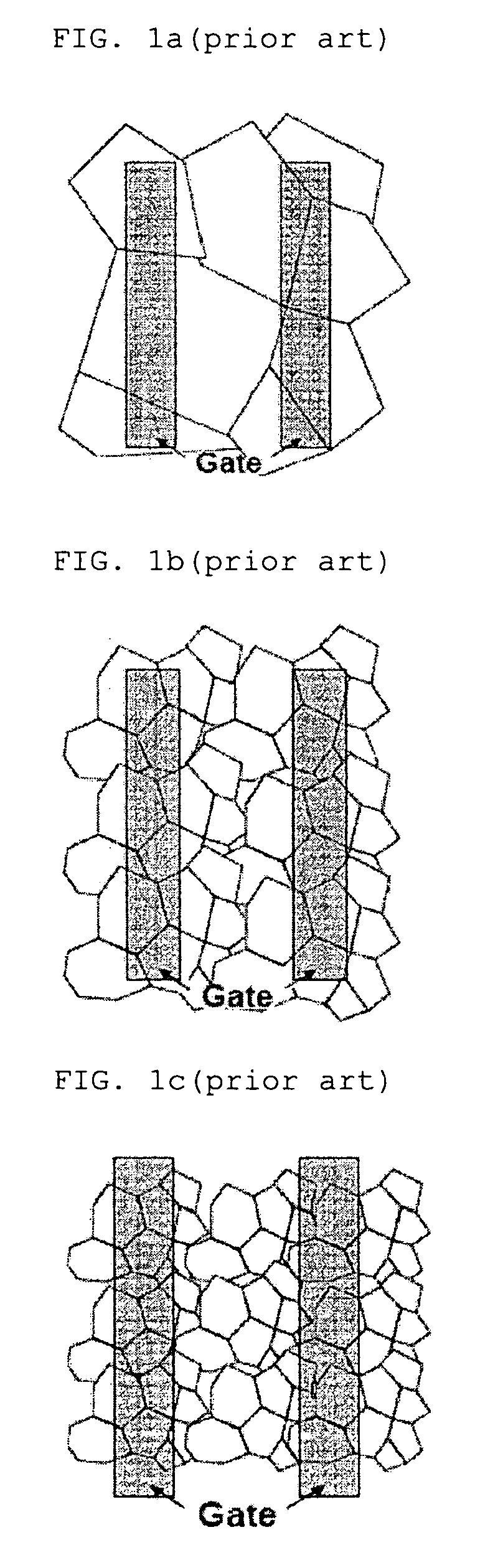

Method of forming polycrystalline silicon layer and atomic layer deposition apparatus used for the same

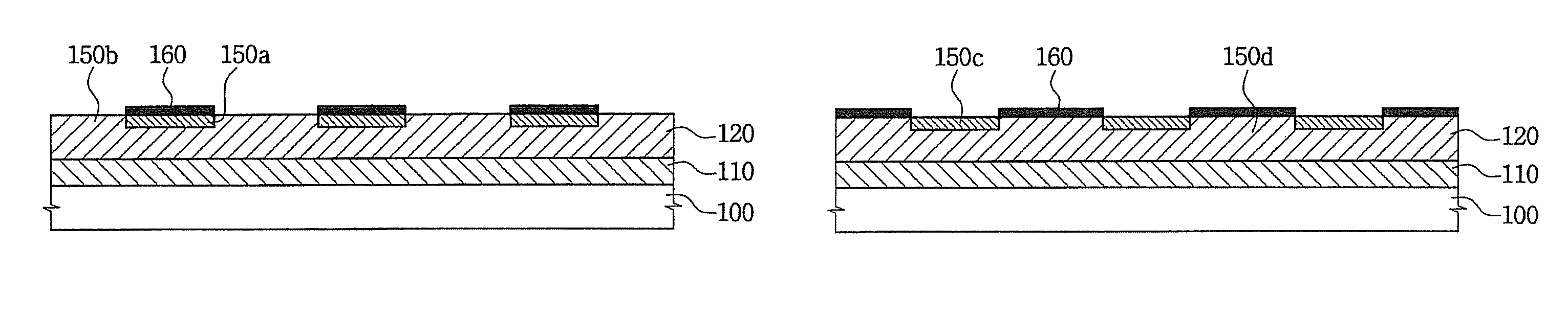

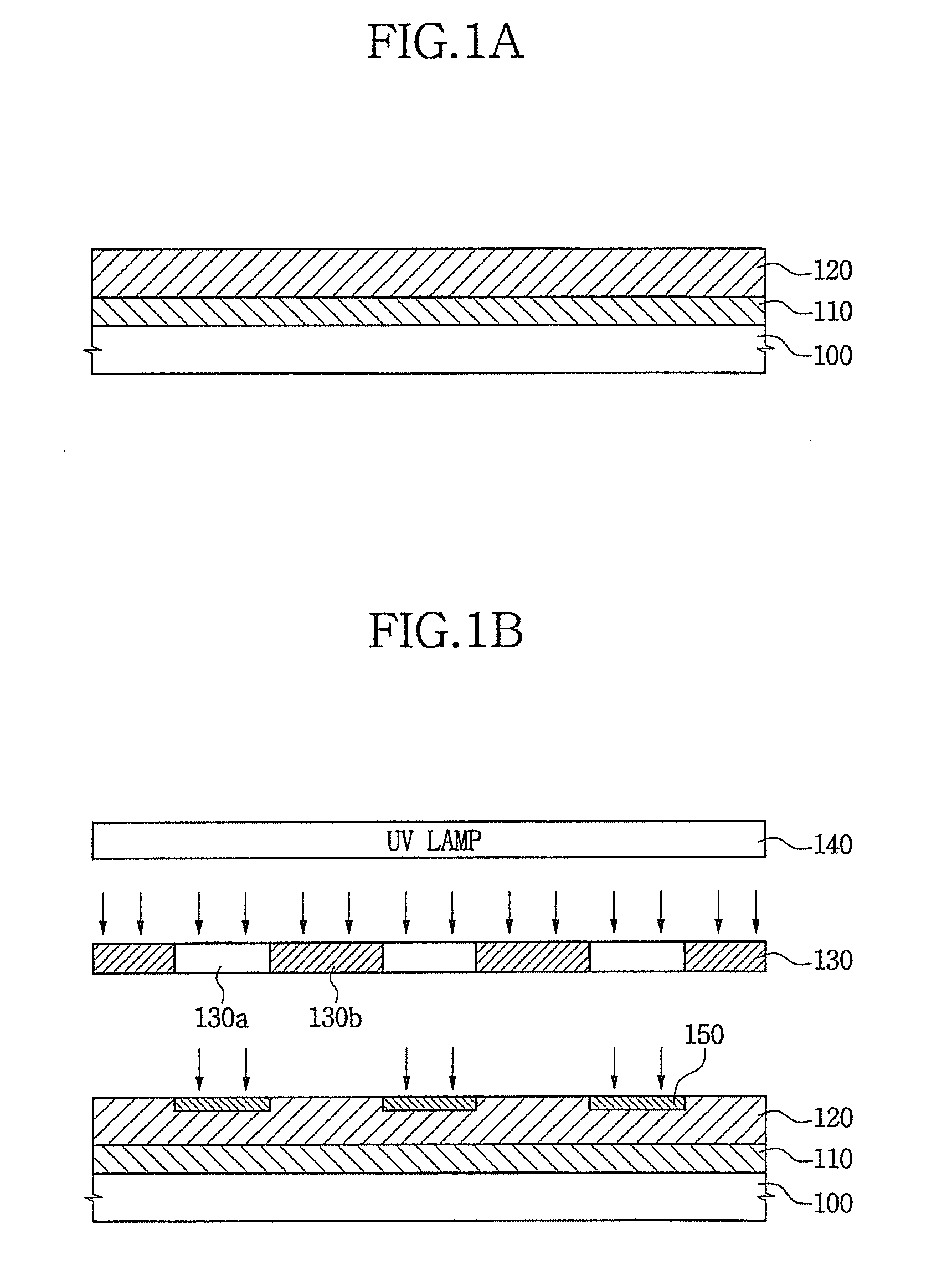

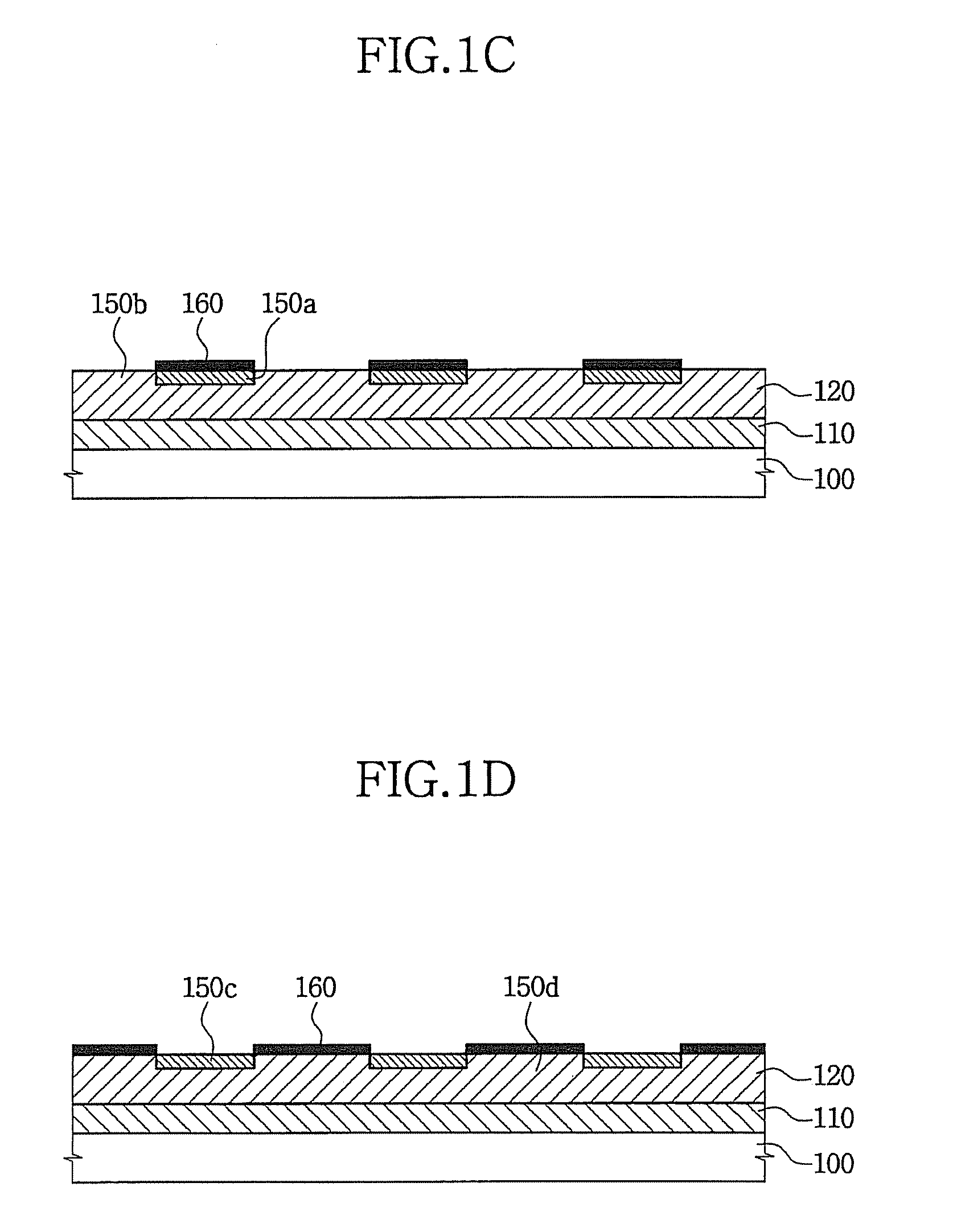

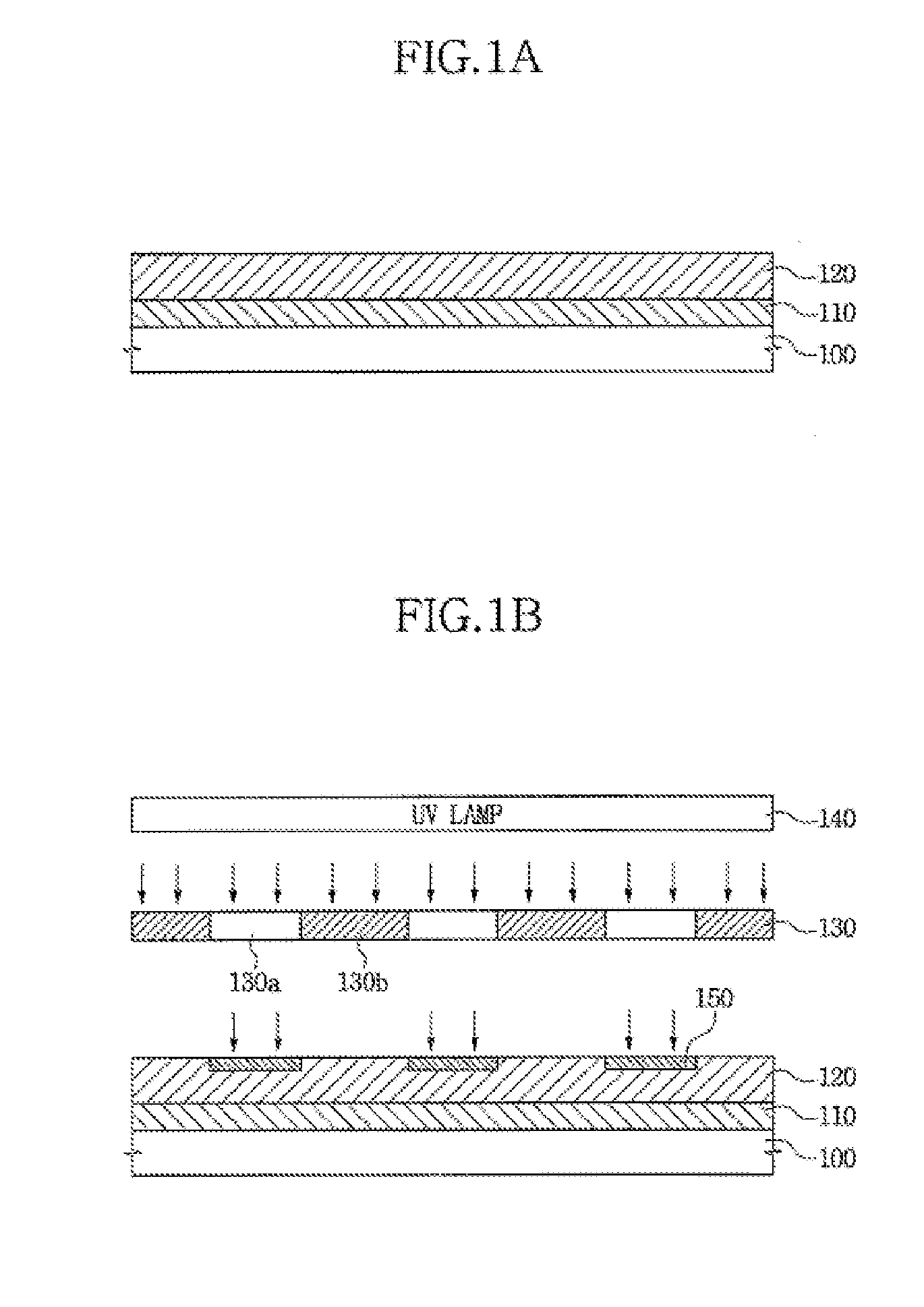

A method of forming a polycrystalline silicon layer and an atomic layer deposition apparatus used for the same. The method includes forming an amorphous silicon layer on a substrate, exposing the substrate having the amorphous silicon layer to a hydrophilic or hydrophobic gas atmosphere, placing a mask having at least one open and at least one closed portion over the amorphous silicon layer, irradiating UV light toward the amorphous silicon layer and the mask using a UV lamp, depositing a crystallization-inducing metal on the amorphous silicon layer, and annealing the substrate to crystallize the amorphous silicon layer into a polycrystalline silicon layer. This method and apparatus provide for controlling the seed position and grain size in the formation of a polycrystalline silicon layer.

Owner:SAMSUNG DISPLAY CO LTD

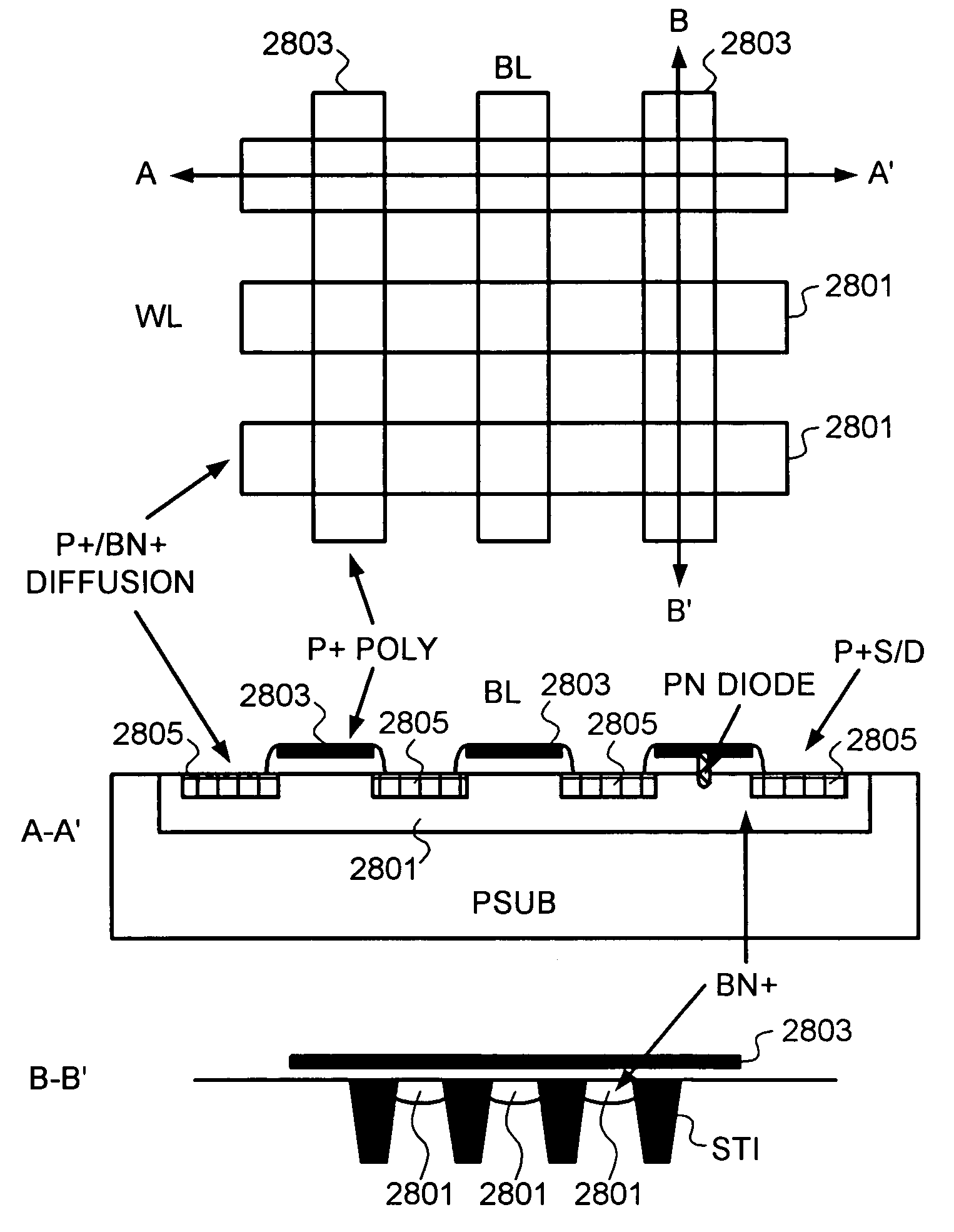

High density semiconductor memory cell and memory array using a single transistor and having counter-doped poly and buried diffusion wordline

A programmable memory cell comprised of a transistor located at the crosspoint of a column bitline and a row wordline is disclosed. The transistor has its gate formed from the column bitline and its source connected to the row wordline. The memory cell is programmed by applying a voltage potential between the column bitline and the row wordline to produce a programmed p+ region to form a p-n diode in the substrate underlying the gate of the transistor. Further, the wordline is formed from a buried diffusion N+ layer while the column bitline is formed from a counterdoped polysilicon layer.

Owner:SYNOPSYS INC

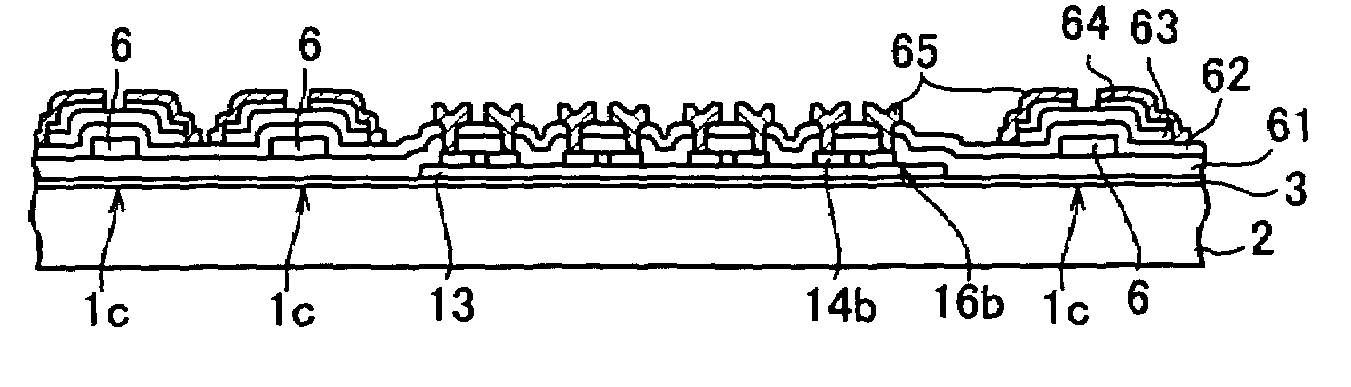

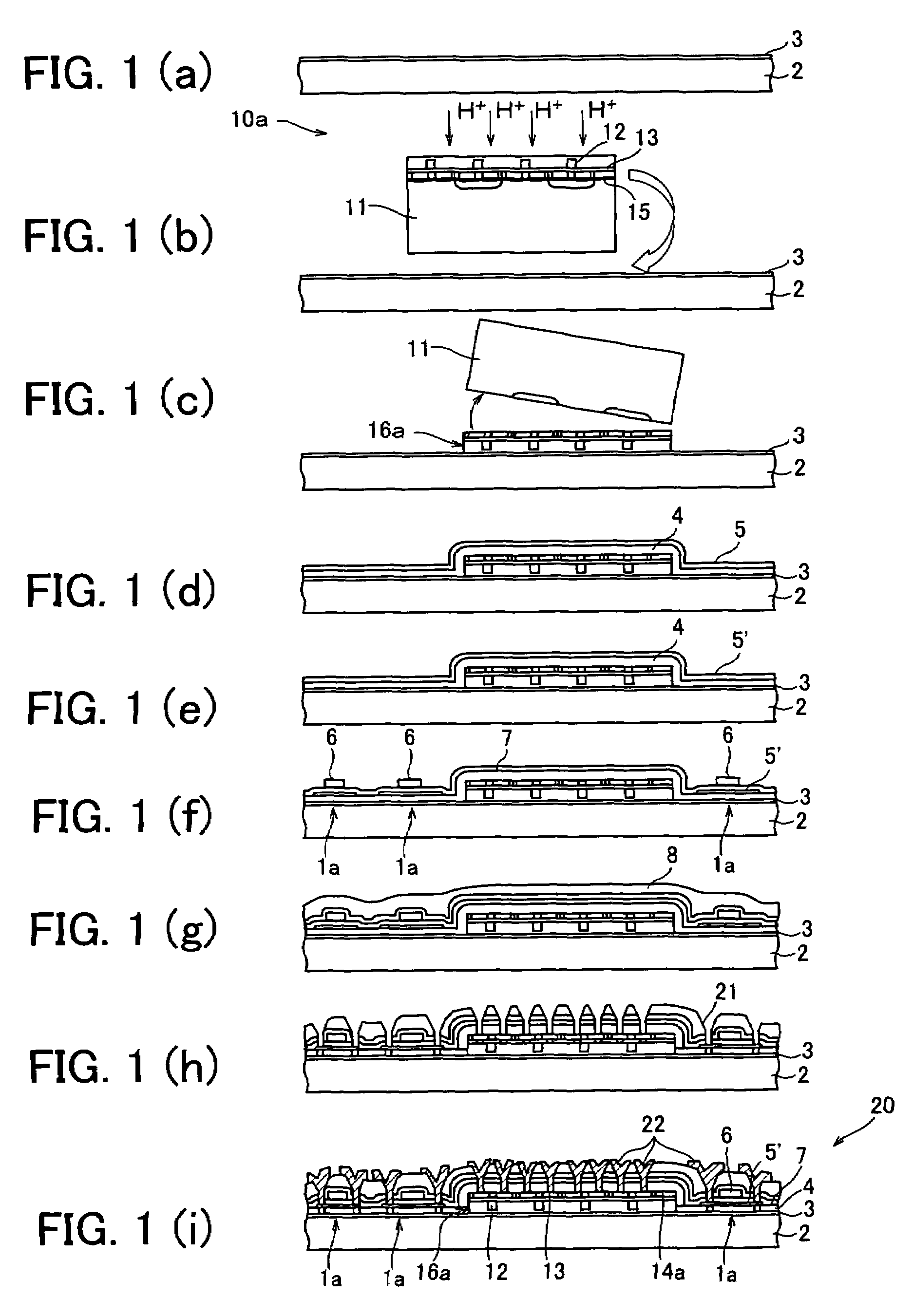

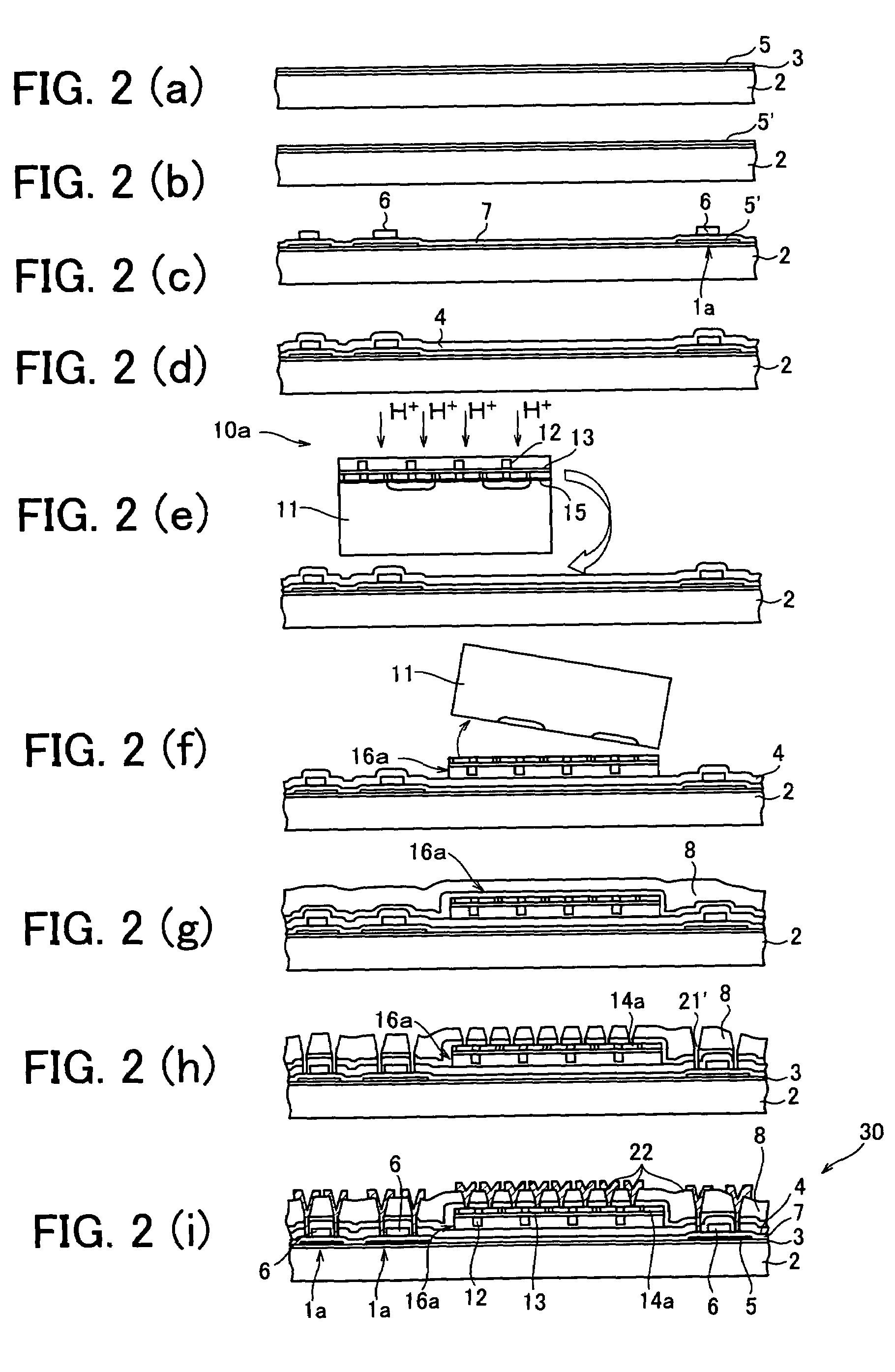

Semiconductor thin film forming method, production methods for semiconductor device and electrooptical device, devices used for these methods, and semiconductor device and electrooptical device

InactiveUS20030013280A1Promote crystallizationTransistorPolycrystalline material growthSingle crystalCrystallinity

An object of the present invention is to provide a method for easily forming a polycrystalline semiconductor thin-film, such as polycrystalline silicon having high crystallinity and high quality, or a single crystalline semiconductor thin-film at inexpensive cost, the crystalline semiconductor thin-film having a large area, and to provide an apparatus for processing the method described above. In forming a polycrystalline (or single crystalline) semiconductor thin-film (7), such as a polycrystalline silicon thin-film, having high crystallinity and a large grain size on a substrate (1), or in forming a semiconductor device having the polycrystalline (or single crystalline) semiconductor thin-film (7) on the substrate (1), a method comprises forming a low-crystallization semiconductor thin-film (7A) on the substrate (1), and subsequently heating and cooling this low-crystallization semiconductor thin-film (7A) to a fusion, a semi-fusion, or a non-fusion state by flash lamp annealing to facilitate the crystallization of the low-crystallization semiconductor thin-film, whereby a polycrystalline (single crystalline) semiconductor thin-film (7) is obtained. A method for forming the semiconductor device and an apparatus for processing the methods are also disclosed.

Owner:SONY CORP

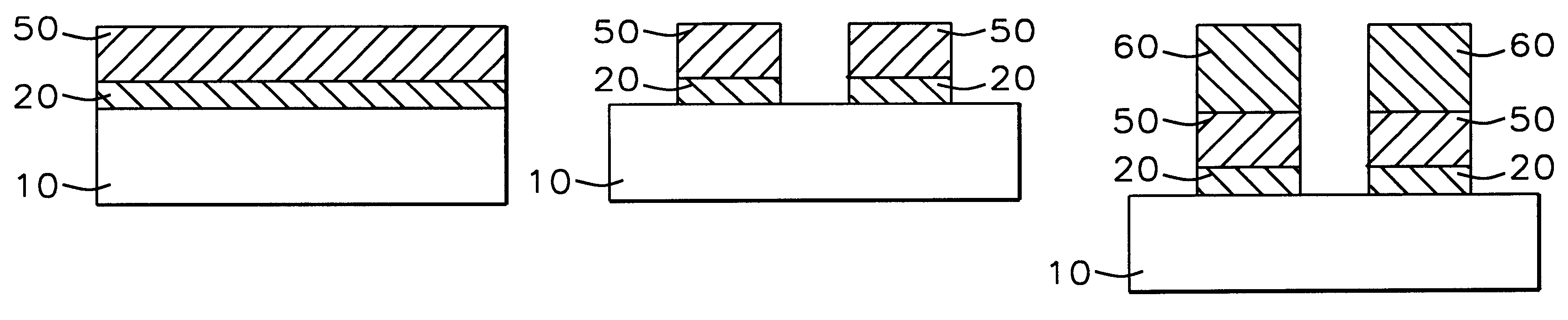

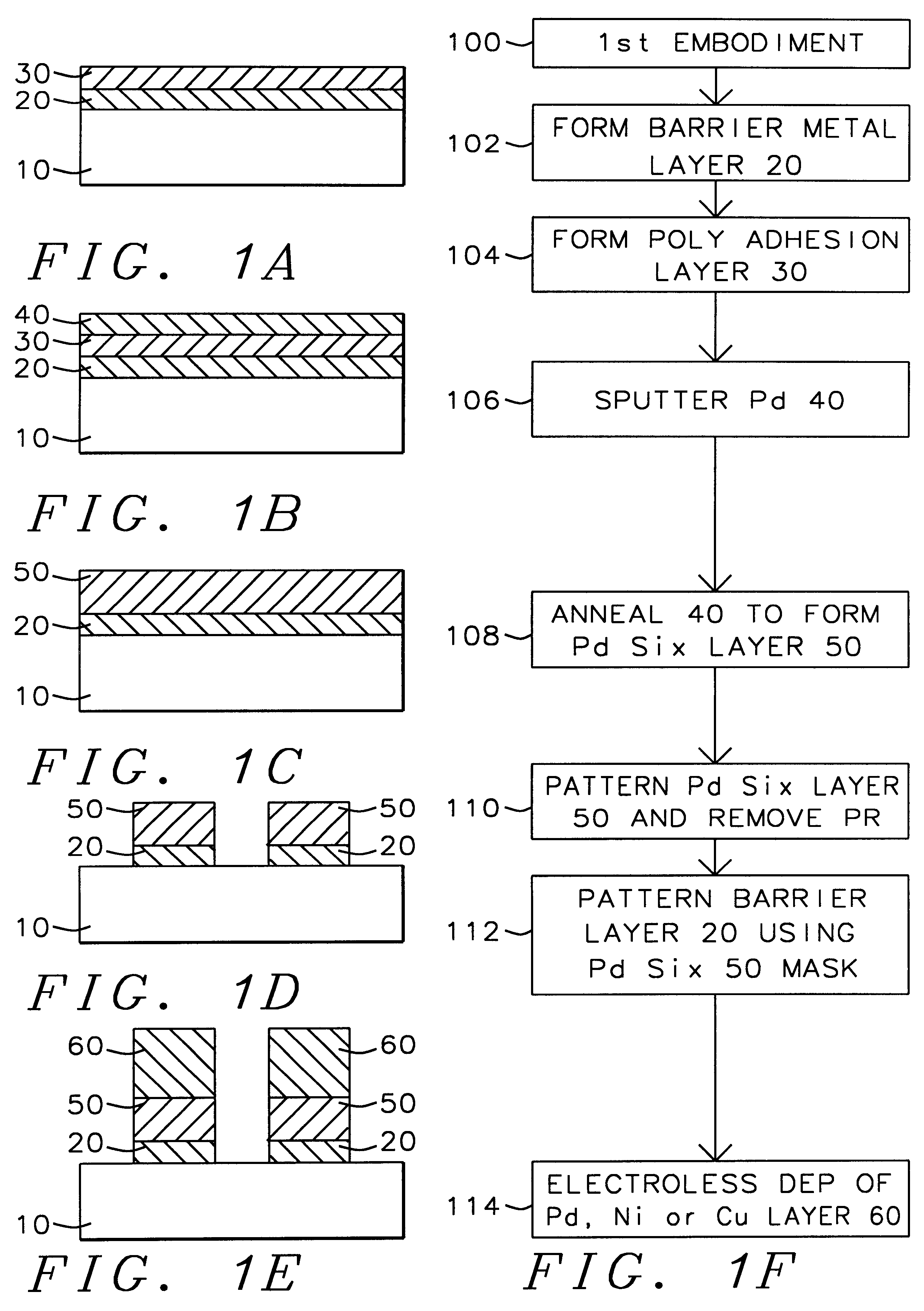

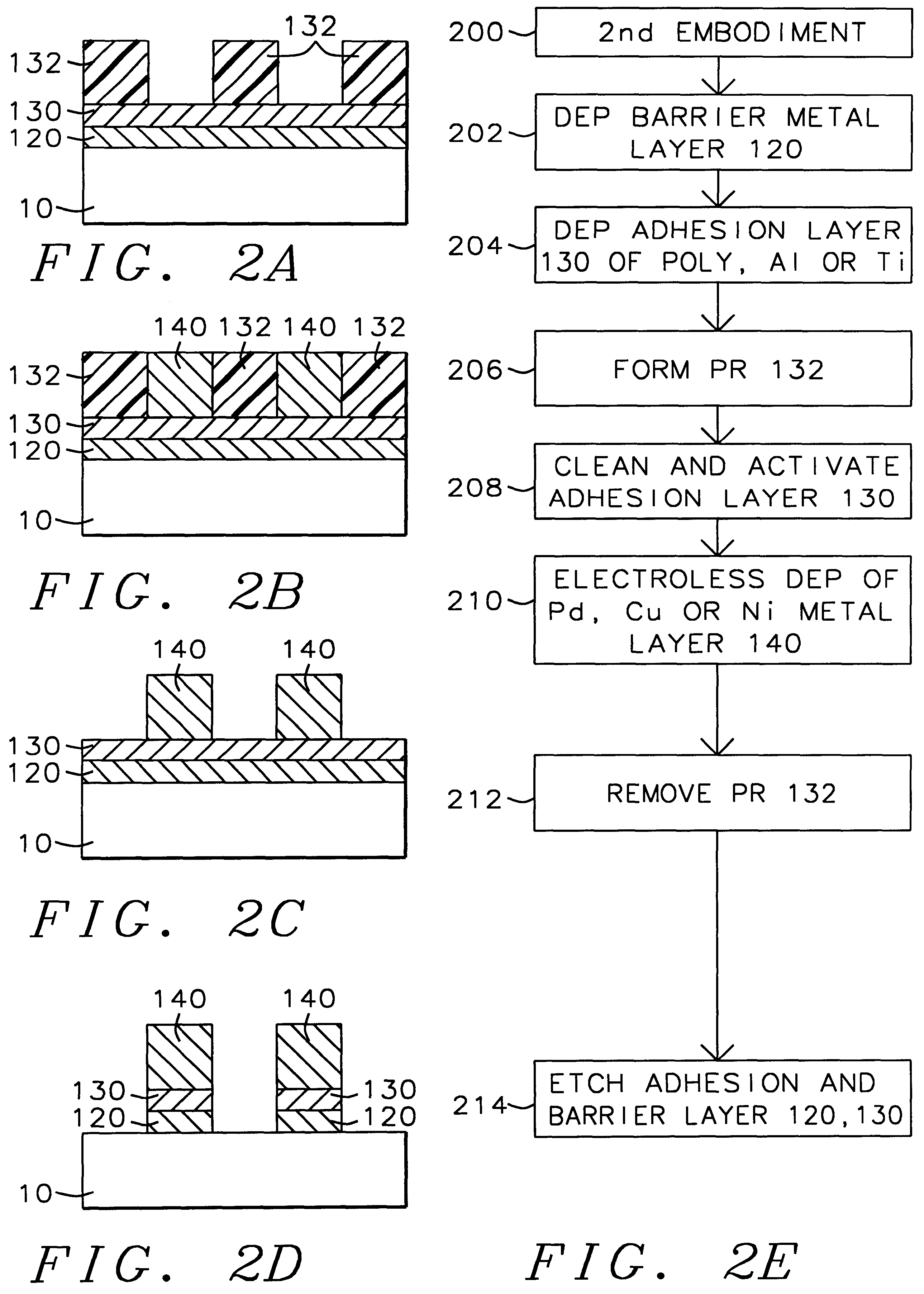

Method of electroless plating copper on nitride barrier

InactiveUS6436816B1Insulating substrate metal adhesion improvementSolid-state devicesCopper platingElectroless deposition

A method with three embodiments of manufacturing metal lines and solder bumps using electroless deposition techniques. The first embodiment uses a PdSix seed layer 50 for electroless deposition. The PdSix layer 50 does not require activation. A metal line is formed on a barrier layer 20 and an adhesion layer 30. A Palladium silicide seed layer 50 is then formed and patterned. Ni, Pd or Cu is electroless deposited over the Palladium silicide layer 50 to form a metal line. The second embodiment selectively electrolessly deposits metal 140 over an Adhesion layer 130 composed of Poly Si, Al, or Ti. A photoresist pattern 132 is formed over the adhesion layer. A metal layer 140 of Cu or Ni is electrolessly deposited over the adhesion layer. The photoresist layer 132 is removed and the exposed portion of the adhesion layer 130 and the underlying barrier metal layer 120 are etched thereby forming a metal line. The third embodiment electroless deposits metal over a metal barrier layer that is roughen by chemical mechanical polishing. A solder bump is formed using an electroless deposition of Cu or Ni by: depositing an Al layer 220 and a barrier metal layer 230 over a substrate 10. The barrier layer 230 is polished and activated. Next, the aluminum layer 220 and the barrier metal layer 230 are patterned. A metal layer 240 is electroless deposited. Next a solder bump 250 is formed over the electroless metal layer 240.

Owner:TAIWAN SEMICON MFG CO LTD

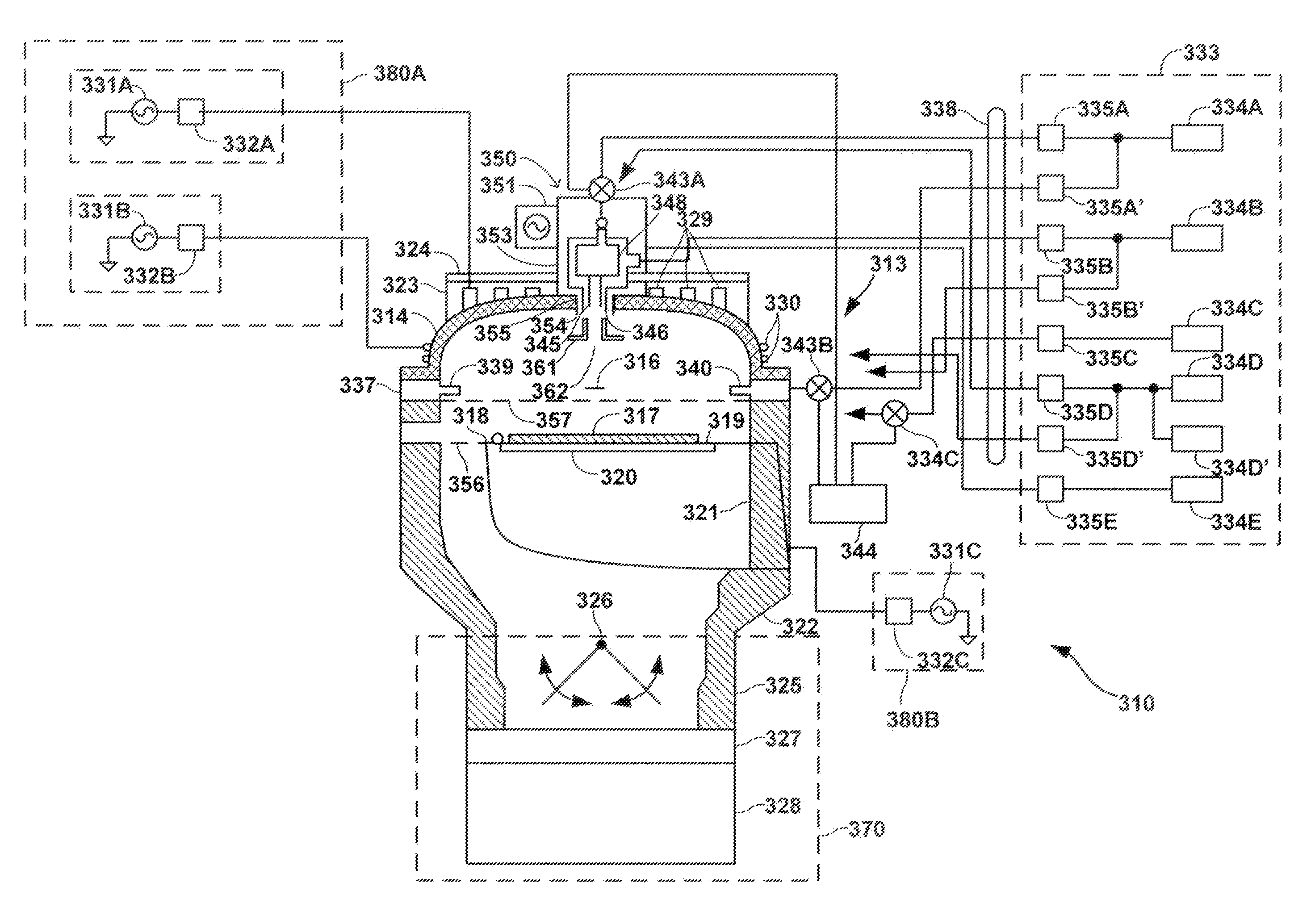

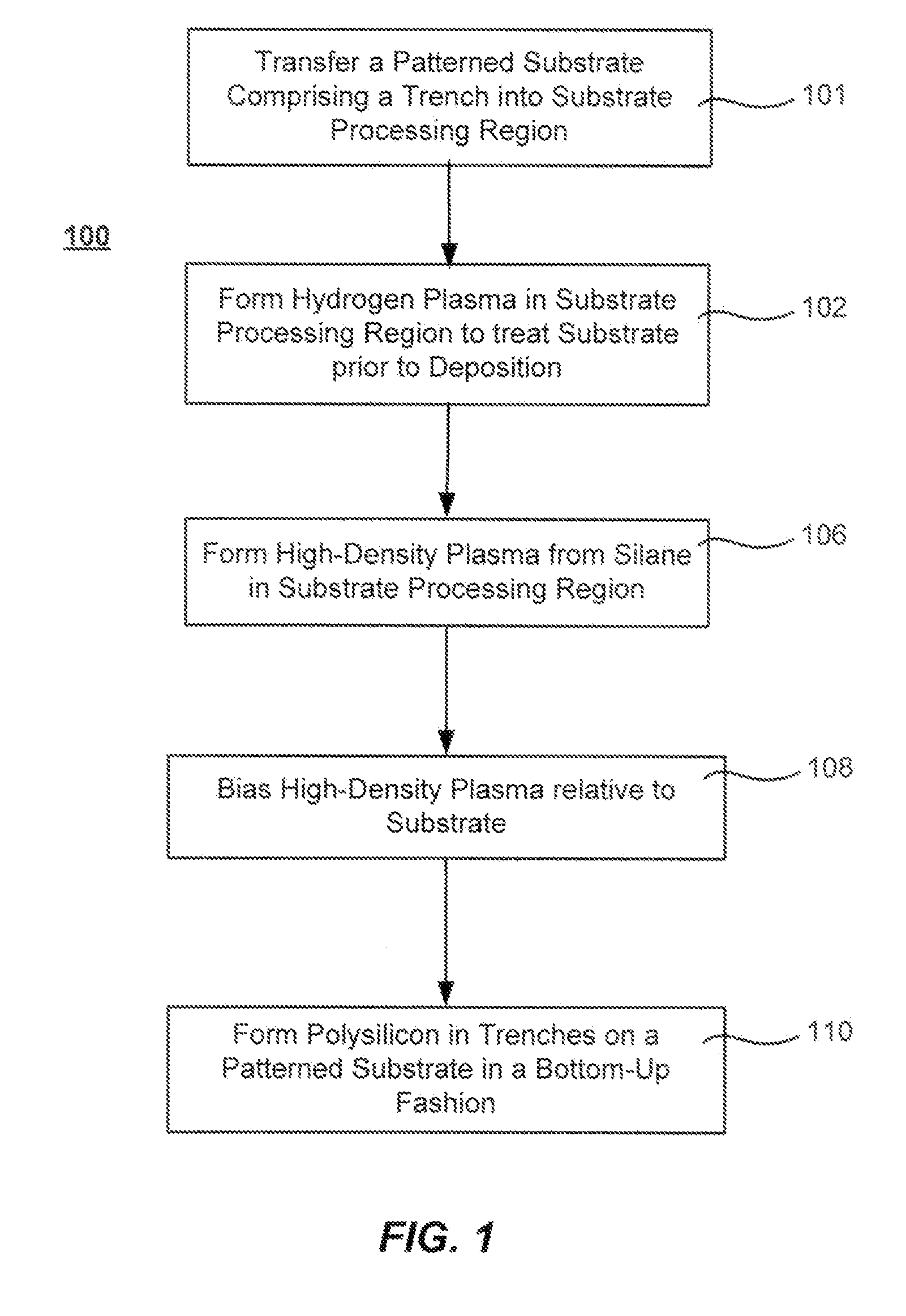

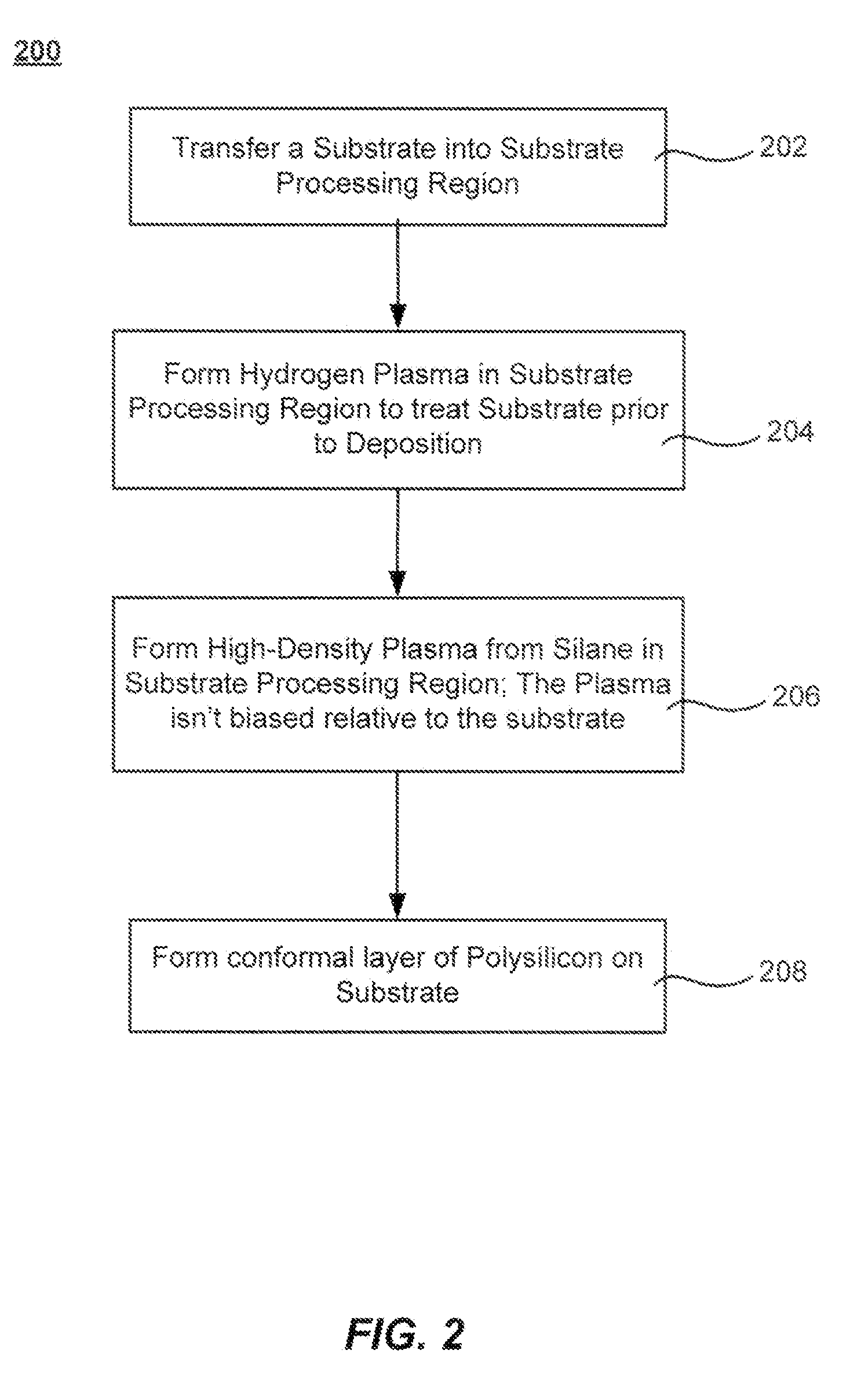

Polysilicon films by HDP-CVD

InactiveUS8450191B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingDopantHigh density

Methods of forming polysilicon layers are described. The methods include forming a high-density plasma from a silicon precursor in a substrate processing region containing the deposition substrate. The described methods produce polycrystalline films at reduced substrate temperature (e.g. <500° C.) relative to prior art techniques. The availability of a bias plasma power adjustment further enables adjustment of conformality of the formed polysilicon layer. When dopants are included in the high density plasma, they may be incorporated into the polysilicon layer in such a way that they do not require a separate activation step.

Owner:APPLIED MATERIALS INC

Zero shrinkage smooth interface oxy-nitride and oxy-amorphous-silicon stacks for 3D memory vertical gate application

InactiveUS20130161629A1Reduce AlFx depositReduce AlFx buildingSolid-state devicesSemiconductor/solid-state device manufacturingDeposition temperatureAmorphous silicon

Methods are provided for depositing a stack of film layers for use in vertical gates for 3D memory devices, by depositing a sacrificial nitride film layer at a sacrificial film deposition temperature greater than about 550° C.; depositing an oxide film layer over the nitride film layer, at an oxide deposition temperature of about 600° C. or greater; repeating the above steps to deposit a film stack having alternating layers of the sacrificial films and the oxide films; forming a plurality of holes in the film stack; and depositing polysilicon in the plurality of holes in the film stack at a polysilicon process temperature of about 700° C. or greater, wherein the sacrificial film layers and the oxide film layers experience near zero shrinkage during the polysilicon deposition. Flash drive memory devices may also be made by these methods.

Owner:APPLIED MATERIALS INC

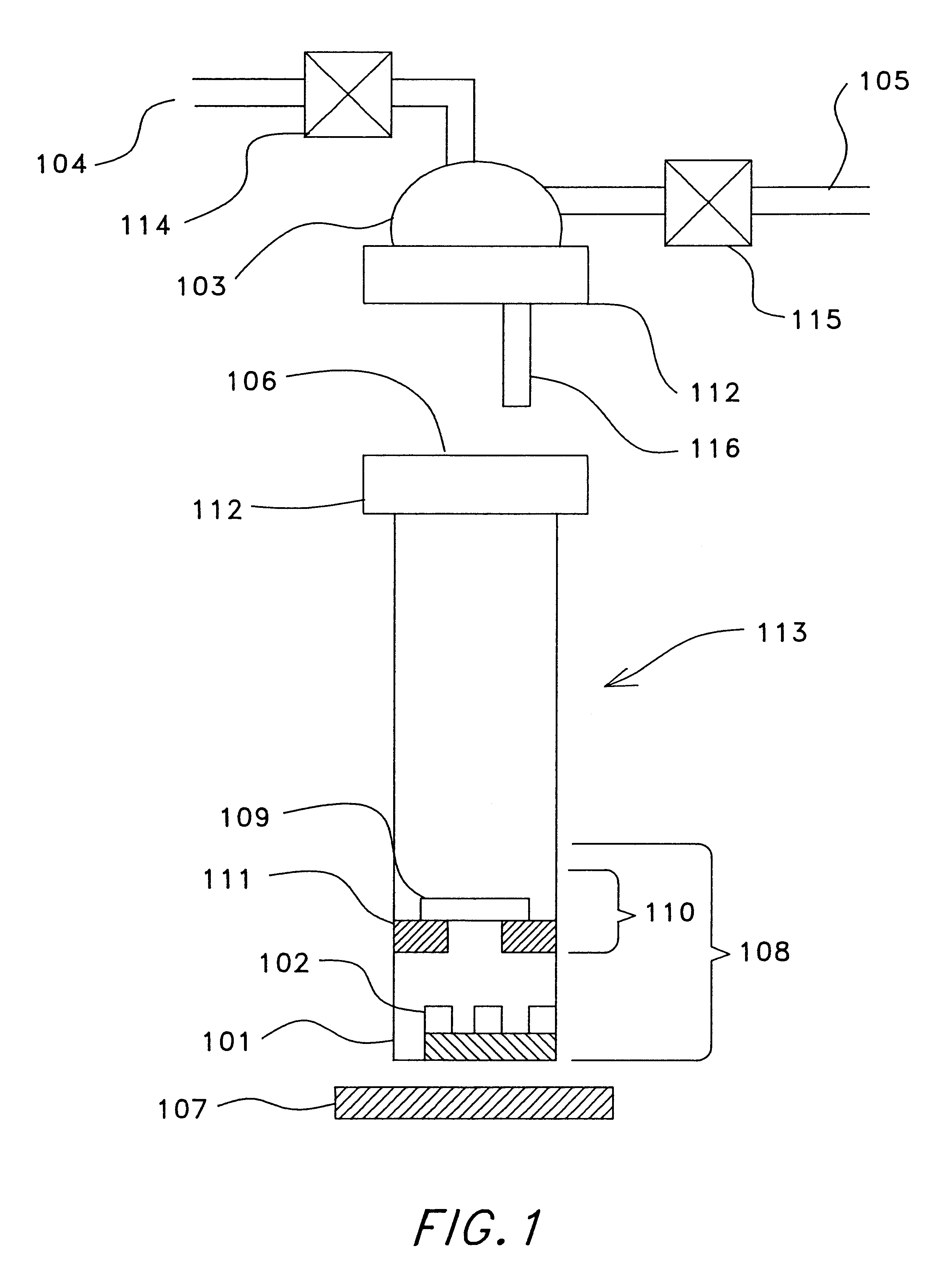

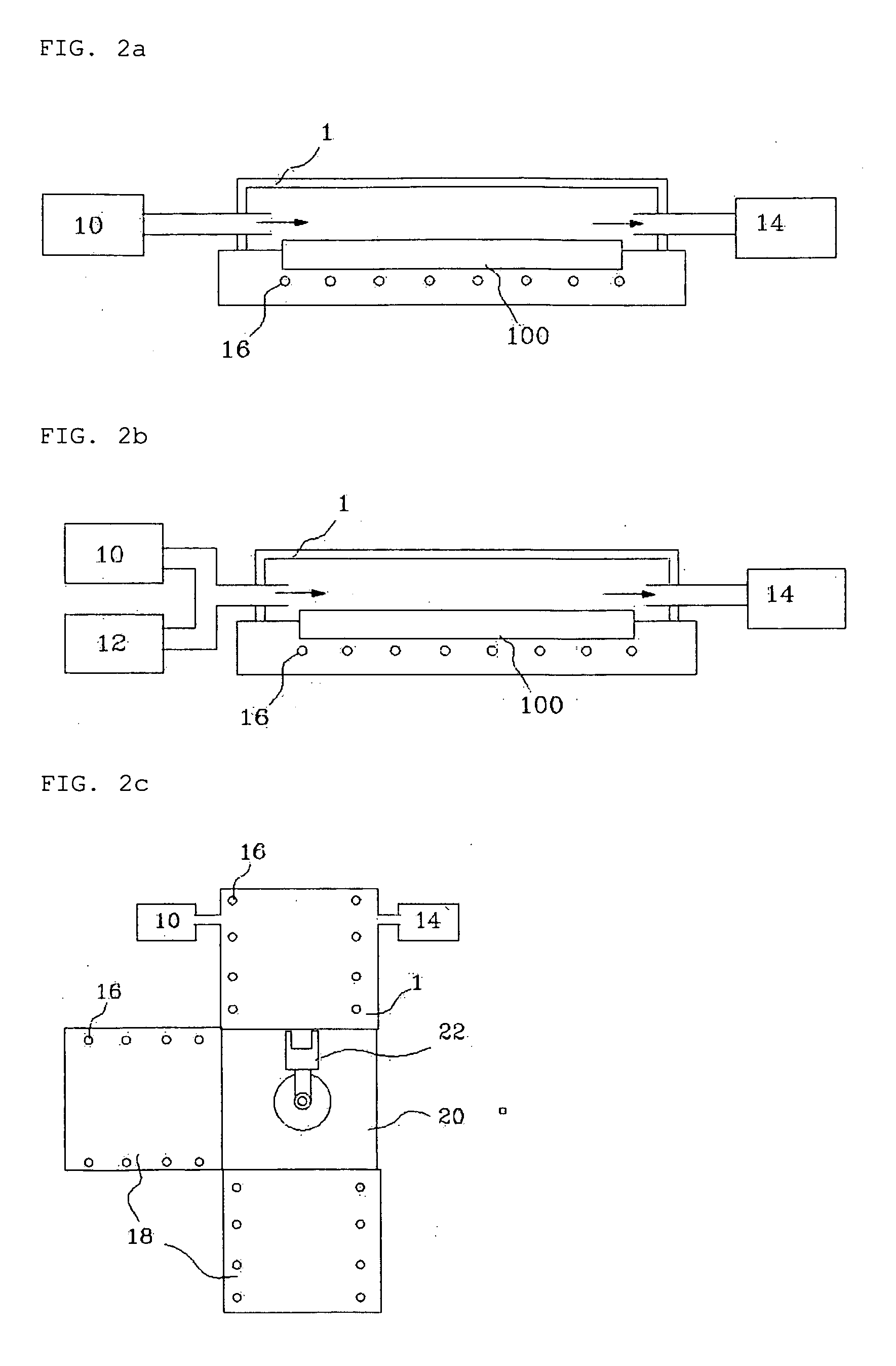

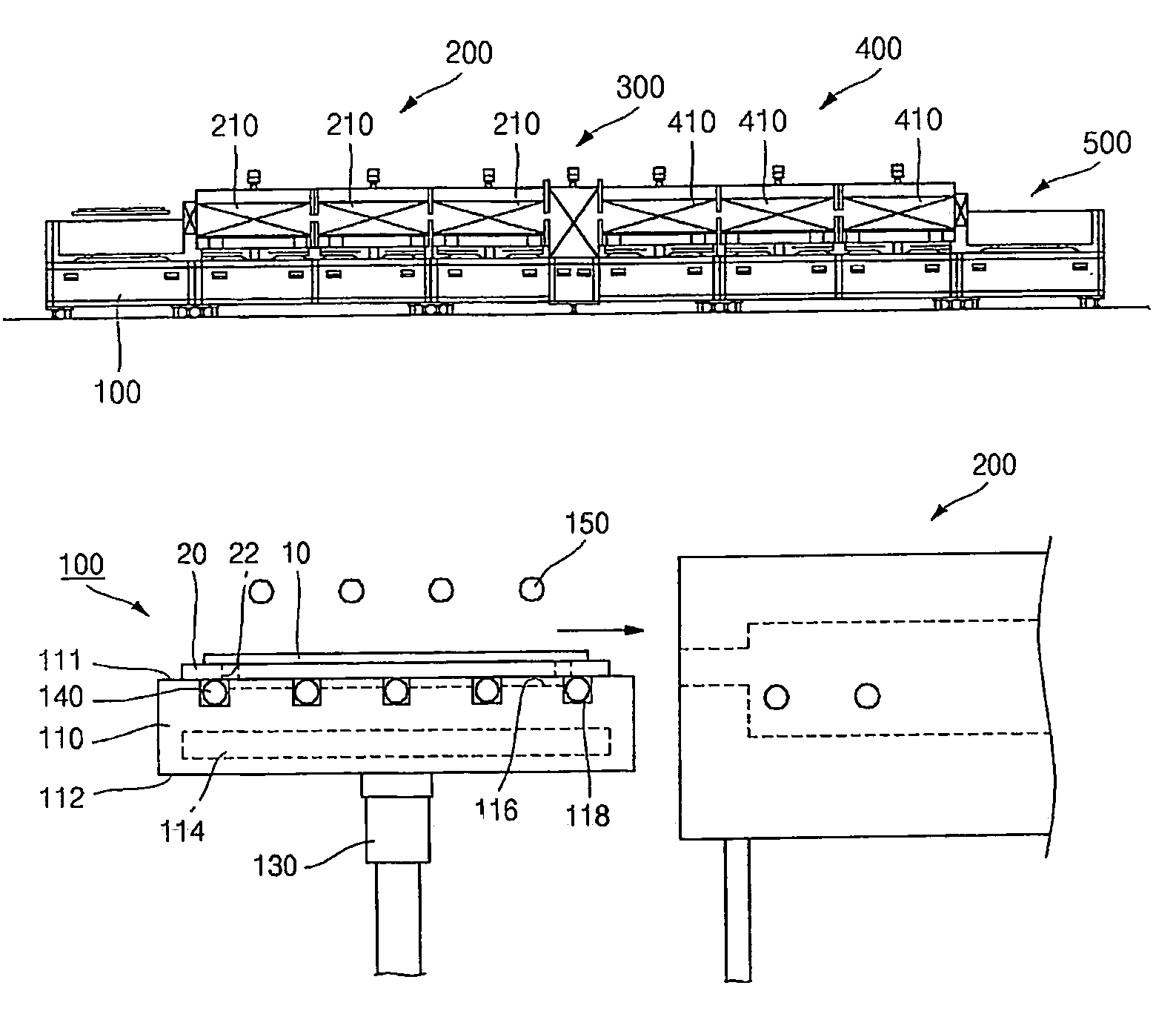

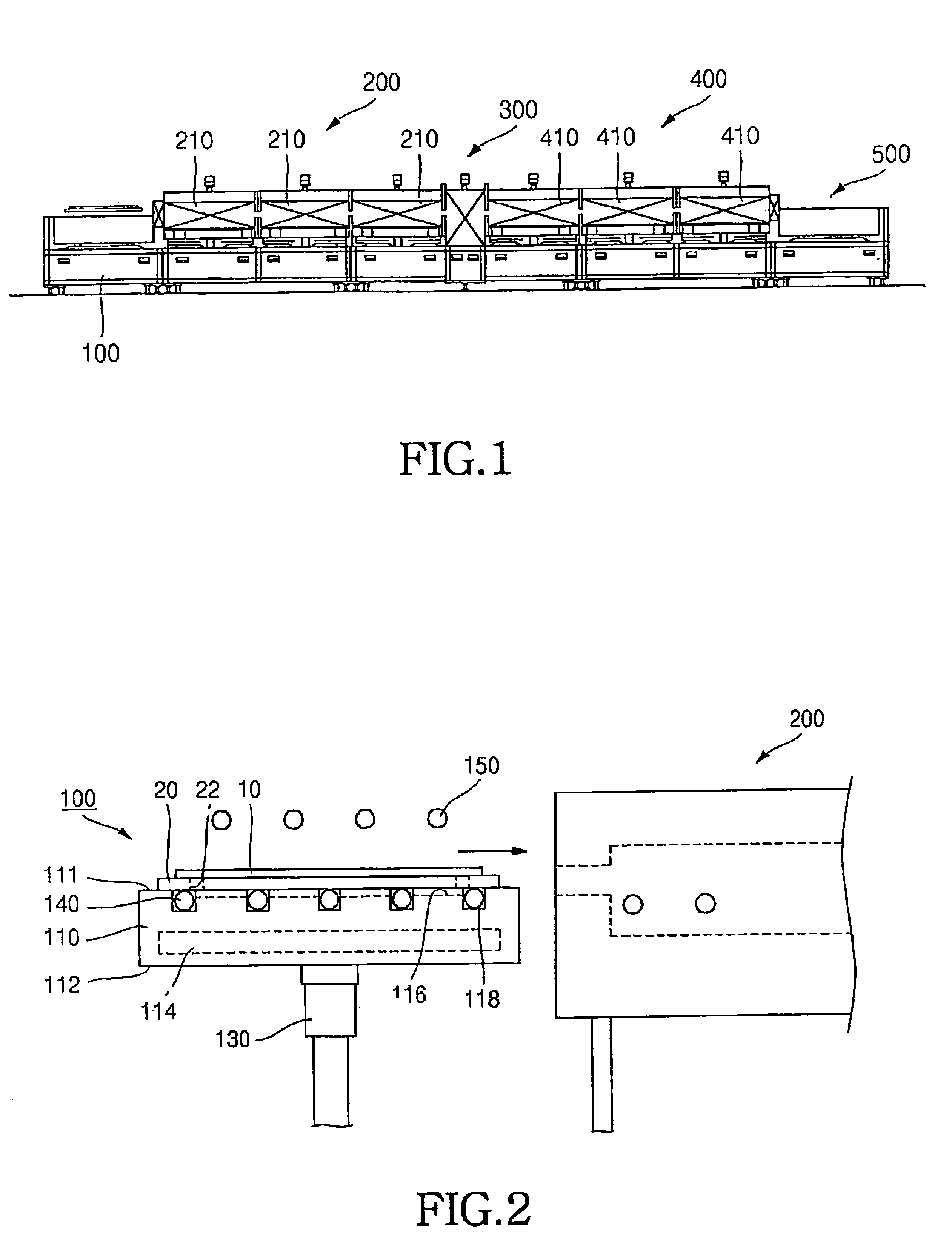

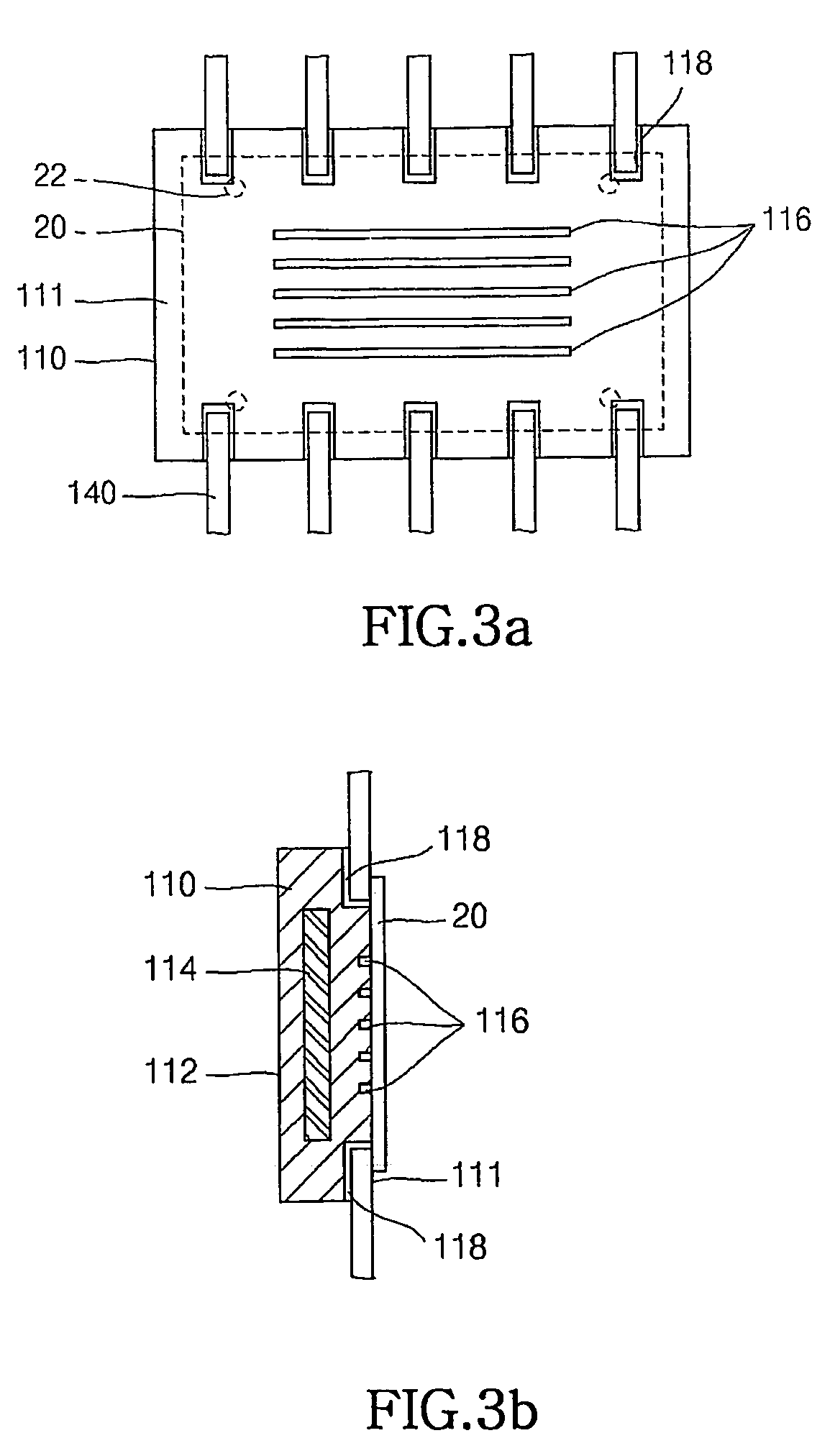

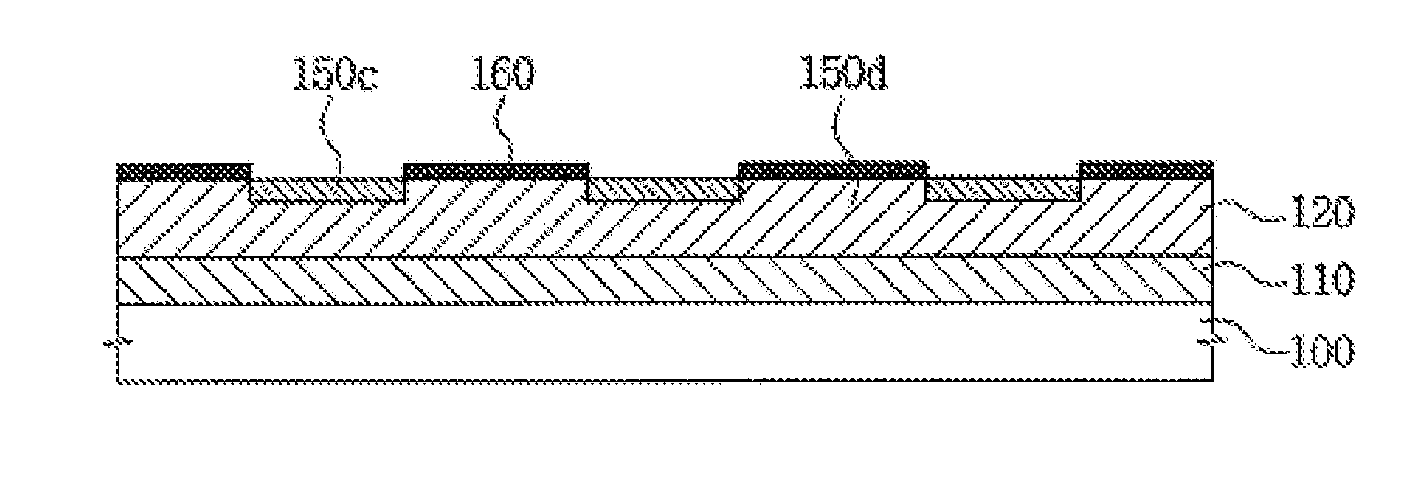

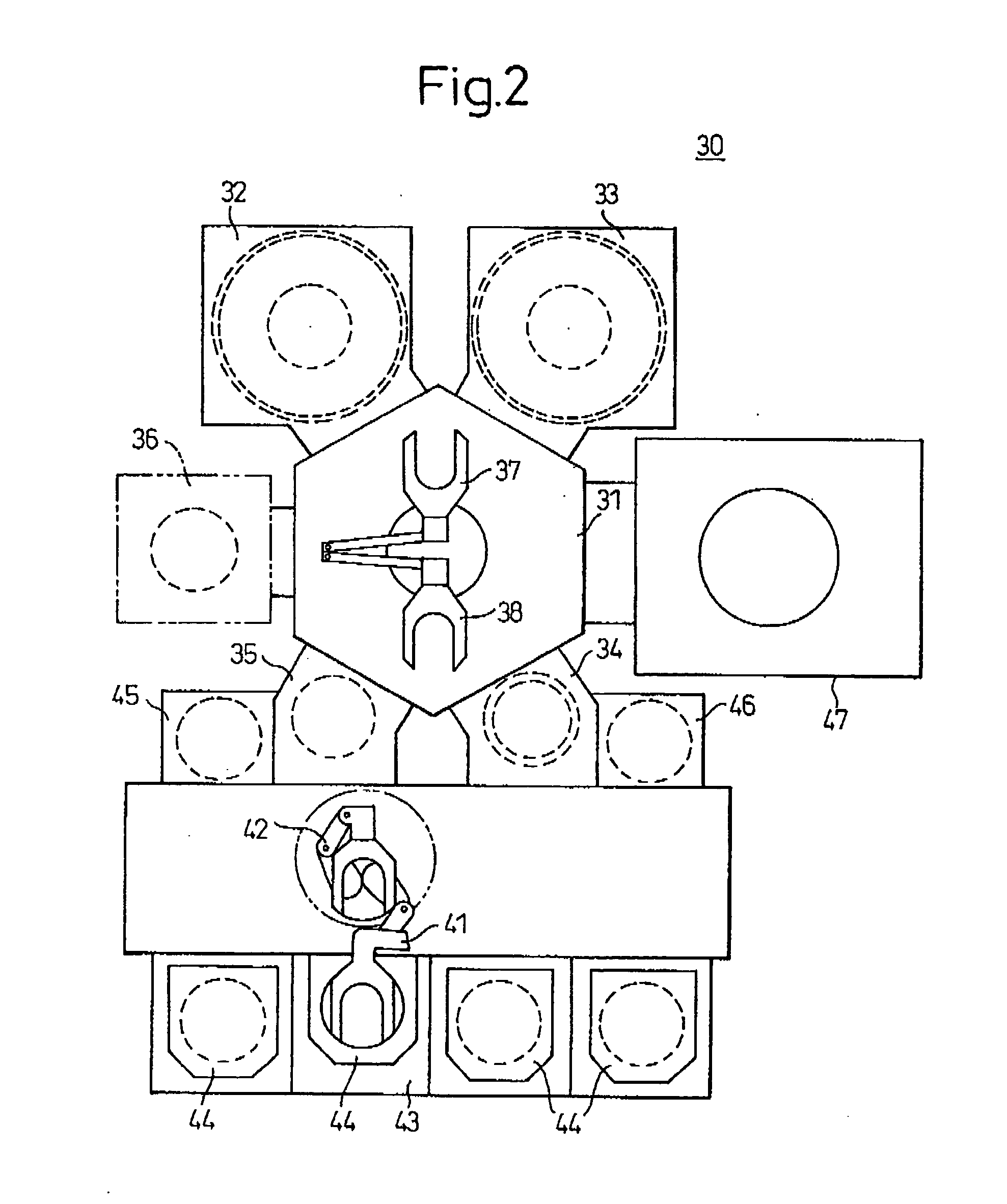

System for heat treatment of semiconductor device

InactiveUS7989736B2Avoid damageIncrease temperatureFurnaces without endless coreSemiconductor/solid-state device manufacturingElectromotive forceSilicon thin film

Disclosed is a heat treatment system for semiconductor devices. The heat treatment system is used in a heat treatment process for semiconductor devices, such as a crystallization process for an amorphous silicon thin film or a dopant activation process for a poly-crystalline silicon thin film formed on a surface of a glass substrate of a flat display panel including a liquid crystal display (LCD) or an organic light emitting device (OLED). The heat treatment system transfers a semiconductor device after uniformly preheating the semiconductor device in order to prevent deformation of the semiconductor device during the heat treatment process, rapidly performs the heat treatment process under the high temperature condition by heating the semiconductor device using a lamp heater and induction heat derived from induced electromotive force, and unloads the semiconductor device after uniformly cooling the semiconductor device such that the semiconductor device is prevented from being deformed when the heat treatment process has been finished. The heat treatment system rapidly performs the heat treatment process while preventing deformation of the semiconductor device by gradually heating or cooling the semiconductor device.

Owner:VIATRON TECH INC

Method of forming polycrystalline silicon layer and atomic layer deposition apparatus used for the same

ActiveUS20110263107A1Vacuum evaporation coatingSemiconductor/solid-state device manufacturingAmorphous siliconOptoelectronics

A method of forming a polycrystalline silicon layer and an atomic layer deposition apparatus used for the same. The method includes forming an amorphous silicon layer on a substrate, exposing the substrate having the amorphous silicon layer to a hydrophilic or hydrophobic gas atmosphere, placing a mask having at least one open and at least one closed portion over the amorphous silicon layer, irradiating UV light toward the amorphous silicon layer and the mask using a UV lamp, depositing a crystallization-inducing metal on the amorphous silicon layer, and annealing the substrate to crystallize the amorphous silicon layer into a polycrystalline silicon layer. This method and apparatus provide for controlling the seed position and grain size in the formation of a polycrystalline silicon layer.

Owner:SAMSUNG DISPLAY CO LTD

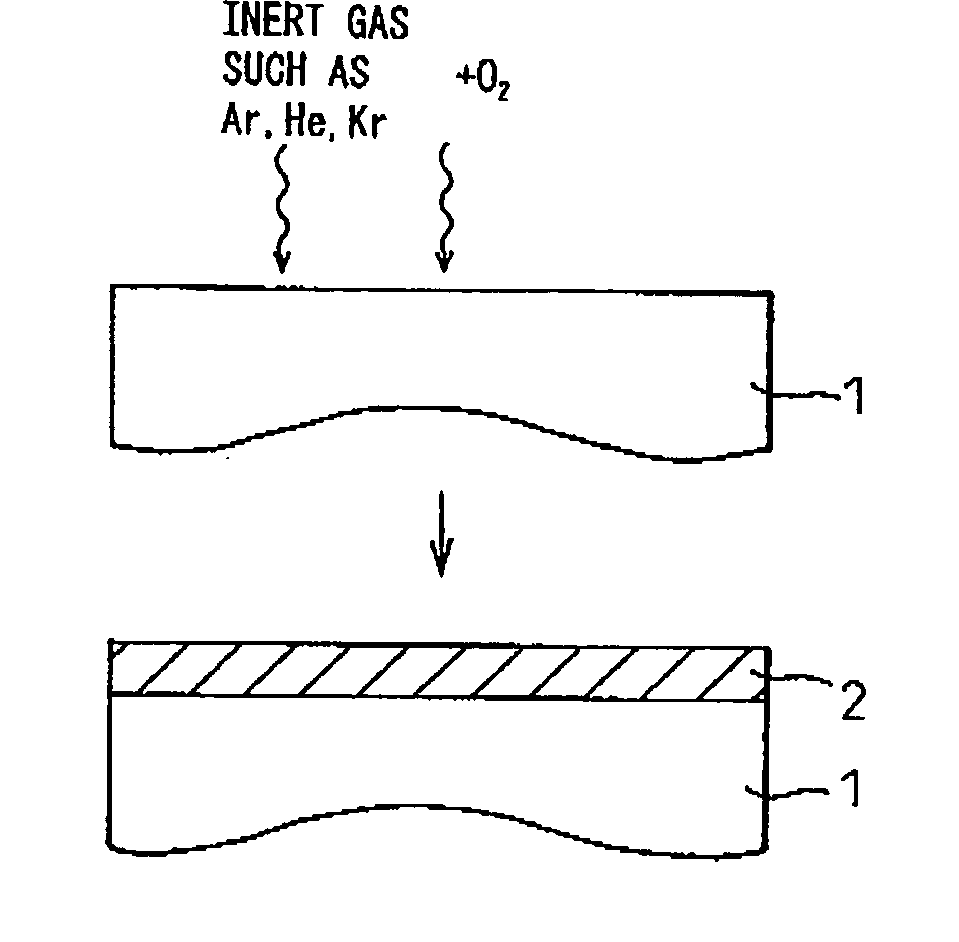

Method for producing material of electronic device

InactiveUS20040142577A1Quality improvementSemiconductor/solid-state device manufacturingSolid state diffusion coatingOxygenNitrogen gas

A process for producing electronic device (for example, high-performance MOS-type semiconductor device) structure having a good electric characteristic, wherein an SiO2 film or SiON film is used as an insulating film having an extremely thin (2.5 nm or less, for example) film thickness, and poly-silicon, amorphous-silicon, or SiGe is used as an electrode. In the presence of process gas comprising oxygen and an inert gas, plasma including oxygen and the inert gas (or plasma comprising nitrogen and an inert gas, or plasma comprising nitrogen, an inert gas and hydrogen) is generated by irradiating a wafer W including Si as a main component with microwave via a plane antenna member SPA. An oxide film (or oxynitride film) is formed on the wafer surface by using the thus generated plasma, and as desired, an electrode of poly-silicon, amorphous-silicon, or SiGe is formed, to thereby form an electronic device structure.

Owner:TOKYO ELECTRON LTD

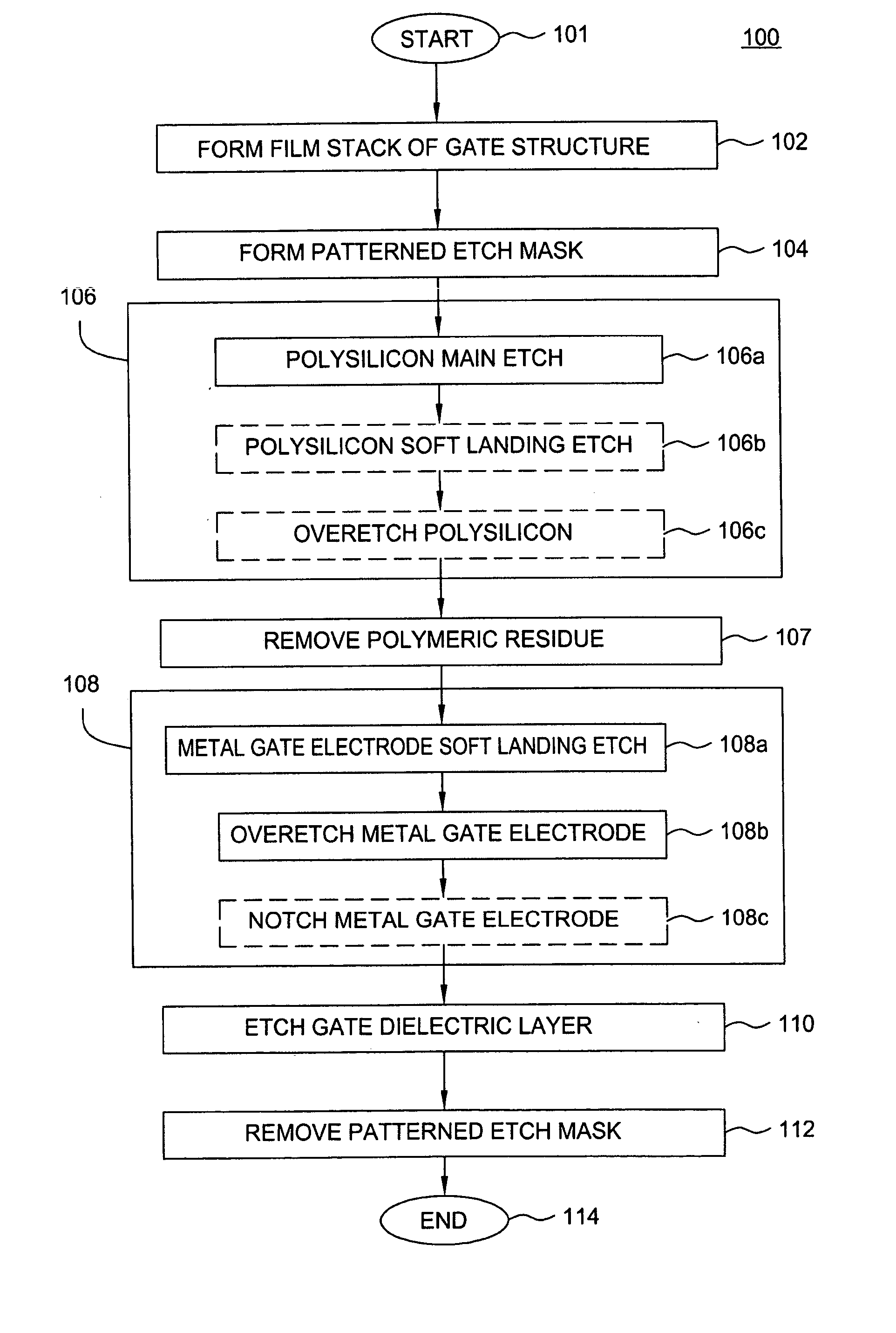

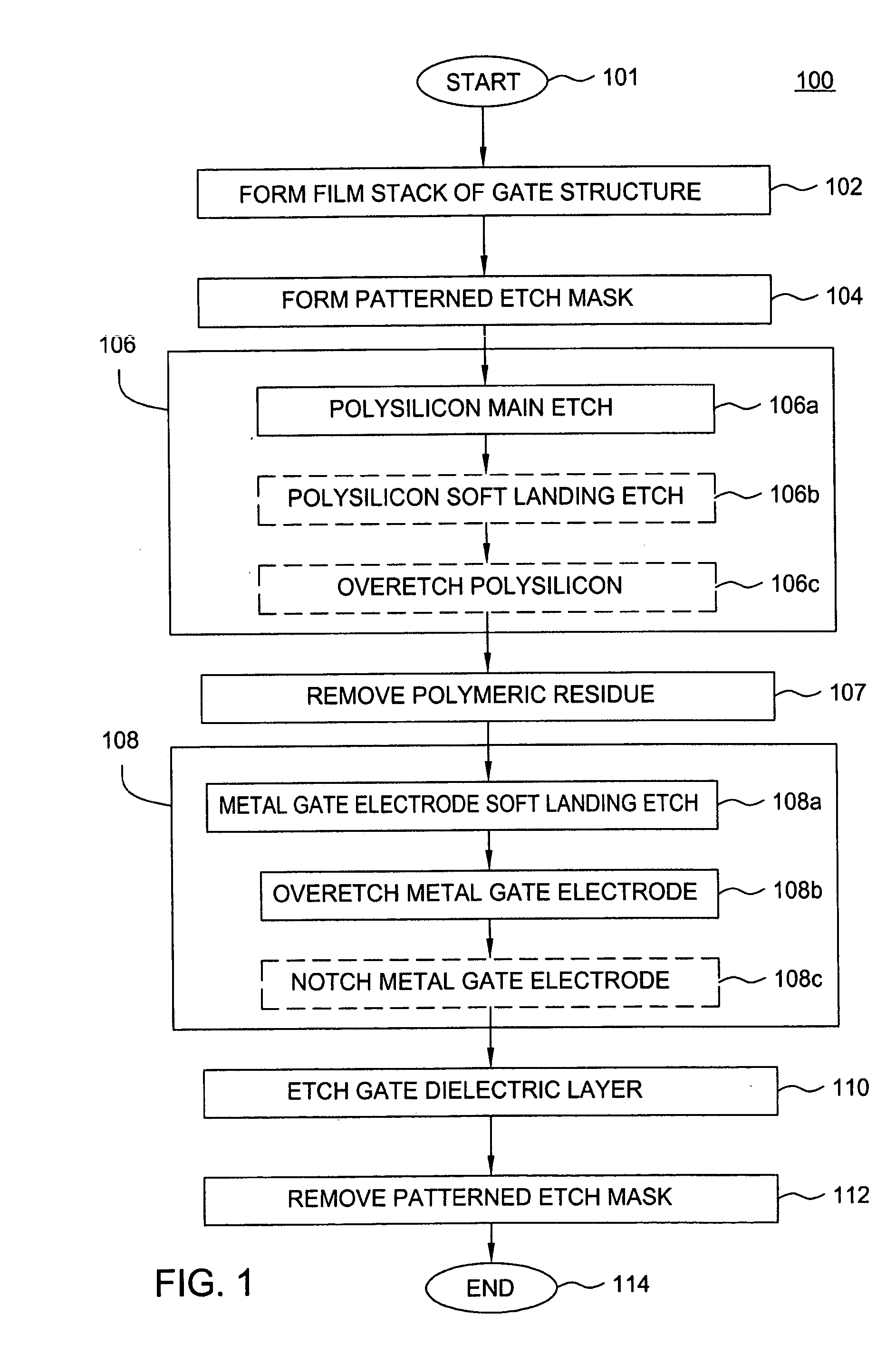

Method of fabricating a gate structure of a field effect transistor having a metal-containing gate electrode

InactiveUS20050009358A1High selectivitySemiconductor/solid-state device detailsSolid-state devicesBromineTitanium nitride

A method of etching metals and / or metal-containing compounds using a plasma comprising a bromine-containing gas. In one embodiment, the method is used during fabrication of a gate structure of a field effect transistor having a titanium nitride gate electrode, an ultra-thin (about 10 to 20 Angstroms) silicon dioxide gate dielectric, and a polysilicon upper contact. In a further embodiment, the gate electrode is selectively notched to a pre-determined width.

Owner:APPLIED MATERIALS INC

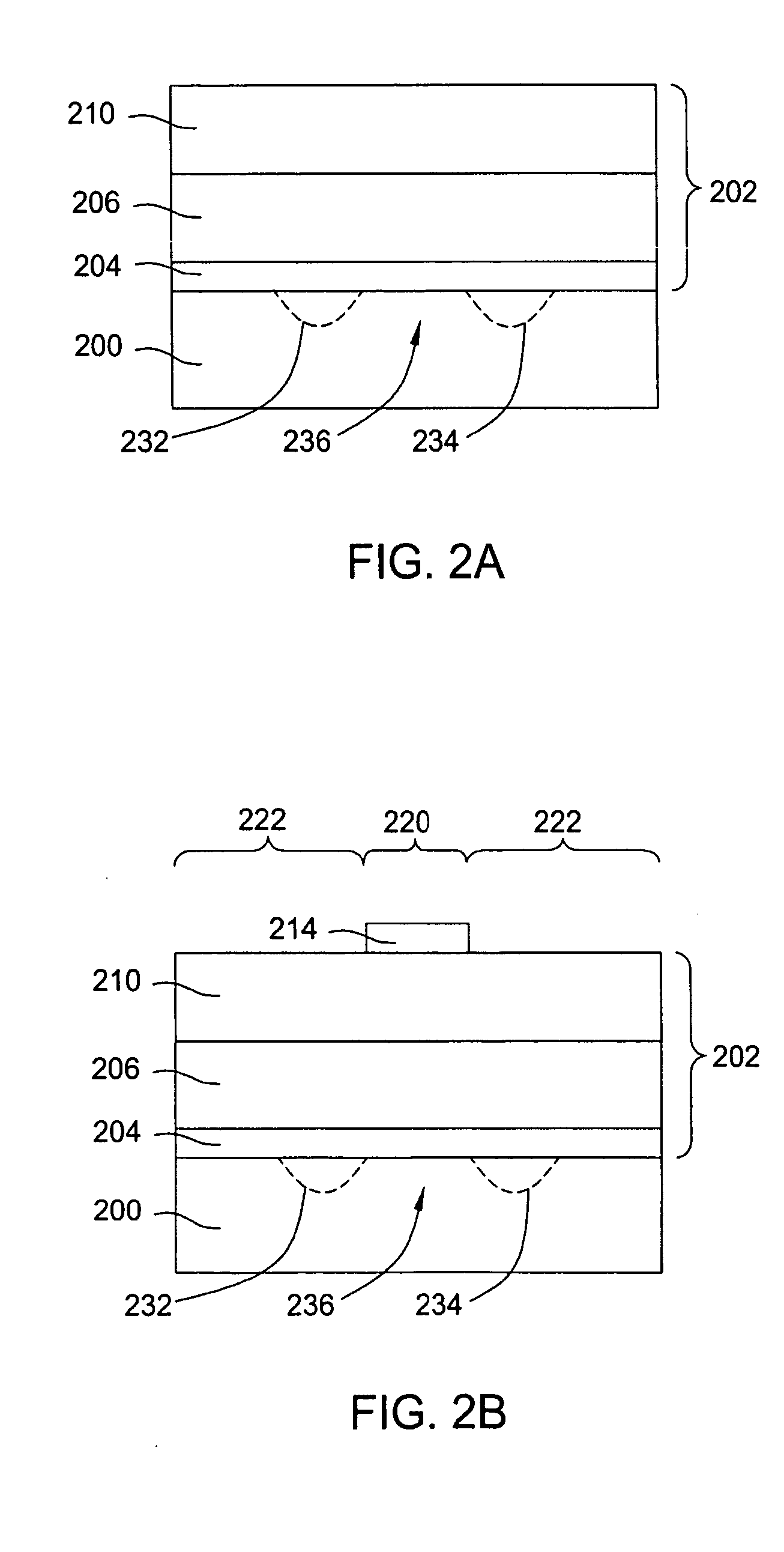

Linearity improvements of semiconductor substrate based radio frequency devices

ActiveUS7868419B1Effectively layerPrevent capacitance changeSemiconductor/solid-state device detailsSolid-state devicesCapacitanceHigh density

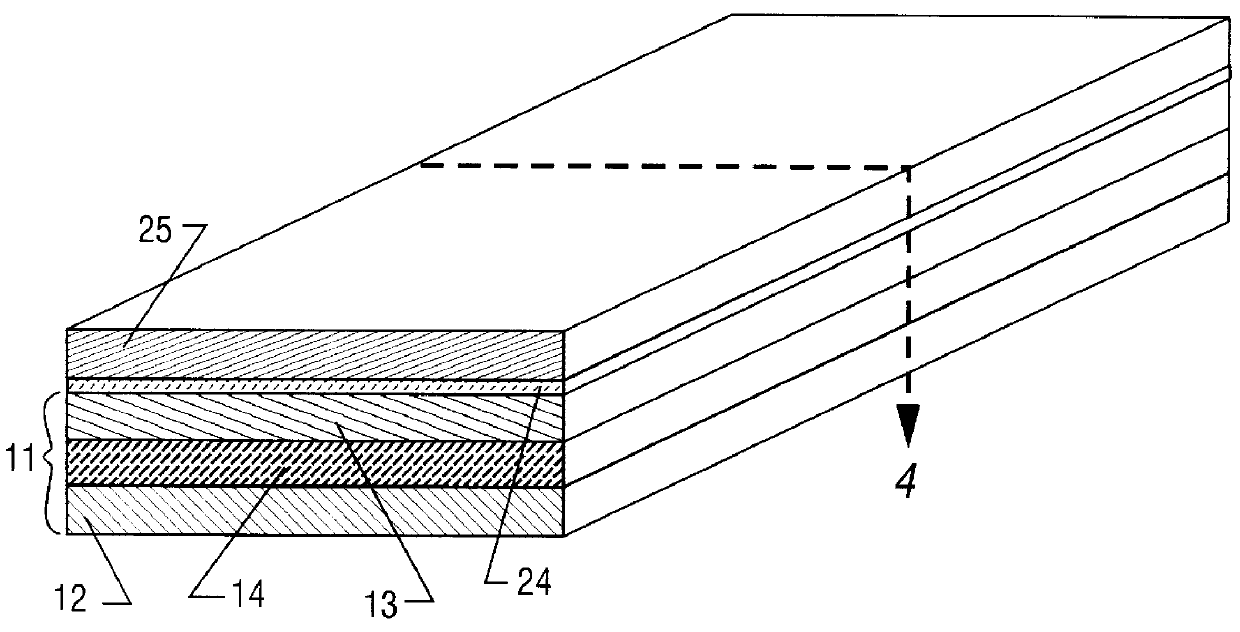

The present invention relates to using a trap-rich layer, such as a polycrystalline Silicon layer, over a semiconductor substrate to substantially immobilize a surface conduction layer at the surface of the semiconductor substrate at radio frequency (RF) frequencies. The trap-rich layer may have a high density of traps that trap carriers from the surface conduction layer. The average release time from the traps may be longer than the period of any present RF signals, thereby effectively immobilizing the surface conduction layer, which may substantially prevent capacitance and inductance changes due to the RF signals. Therefore, harmonic distortion of the RF signals may be significantly reduced or eliminated. The semiconductor substrate may be a Silicon substrate, a Gallium Arsenide substrate, or another substrate.

Owner:QORVO US INC

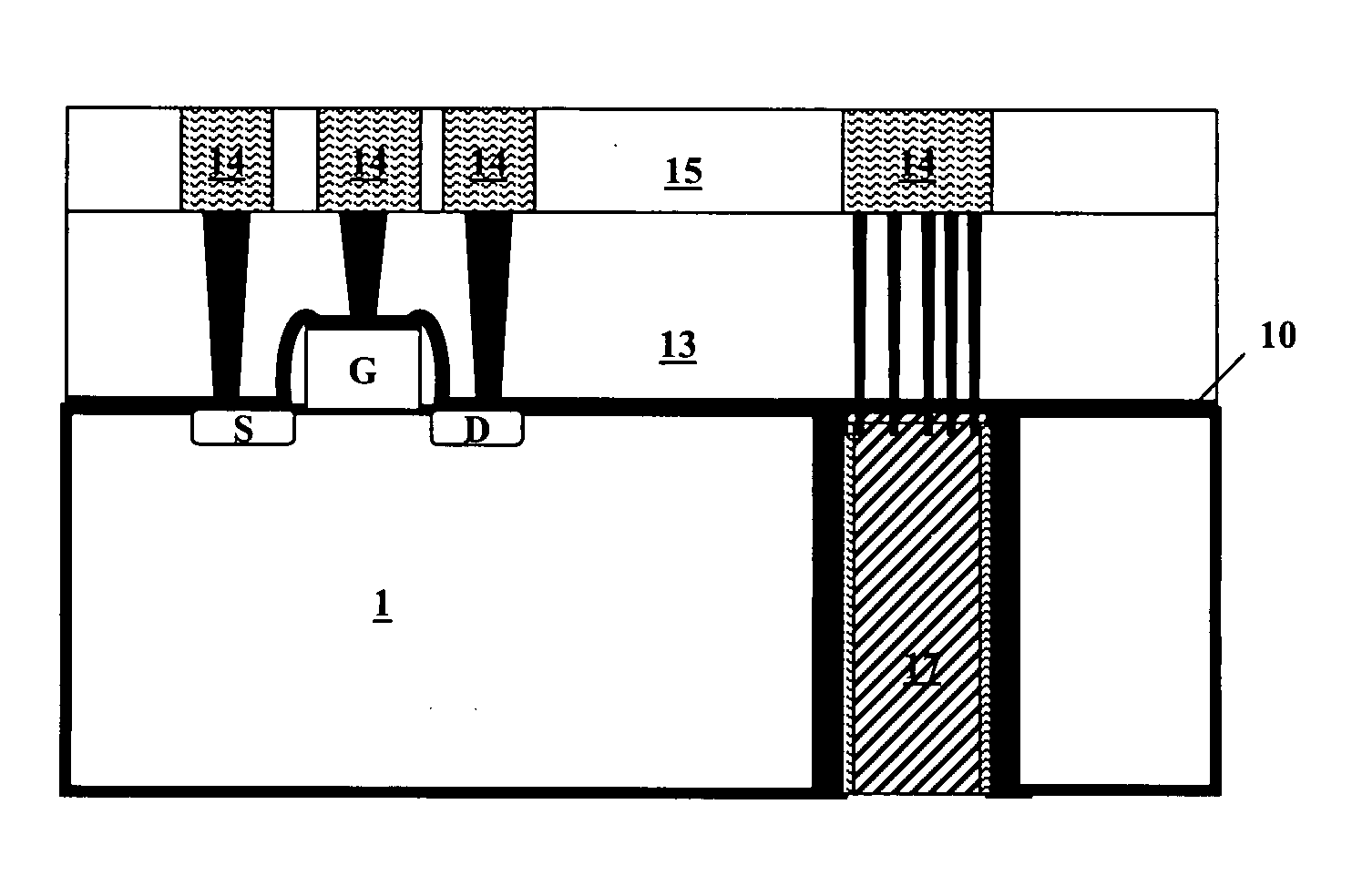

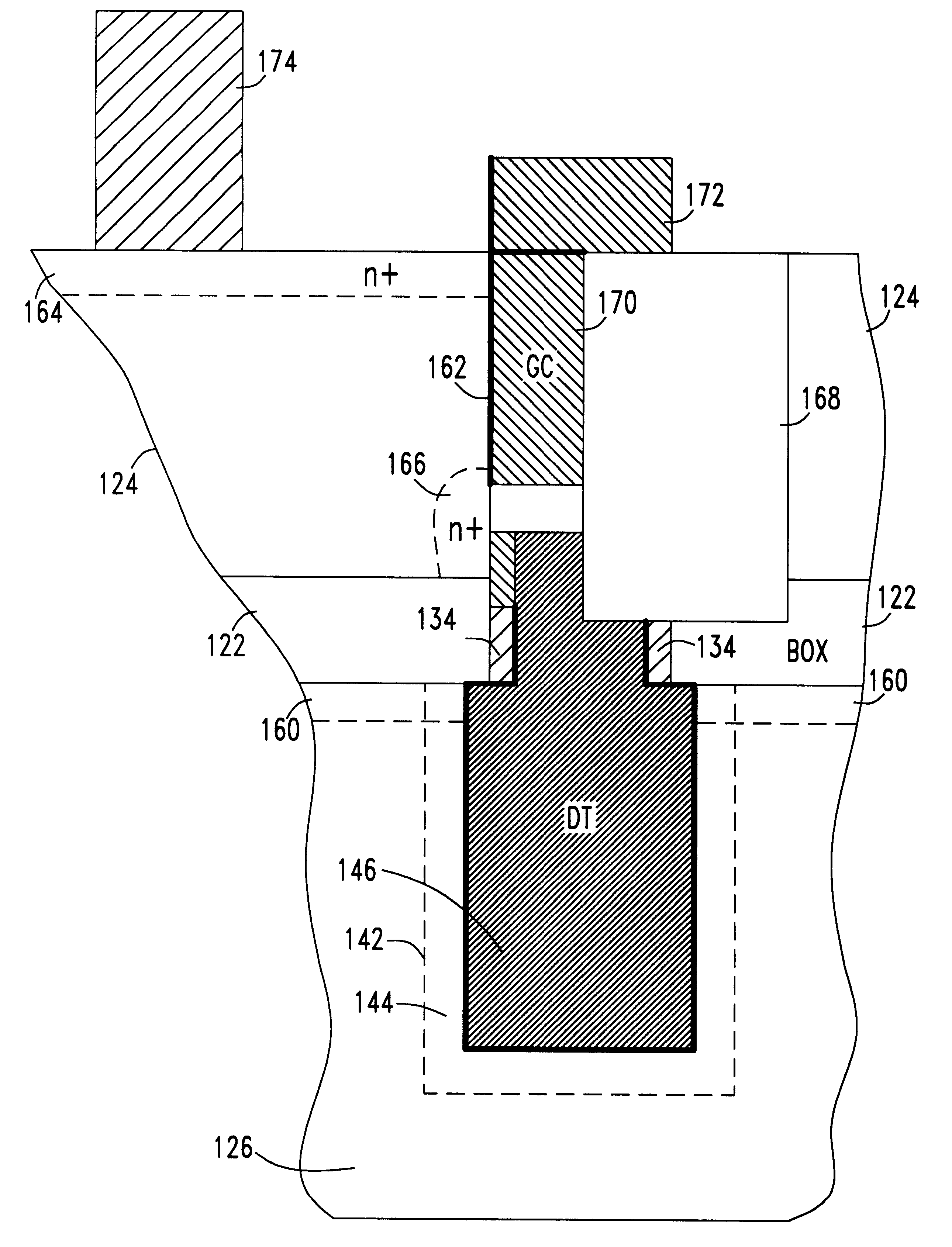

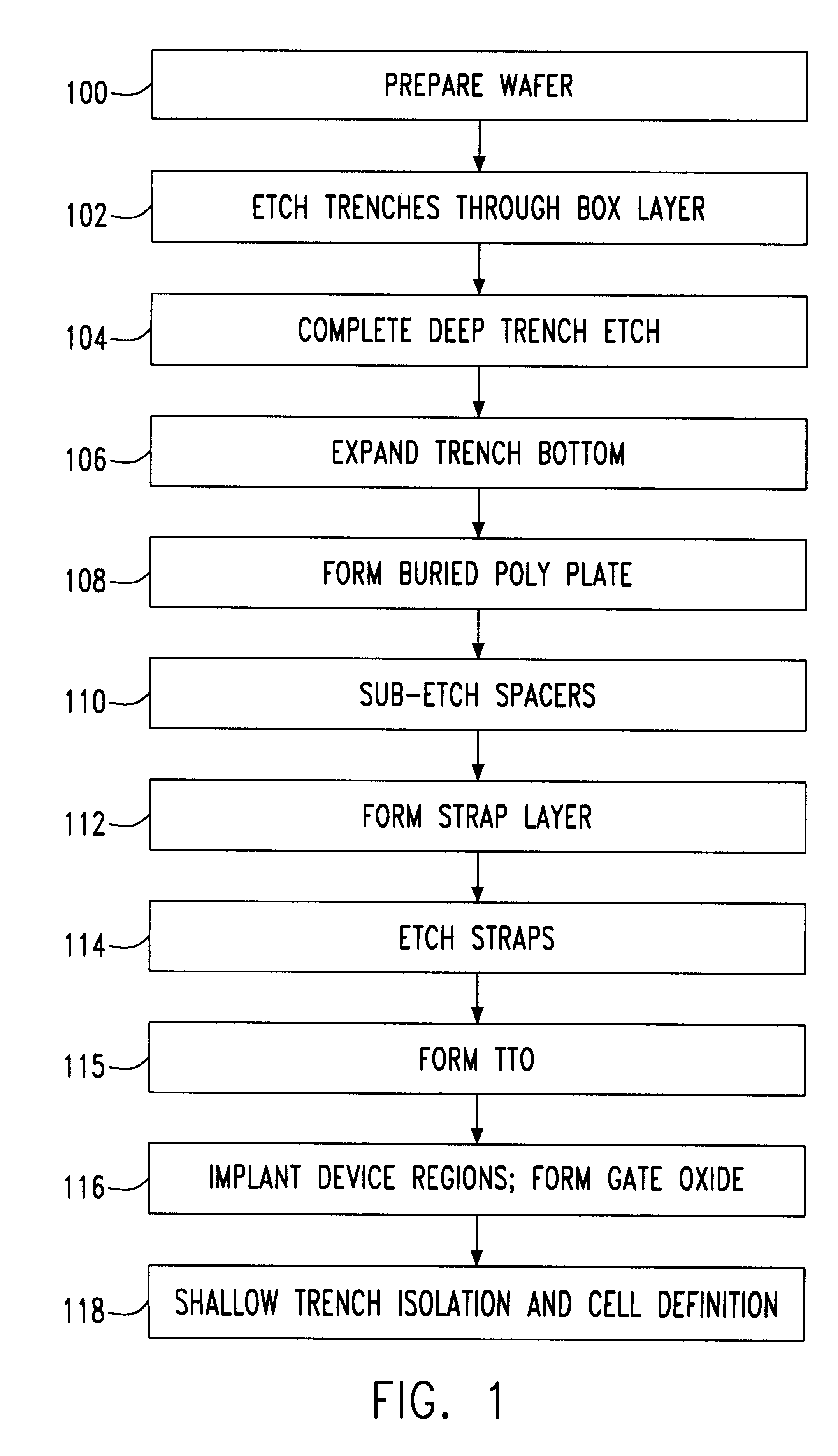

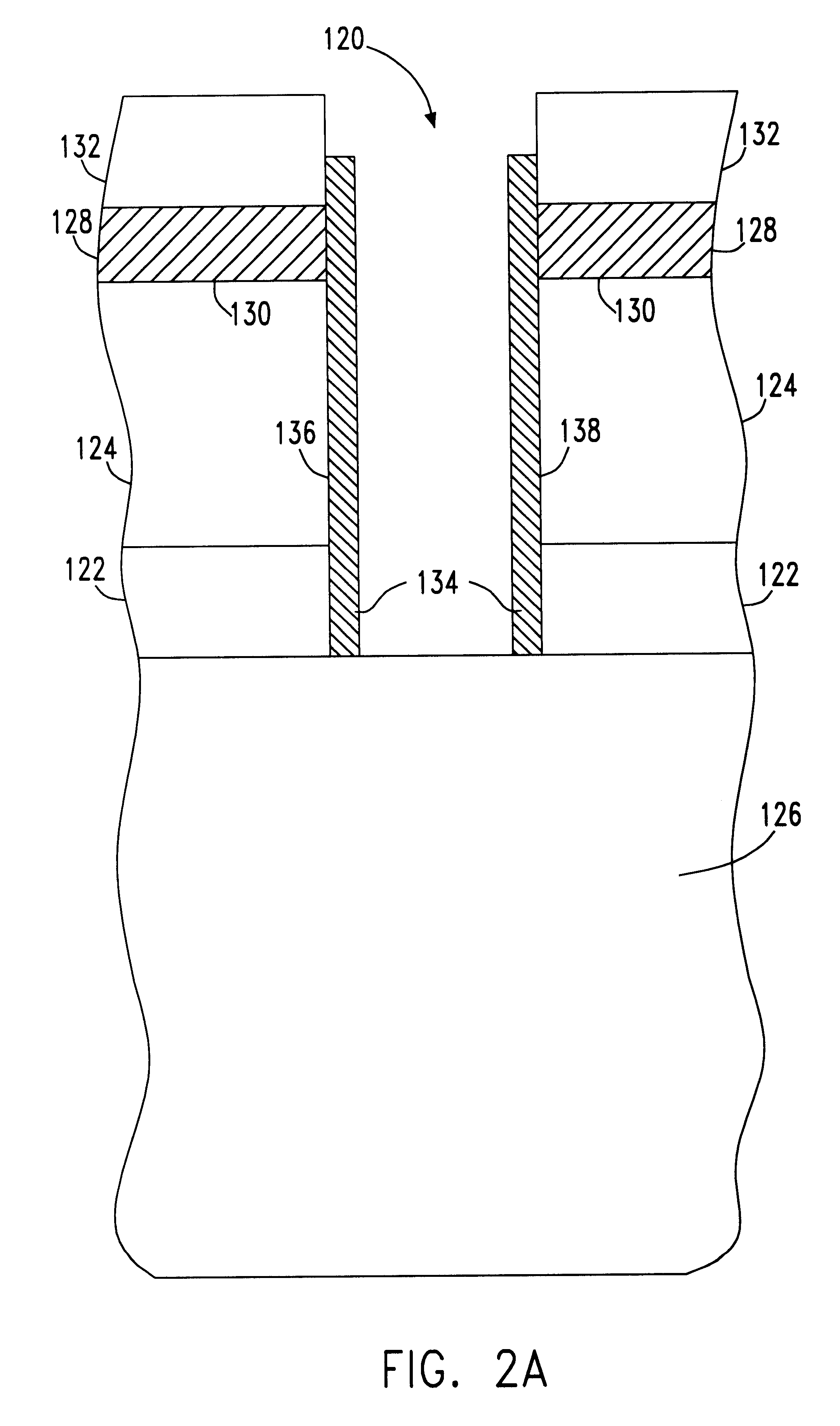

Silicon-on-insulator vertical array device trench capacitor DRAM

InactiveUS6566177B1Solid-state devicesSemiconductor/solid-state device manufacturingEngineeringBottle

A silicon on insulator (SOI) dynamic random access memory (DRAM) cell and array and method of manufacture. The memory cell includes a trench storage capacitor connected by a self aligned buried strap to a vertical access transistor. A buried oxide layer isolates an SOI layer from a silicon substrate. The trench capacitor is formed in the substrate and the access transistor is formed on a sidewall of the SOI layer. A polysilicon strap connected to the polysilicon plate of the storage capacitor provides a self-aligned contact to the source of the access transistor. Initially, the buried oxide layer is formed in the wafer. Deep trenches are etched, initially just through the SOI layer and the BOX layer. Protective sidewalls are formed in the trenches. Then, the deep trenches are etched into the substrate. The volume in the substrate is expanded to form a bottle shaped trench. A polysilicon capacitor plate is formed in the deep trenches and conductive polysilicon straps are formed in the trenches between the capacitor plates and the SOI sidewalls. Device regions are defined in the wafer and a sidewall gate is formed in the deep trenches. Shallow trenches isolation (STI) is used to isolate and define cells. Bitlines and wordlines are formed on the wafer.

Owner:GOOGLE LLC

Single-crystal silicon substrate, SOI substrate, semiconductor device, display device, and manufacturing method of semiconductor device

InactiveUS7508034B2Well formedHigh bonding strengthTransistorSolid-state devicesDisplay deviceSoi substrate

A semiconductor device of the present invention is arranged in such a manner that a MOS non-single-crystal silicon thin-film transistor including a non-single-crystal silicon thin film made of polycrystalline silicon, a MOS single-crystal silicon thin-film transistor including a single-crystal silicon thin film, and a metal wiring are provided on an insulating substrate. With this arrangement, (i) a semiconductor device in which a non-single-crystal silicon thin film and a single-crystal silicon thin-film device are formed and high-performance systems are integrated, (ii) a method of manufacturing the semiconductor device, and (iii) a single-crystal silicon substrate for forming the single-crystal silicon thin-film device of the semiconductor device are obtained.

Owner:SHARP KK

Single-electron floating-gate MOS memory

A Single Electron MOS Memory (SEMM), in which one bit of information is represented by storing only one electron, has been demonstrated at room temperature. The SEMM is a floating gate Metal-Oxide-Semiconductor (MOS) transistor in silicon with a channel width (about 10 nanometers) which is smaller than the Debye screening length of a single electron stored on the floating gate, and a nanoscale polysilicon dot (about 7 nanometers by 7 nanometers by 2 nanometers) as the floating gate which is positioned between the channel and the control gate. An electron stored on the floating gate can screen the entire channel from the potential on the control gate, and lead to: (i) a discrete shift in the threshold voltage; (ii) a staircase relation between the charging voltage and the shift; and (iii) a self-limiting charging process. The structure and fabrication of the SEMM is well adapted to the manufacture of ultra large-scale integrated circuits.

Owner:MINNESOTA RGT UNIV OF A CORP OF MN

Use of high-K dielectric material for ONO and tunnel oxide to improve floating gate flash memory coupling

InactiveUS6617639B1Enhanced couplingReduce equivalent oxide thicknessTransistorSemiconductor/solid-state device manufacturingCouplingDielectric layer

A floating gate flash memory device including a substrate comprising a source region, a drain region, and a channel region positioned therebetween; a floating gate electrode positioned above the channel region and separated from the channel region by a tunnel dielectric material layer; and a control gate electrode positioned above the floating gate electrode and separated from the floating gate electrode by an interpoly dielectric layer, the interpoly dielectric layer comprising a modified ONO structure having a bottom dielectric material layer adjacent to the floating gate electrode, a top dielectric material layer adjacent to the control gate electrode, and a center layer comprising a nitride and positioned between the bottom dielectric material layer and the top dielectric material layer, in which the tunnel dielectric material layer, and at least one of the bottom dielectric material layer and the top dielectric material layer, comprise a high-K dielectric material.

Owner:MONTEREY RES LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com